为处理器验证创建一个“瑞士奶酪模型”,以保证高效的验证品质!

所有的处理器都有着很高的品质要求,其可靠性是处理器验证团队的主要关切。提供一流质量的产品需要一个战略性的、勤勉的和彻底的方法去实现。因此,处理器验证发挥着重要作用,它需要结合所有行业标准技术--而这就有点像心理学上的的瑞士奶酪模型(又称Reason模型)原则。

我们强烈需要一个强大的、分层的处理器验证策略!

我在之前曾经说过:处理器验证是一门微妙的艺术。我们需要考虑到所有的不确定性,这意味着在优化资源的同时开放验证范围。一方面,我们要在最终交付前找到所有的关键漏洞。另一方面,我们必须有一个高效的验证策略来满足上市时间的硬性要求。交付智能处理器验证意味着在产品开发过程中尽可能有效地、尽早地找到有意义的bug。实现这一目标的方法之一是结合所有行业标准的验证技术。而正是通过创建冗余,最终找到并击败所有关键bug。

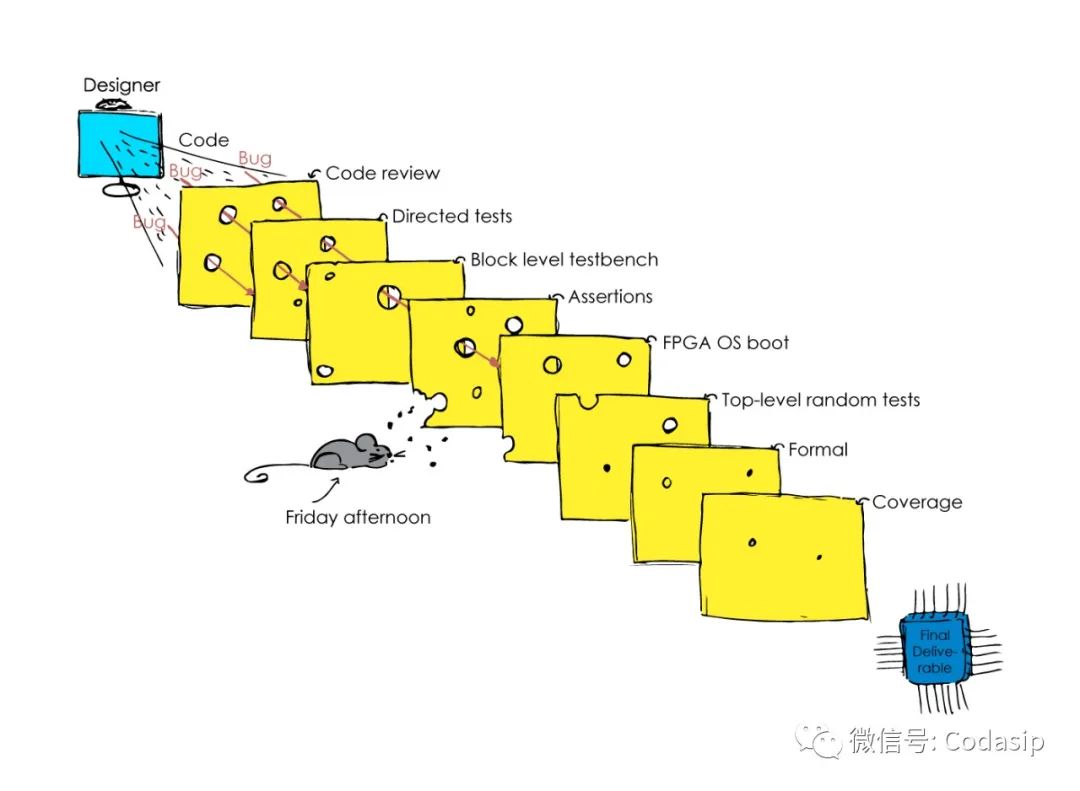

不同类型的bug都有一个复杂性--或bug评分--这取决于触发bug所需的事件数量和类型。有些可能是用覆盖率发现的,而有些是用形式证明发现的。想象一下,如果将”瑞士奶酪模型”应用于处理器验证。每一片奶酪都象征着一种验证技术,它有一些特定的优势来捕捉特定类型的bug。漏洞逃脱并进入最终交付物的风险通过不同层次和类型的验证来减轻,而这些验证是相互分层的。

在应用于处理器验证的瑞士奶酪模型中,其原理类似于航空业:如果有一条直接穿过所有切片的路径,那么飞机就有坠毁的风险。这就是为什么航空业对程序、飞行检查单和冗余系统要求严格?我们的目标是增加更多的切片,减少每一个切片上的孔的大小,直至最后没有任何缝隙可以穿过,此时一个高质量的处理器正式完成。

应用于处理器验证的瑞士奶酪模型原则

通过验证方法(以瑞士奶酪模型为例):

首先需要创建冗余,以确保在其中一个layer上失败时的连续性。

当在开发过程中发现bug时,表明漏洞出现在了其中的几片奶酪上。因此,我们可以改进几种验证方法,以减少每片奶酪上的漏洞大小。利用这种方法,无论是简易简单的漏洞还是复杂的终极漏洞,都可以增加击中bug的几率。

最大限度地发挥每种验证技术的潜力。

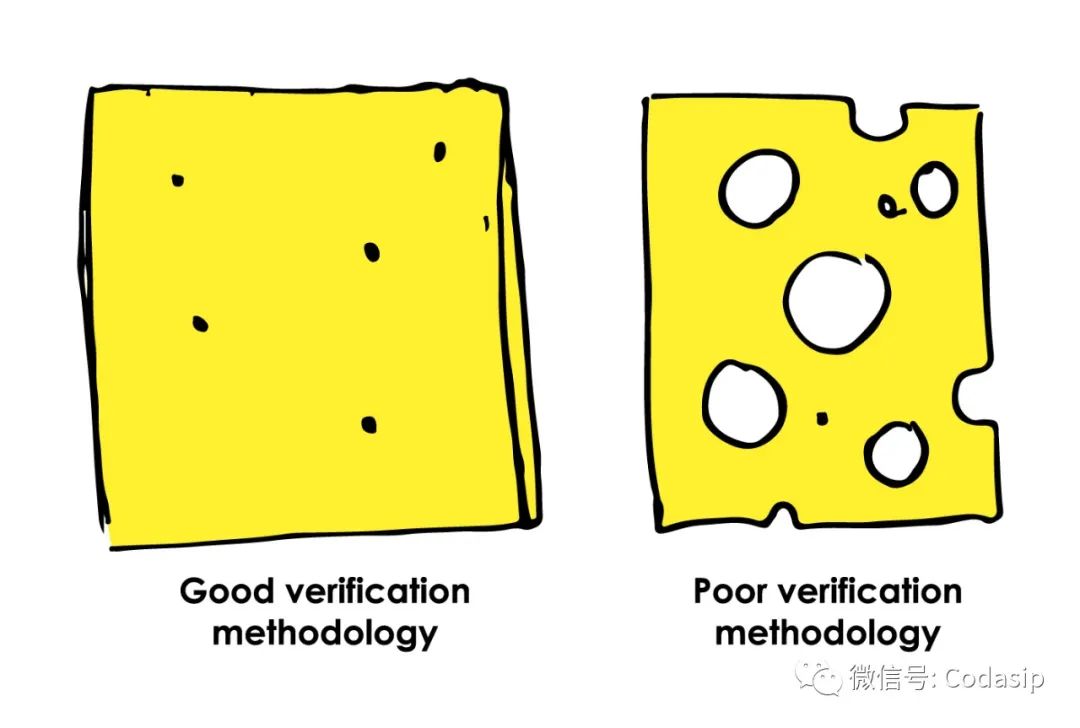

每个分片上的孔就是验证方法中的一个洞。孔越多越大,意味着越多的bug可以逃脱。如果设计的同一区域(奶酪片之间的重叠孔)中没有被任何一种验证技术所覆盖和测试,那么这个漏洞就会通过验证,并最终出现在交付产品中。

一种好的验证方法必须在每个切片上呈现尽可能少和小的孔。而这就要求验证团队有着扎实的策略、经验和高效的沟通,这些品质也是交付高质量产品的重要因素。

在验证过程中,当我们发现一个bug,或者一个切片上的孔时,及时修复并检查其他切片是否有类似的漏洞。每一个切片都应该找到前一个切片中的漏洞,并在继续运行之前解决掉它们。而实现这一目标的有效方式是全面健全性检查!

在应用于处理器验证的瑞士奶酪模型原则中,如果一种技术有改进的测试平台、新的断言等功能加持,那么在产品交付之前,该漏洞就会被及时发现和修复。所有的处理器验证技术都很重要,正是所有技术的结合才能使每种技术更有效率。

同时我们需要意识到一个单一的验证技术不可能完成所有的事情,是所有技术的综合提高了验证和处理器设计的整体质量。在产品的开发过程中,可能会有意想不到的变化或因素,这些外部行为会影响某种技术的效率。例如,设计中的变化没有很好的传达给验证团队,或者出小差的周五下午的工作效率导致了人为错误。这些因素都会增加切片上孔的大小,因此保持项目规范的及时更新以及设计者和验证工程师之间有效的定期沟通极其重要。此外在Codasip,实现这一目标的另一个有效解决方案是执行由其他团队成员进行的代码审查。

Codasip使用的验证技术和技巧,使我们能够创建冗余,及时发现和修复漏洞并最终提供一流品质的RISC-V处理器!

审核编辑 :李倩

-

处理器

+关注

关注

68文章

20339浏览量

255356 -

验证技术

+关注

关注

0文章

6浏览量

6379

原文标题:处理器验证系列之五:为处理器验证创建一个“瑞士奶酪模型”,以保证高效的验证品质!

文章出处:【微信号:Codasip 科达希普,微信公众号:Codasip 科达希普】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

RDMA设计36:验证环境设计

RDMA设计35:基于 SV 的验证平台

Andes晶心科技推出全新32位RISC-V处理器D23-SE

利用事务级加速实现高速、高质量的RISC-V验证

NVMe高速传输之摆脱XDMA设计24: UVM 验证包设计

NVMe高速传输之摆脱XDMA设计23:UVM验证平台

NVMe高速传输之摆脱XDMA设计18:UVM验证平台

绿氢系统 PEM 电解槽直流接入仿真验证深度解析

Veloce Primo补全完整的SoC验证环境

硬件辅助验证(HAV) 对软件验证的价值

筑牢汽车品质基石:深入剖析 DV 与 PV 验证

为处理器验证创建一个“瑞士奶酪模型”,以保证高效的验证品质!

为处理器验证创建一个“瑞士奶酪模型”,以保证高效的验证品质!

评论