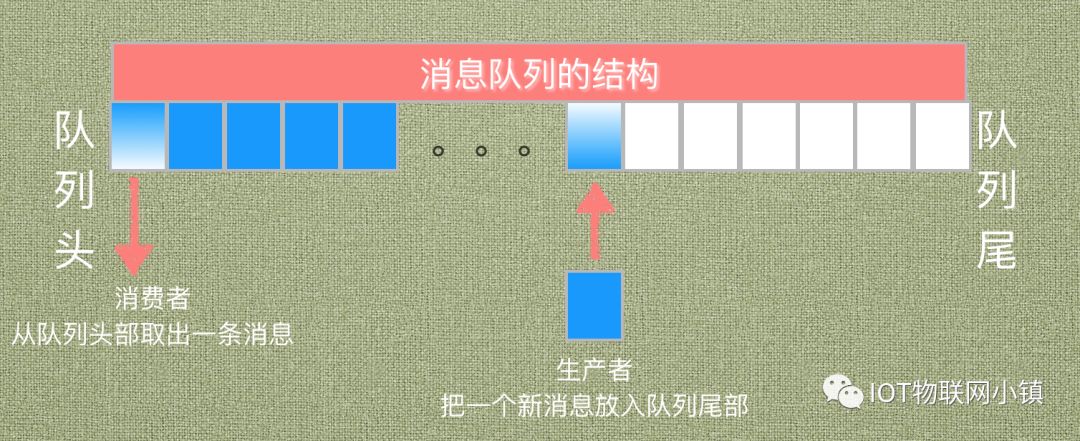

队列是大小可变的有序集合,队列中元素必须是同一个类型的。队列支持对其所有元素的访问以及在队列的开始或结束处插入和删除。

第0个位置表示第一个元素,第$个位置表示队列的最后一个元素。

队列也是一个一维unpacked数组。队列可用于建模后进先出(LIFO)或先进先出(FIFO) buffer。

data_type queue_name [$ :];

下面是队列的示例

module dq; // A queue of 8-bit bytes – unbounded queue bit[7:0] dq1[$]; // A queue of strings – unbounded queue string mname[$] = { "Bob" }; // An initialized queue – unbounded queue bit[15:0] dq2[$] = { 3, 2, 7, 1 }; // A bounded queue – size = 256. Maximum index @255. bit q2[$:255]; //bit q2[255:$]; // Compile ERROR – invalid syntax int dq2_size; initial begin dq1[0] = 'hff; dq1[1] = 'h00; dq1[$] = 'h01; //last entry - will override dq1[1]='h00 $display($stime,,,"dq1=",dq1); dq1[1] = 'h02; $display($stime,,,"dq1=", dq1); mname[1] = "mike"; //push-in - grow the queue $display($stime,,, "mname=", mname); //displays initialized 4 entries $display($stime,,,"dq2=", dq2); dq2[4] = {16'h 1111}; $display($stime,,,"dq2=", dq2); q2[0] = 1; q2[1] = 0; $display($stime,,, "q2=",q2); q2[3] = 1; //skipped entry '2' - so no 3rd entry $display($stime,,, "q2=",q2); dq2_size = dq2.size( ); $display($stime,,,"dq2 size = %0d",dq2_size); for (int i = 0; i < dq2_size; i++) //read the entire queue $display($stime,,,"dq2[%0d] = %0h", i, dq2[i]); //insert a value at index 256 which is out of bound //dq2.insert(256,1); //You get a run-time Error end endmodule

上面的例子中声明了两种类型的队列:有界队列和

无界队列。

有界队列:

“q2[$:255];”有界的意思是最大下标

队列是有界的。在本例中,最大索引是255,这意味着它可以存储的元素是256(0到255)。如果你想在index 256插入元素,就会出现溢出,数据就会丢失。

无界队列为:

bit[7:0] dq1[$]; // A queue of 8-bit bytes – unbounded queue

string mname[$] = { "Bob" }; // A queue of strings – unbounded queue

bit[15:0] dq2[$] = { 3, 2, 7, 1 }; // An initialized queue – unbounded queue

无界队列的大小没有上限。

仿真log:

0 dq1='{'hff, 'h1}

0 dq1='{'hff, 'h2}

0 mname='{"Bob", "mike"}

0 dq2='{'h3, 'h2, 'h7, 'h1}

0 dq2='{'h3, 'h2, 'h7, 'h1, 'h1111}

0 q2='{'h1, 'h0}

0 q2='{'h1, 'h0}

0 dq2 size = 5

0 dq2[0] = 3

0 dq2[1] = 2

0 dq2[2] = 7

0 dq2[3] = 1

0 dq2[4] = 1111

V C S S i m u l a t i o n R e p o r t

将值'ff'和'00" 赋给dq1的前两个元素(dq1[0]和dq1[1])。之后,赋值最后一个条目(dq1[$])为'h01。此时dq1[1]就是'h01。最后在赋值dq1[1]为'h02,实际打印:

0 dq1='{'hff, 'h1}

0 dq1='{'hff, 'h2}

push一个新值“mike”到队列“mname”

0 mname='{"Bob", "mike"}

打印初始化的队列dq2,然后push一个值16'h1111

0 dq2='{'h3, 'h2, 'h7, 'h1}

0 dq2='{'h3, 'h2, 'h7, 'h1, 'h1111}

然后,赋值q2[0] = 1, q2[1] = 0。

0 q2='{'h1, 'h0}

赋值q2[3] = 1。但请注意,由于这个时候q2[2]还不存在,所以会忽略或者报错。

0 q2='{'h1, 'h0}

然后,读取整个队列dq2。首先得到队列的大小并将其存储在dq2_size中,遍历整个队列并显示每个元素。

0 dq2 size = 5 0 dq2[0] = 3 0 dq2[1] = 2 0 dq2[2] = 7 0 dq2[3] = 1 0 dq2[4] = 1111

最后,在索引256处插入一个值

dq2.insert(256);

由于" dq2 "是一个最大下标为255的有界数组,试图插入索引为256的值会报错:

Error-[DT-MCWII] Method called with invalid index testbench.sv, 45 "insert" method called with invalid index (index:256) Please make sure that the index is positive and less than size.

审核编辑:汤梓红

-

Verilog

+关注

关注

31文章

1374浏览量

114723 -

System

+关注

关注

0文章

166浏览量

38829 -

队列

+关注

关注

1文章

46浏览量

11254

原文标题:SystemVerilog中的队列

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

SystemVerilog中的“const”类属性

SystemVerilog的断言手册

SystemVerilog中$cast的应用

SystemVerilog中的Queue Methods

SystemVerilog中的package

SystemVerilog中的Semaphores

Systemverilog中的Driving Strength讲解

SystemVerilog中的队列

SystemVerilog中的队列

评论