在systemverilog中,net用于对电路中连线进行建模,driving strength(驱动强度)可以让net变量值的建模更加精确。net变量拥有4态逻辑值(0,1,z,x),它的driving strength有(supply,strong,pull,weak,highz)。net的值由连接到net的driver源(驱动源)决定的,这些driver源可以是连续赋值语句(例如assign),也可以是门级建模原语(例如门级or或and或cmos等)。

在每个Δ仿真周期中,仿真器通过查看net上所有驱动源的逻辑值(logical value)和强度值(strength level)来决定该net的逻辑值和强度值。如果net没有驱动源,那么它的值将是’z’态。如果net只有1个驱动源,那么它的逻辑值和强度值等于驱动源的值和强度。但是,如果net有多个驱动源,那么需要比较它们的强度值了,强度最大的驱动源将成功驱动net。不过如果有多个强度最大的驱动源,但它们的逻辑值不一样的话,net的逻辑值将会是’x’态,强度值是最强的strength。

需要注意的是driving strength是用于gate输出和连续赋值语句输出的(assign)。对于非net类型的多驱动,仿真工具会报多驱的编译错误。

Systemverilog的driving strength level(驱动强度)有以下几种:

上述strength level可以归为3类:

- Driving strength:supply,strong,pull和weak

- Charge storage strength:large,medium和small

- High impedance:highz

Charge storage strength只用于trireg类型的net。

Driving strength的语法如下:

drive_strength ::=

( strength0 , strength1 )

| ( strength1 , strength0 )

| ( strength0 , highz1 )

| ( strength1 , highz0 )

| ( highz0 , strength1 )

| ( highz1 , strength0 )

strength0 ::= supply0 | strong0 | pull0 | weak0

strength1 ::= supply1 | strong1 | pull1 | weak1

charge_strength ::= ( small ) | ( medium ) | ( large )

strength0表示当驱动源驱动net为0时的驱动强度。Strength1表示当驱动源驱动net为1时的驱动强度。

net默认的strength level是(strong0, strong1)。对于pullup和pulldown gate,默认的strength level是pull。trireg默认的strength level是medium。Supply net的默认strength level是supply。另外从上面syntax看出,(highz1, highz0)和(highz0, highz1)的strength level组合是非法的。

结合上面的理论讲解,给出1个例子如下:

module strength;

logic i1, i2;

wire logic out;

assign (supply1, weak0) out = i1;

assign (pull1, supply0) out = i2;

initial begin

i1 = 1'b0;

i2 = 1'b0;

$strobe("[time:%0t],i1:%b, i2:%b, out:%b, out_strength:%v", $time, i1, i2, out, out);

#1ns;

i1 = 1'b0;

i2 = 1'b1;

$strobe("[time:%0t],i1:%b, i2:%b, out:%b, out_strength:%v", $time, i1, i2, out, out);

#1ns;

i1 = 1'b1;

i2 = 1'b0;

$strobe("[time:%0t],i1:%b, i2:%b, out:%b, out_strength:%v", $time, i1, i2, out, out);

#1ns;

i1 = 1'b1;

i2 = 1'b1;

$strobe("[time:%0t],i1:%b, i2:%b, out:%b, out_strength:%v", $time, i1, i2, out, out);

end

endmodule

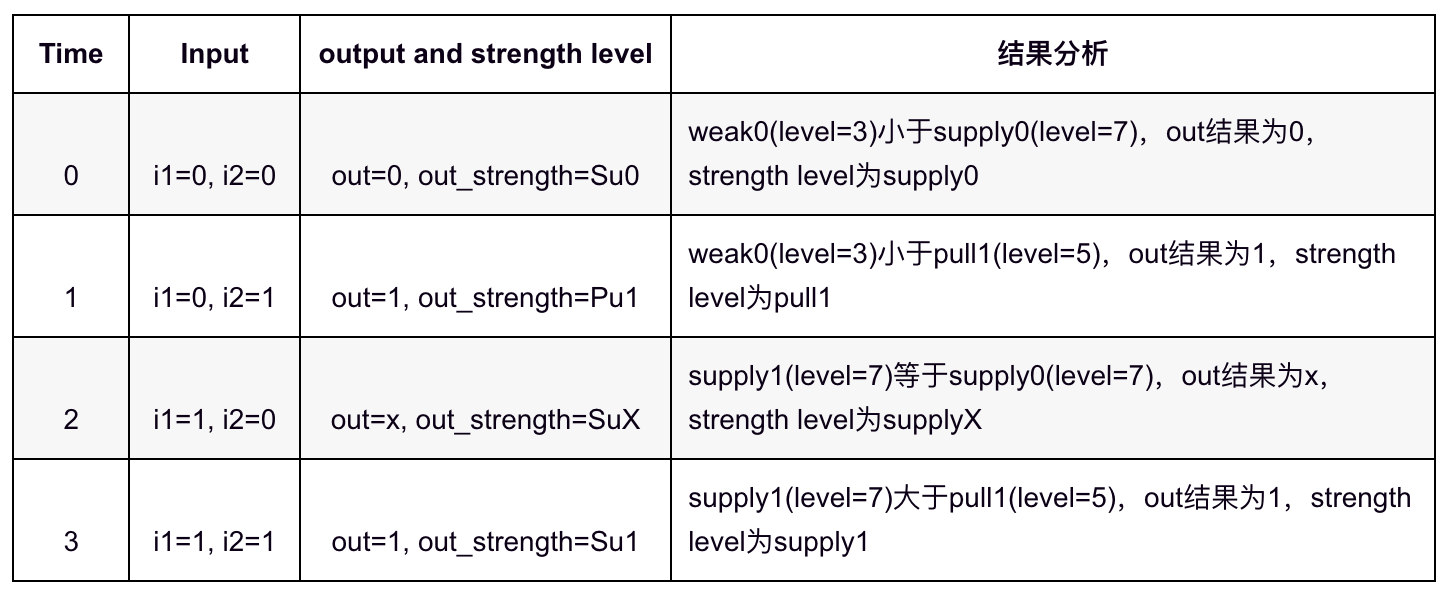

使用Questasim仿真输出的log结果为:

# [time:0],i1=0, i2=0, out=0, out_strength=Su0

# [time:1],i1=0, i2=1, out=1, out_strength=Pu1

# [time:2],i1=1, i2=0, out=x, out_strength=SuX

# [time:3],i1=1, i2=1, out=1, out_strength=Su1

"assign (supply1, weak0) out = i1"行给net类型的out驱动i1的值,其中strength1为supply1(level=7),strength0为weak0(level=3)。12行给net类型的out驱动i2的值,其中strength1为pull1(level=5),strength为supply0(level=7)。

" assign (pull1, supply0) out = i2"行给net类型的out驱动i2的值,其中strength1为pull1(level=5),strength为supply0(level=7)。

Driving strength还有很多其它的组合,大家可以复制上述代码,并修改assign out语句的strength0与strength1去产生其它的组合并分析结果。

另外,大家可能好奇如何打印出net变量的strength level?在systemverilog中提供了%v格式化打印。%v的输出是3个字符的string类型,前2个字符指示strength类型,第三个字符指示当前逻辑值。比如上述log中的Su0或Pu1或SuX或Su1。

-

驱动器

+关注

关注

54文章

9115浏览量

156508 -

仿真器

+关注

关注

14文章

1052浏览量

88196 -

Verilog语言

+关注

关注

0文章

113浏览量

8827

发布评论请先 登录

Systemverilog中的Driving Strength讲解

Systemverilog中的Driving Strength讲解

评论