提到阻抗其实很多人可能都不会计算,因为涉及到很多参数,如:半固化片PP厚度,铜的厚度,如果是隔层参考还要计算芯板加PP厚度,接下来就会讲解到详细的阻抗。

做阻抗的目的是什么?

印刷电路板提供的电路性能必须能够使信号传输过程中不发生反射现象,信号保持完整,降低传输损耗,起到匹配阻抗的作用,这样才能得到完整、可靠、精确,无干扰、噪音的传输信号。

对我们而言,就是除了要保证PCB板的短、断路合格外,还要保证阻抗值在规定的范围内,只有这两方向都合格了印刷板才符合客户的要求

阻抗的影响因素

★ 线宽(W)

由底片的设计值,制程的蚀铜能力决定

★ 线路铜厚(T)

由原物料的选择和镀铜能力决定(外层阻抗)

★ 介电层厚度(H)

PP的种类,残铜率,压合程式等

★ 介电常数(er)

(包括基板,PP)由原物料决定

★ 阻焊厚度(C)

由制程能力决定(包括下墨量,刮刀速度,刮刀角度,外层铜厚)

绿漆介电常数(er)

(包括基板,PP)

★ 介电常数的定义

电容器两极板间充满电介质时的电容和两极板间为真空时的电容之比叫做电介质的介电常数,用er表示。它是表征材料电性能的一个物理量。

材料的介电常数是材料的生产厂家在频率为1MHz下测量确定的,是随着频率的增加而减小,TDR测试频率为900MHz。

PP和基板的介电常数一般为3.8-4.5,而PP和基板都是由玻纤布和树脂组成,玻纤布的介电常数为6.0,树脂的介电常数为3.8,因此不同胶含量的PP,其介电常数一般来说是不同的。

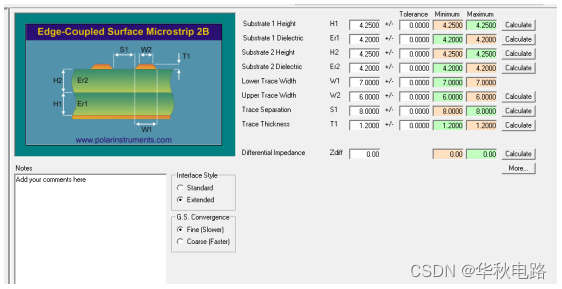

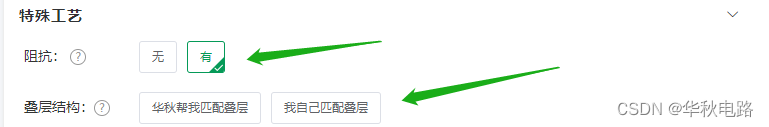

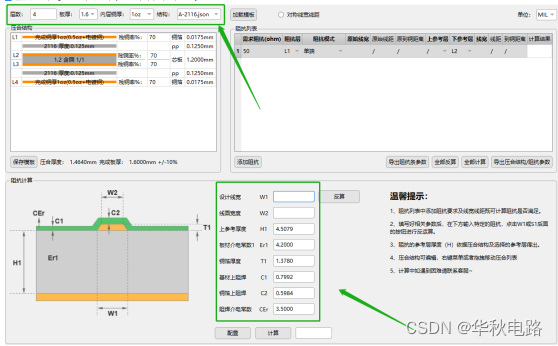

第一种:传统阻抗设计软件

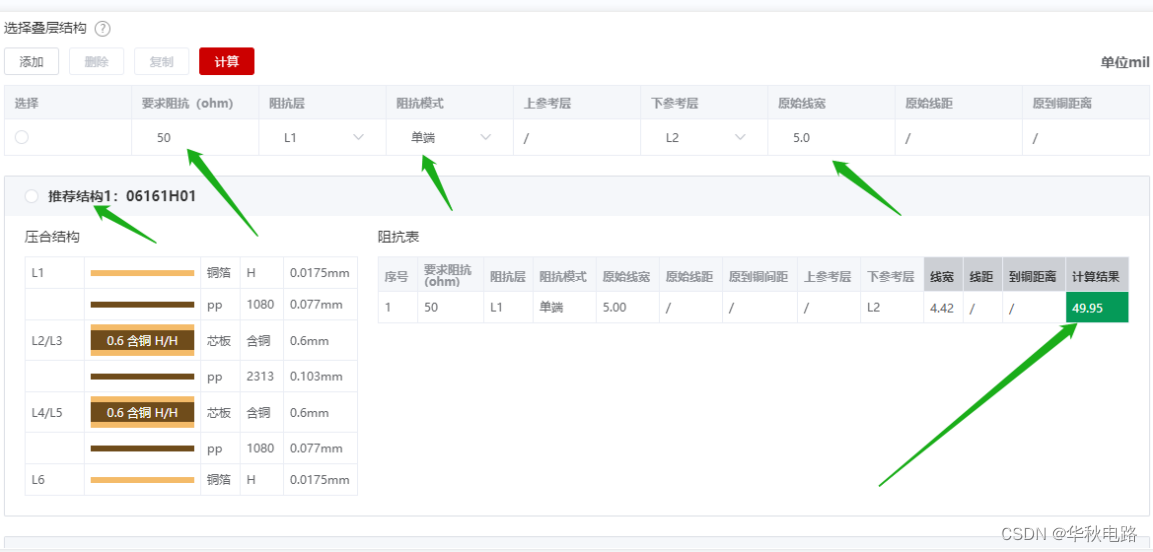

第二种:阻抗神器:

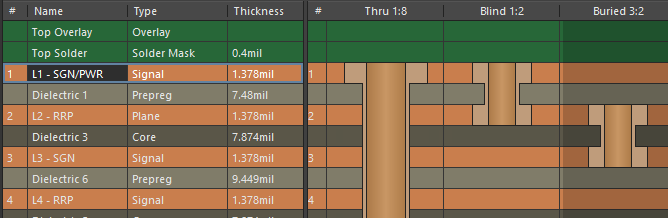

如上图所示,只输入阻抗值和线宽,就会出现阻抗值,下面就会多种叠层推荐。

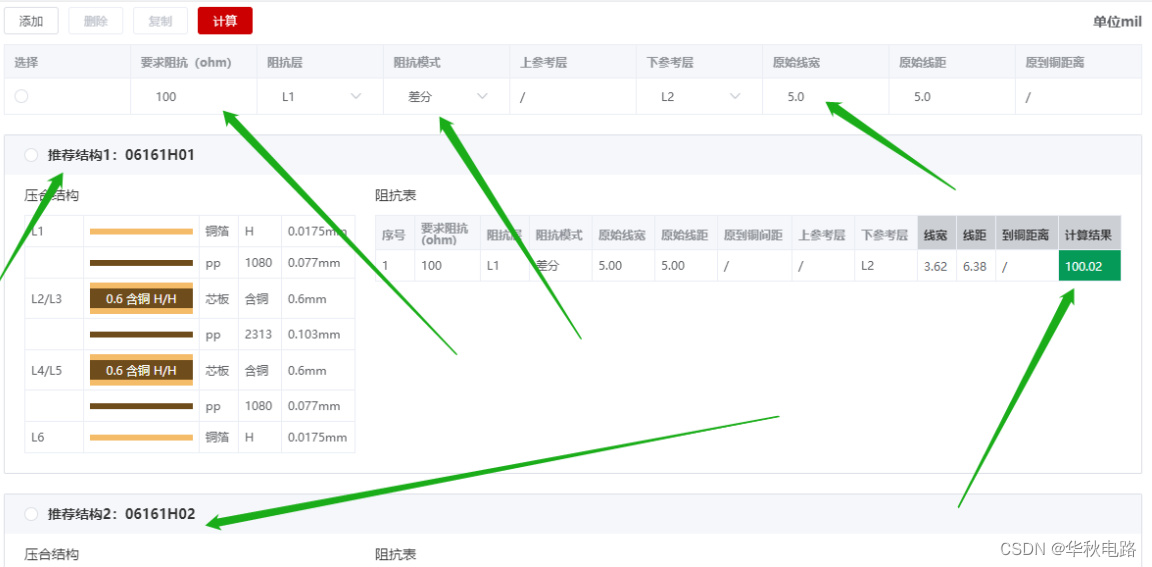

(1)差分阻抗计算

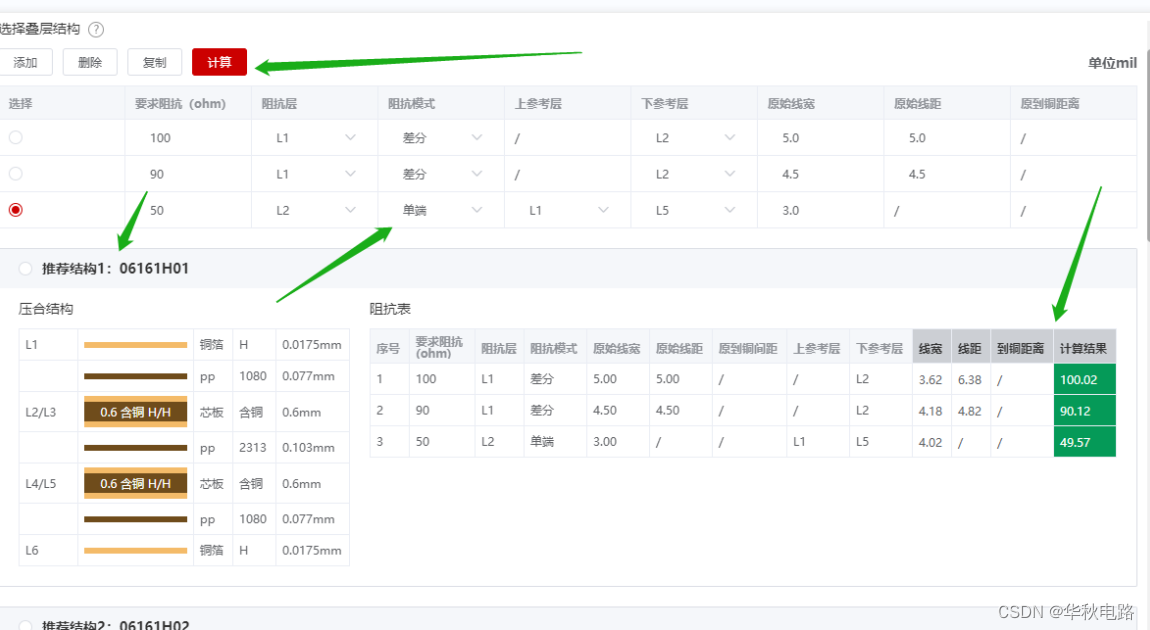

(2)多组阻抗计算

上述工具地址:https://www.hqpcb.com

上述工具地址:https://dfm.elecfans.com/uploads/software/promoter/hqdfm_dzfsy_hdzwz.zip

审核编辑 黄昊宇

-

pcb

+关注

关注

4417文章

23962浏览量

426105 -

阻抗

+关注

关注

17文章

993浏览量

49495 -

PCB设计

+关注

关注

396文章

4938浏览量

95743

发布评论请先 登录

叠层固态电容的性能优势

贴片电感代理-叠层电感的实际应用

PCB叠层设计避坑指南

PCB叠层设计避坑指南

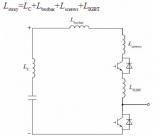

叠层母排在IGBT变流器中的应用(2)

Allegro Skill布线功能之调整差分的线宽线距

Allegro Skill布线功能之改变线宽介绍

输入线宽,就可以得到阻抗值,还能匹配叠层的神器你用过吗?

输入线宽,就可以得到阻抗值,还能匹配叠层的神器你用过吗?

评论