随着物联网市场的不断扩大,对抗性攻击的破坏性也在不断扩大。连接应用程序的安全性现在是其设计的基本要素。连接的设备必须能够相互进行身份验证,确保安全的数据传输,并包括安全存储。虽然RISC-V的安全指南仍在开发中,但为RISC-V用户提供有效的即插即用解决方案以增强SoC及其他产品的安全性至关重要。

需要什么样的设计来保护物联网应用?

在大多数情况下,有六个关键的 SoC 安全因素需要考虑。..

受信任的执行环境 (TEE):隔离需要更高安全级别的代码、数据和内存。

信任根:保护关键安全参数;包含唯一 ID、证书、密钥和安全存储。

安全启动:阻止未经授权的操作系统和应用程序运行。

静态数据安全性:以加密/模糊的形式存储数据,并具有可靠的访问控制,以防止泄漏。

传输中数据安全:利用密钥在传输前对数据进行加密,以防止被拦截。

安全 OTA 更新:确保现场的固件或软件更新以加密密文的形式提供,并且不允许降级。

仅拥有CPU无法实现这六个安全因素。芯片的设计需要一个密钥存储单元和一组加密算法来帮助CPU执行安全功能,包括身份验证、加密、解密和完整性检查,以实现这些功能。此外,安全操作(与非安全操作分开)需要隔离且受信任的安全执行环境。还应实施防篡改设计,以保护安全环境免受攻击。

考虑到这些风险,经验丰富的设计人员通常会使用带有硬件信任根和防篡改设计的安全协处理器来支持CPU执行应用程序和服务的所有必要安全功能。

纠正现有协处理器的不足

安全协处理器负责系统内与安全相关的事务,并允许CPU安全地执行其主要功能。实施后,硬件加速的安全协处理器将保护敏感信息并比CPU更有效地执行安全功能,而不会窃取其计算能力。这不仅简化了系统设计,还提高了整体性能。

在其架构中,ARM提供与其CPU集成的加密单元-312作为安全协处理器来处理安全操作。相比之下,RISC-V生态系统仍在成熟,还没有适合安全协处理器的解决方案。RISC-V用户必须自己开发或采用合作伙伴的IP才能获得上述安全功能。如果他们选择在内部开发,可能会出现一些挑战。他们是否有足够能力的安全开发团队?它将如何影响上市时间?自主研发的安全功能能否获得认证?当技术问题出现时,他们能处理得有多好?最后,成本是多少?所有这些挑战都可以通过采用来自有能力的合作伙伴的集成IP来避免。

现有解决方案缺乏全面的硬件信任根,无法提供可靠的安全边界,使其容易受到攻击。市场上的大多数安全协处理器可能涵盖一到两个关键功能,但不足。例如,一些协处理器无法支持某些加密算法,容易受到攻击,或者没有通过第三方认证。有些没有安全存储密钥,导致协处理器从安全边界之外检索密钥(想象一下,将密钥留给前门的保险库)。即使是包括安全密钥存储在内的选项也有不可避免的缺点,需要在生产过程中逐个将密钥注入芯片,这使得制造或操作成本高昂且难以操作。某些协处理器对所有产品具有相同的激活密钥,从而危及身份和应用服务管理。

所有这些不足可能最终成为物联网设备中的漏洞,这将不可避免地成为希望破坏网络的黑客的目标。因此,即使是一个只传输非敏感数据的微型物联网设备,如果被黑客操纵,也会造成巨大的伤害。像这样的事件不胜枚举,最近的一次是2021年5月,当时最大的石油管道系统殖民地管道受到攻击。他们不仅关闭了整个管道,政府甚至还发布了区域紧急声明。仅支付的赎金损失就为420万美元。

普菲奥特为RISC-V架构提供片上安全保障

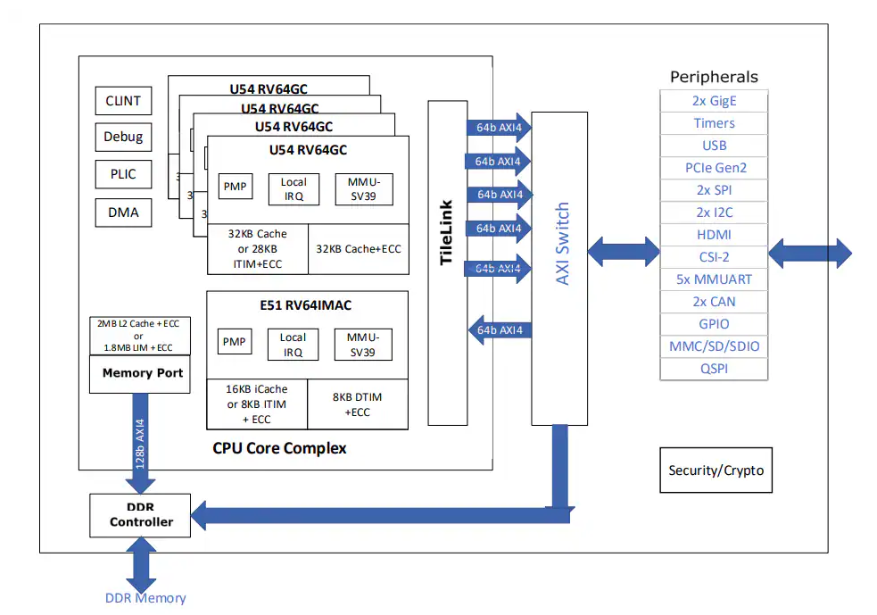

为了解决RISC-V生态系统中缺乏完整的安全协处理器的问题,PUFiot是PUF安全的集成IP解决方案之一,是最终的答案。它采用多层设计,利用一套全面的完全集成的硬件安全IP。与纯粹基于软件的设计不同,PUFiot的安全边界基于硬件的物理分离,因此建立了一个健全的可信执行环境(TEE)。图 1 演示了 PUFiot 的设计架构。PUFiot 的核心是模拟硬件信任根设计。硬件信任根包含 eMemory 的专利 NeoPUF,为每个芯片提供唯一的芯片指纹 (UID),并提供 Riscure 认证的防篡改安全 OTP,用于密钥存储,防止对关键安全参数的物理/电气攻击。硬件信任根还附带一个真随机数生成器(TRNG),这是一个动态熵的来源,用于保护加密引擎和系统之间的通信。

图1:普菲奥特的设计架构

PUFiot支持一套完整的NIST CAVP认证和第三方认证的中国OSCCA硬件加密算法。由于模块化设计,PUFiot加密算法的定制仍然很灵活。这意味着用户的要求,例如在SM4和AES之间进行选择,可以在一个简单的过程中得到满足。因此,PUFiot可以满足RISC-V当前和未来的安全要求。除了安全功能外,众多的数字和模拟防篡改设计进一步加强了PUFiot,使其成为可靠的安全协处理器。同样,为了降低整个 SoC 系统设计的复杂性,PUFiot 支持用于寄存器访问控制的标准 APB 控制接口和具有标准 AXI4 控制接口的 DMA,以快速访问存储在系统存储器中的大量数据。随附的软件开发工具包 (SDK),包括 Linux 裸机固件和高级 API,可帮助加快软件开发和部署。

除了 NIST 标准的密钥包装 (KWP) 和密钥派生函数 (KDF) 以保护密钥的使用和导出外,PUFiot 还可以按需生成多个密钥,以便 RISC-V 物理内存保护 (PMP) 单独保护每个应用程序。此外,PUF的属性非常适合安全启动和安全OTA更新,因为不同物联网设备上的相同软件都有其密钥。因此,我们可以为即将进入市场的数十亿新物联网设备建立牢固的安全基础。

结论

为了保护物联网应用,PUFsecurity利用芯片指纹技术来加强信任根,并开发了PUFiot,这是一种具有广泛安全边界的安全协处理器,可以轻松集成到安全的RISC-V系统中。PUFiot 支持物联网世界所需的零接触部署。凭借硬件加速的安全功能和访问控制,PUFiot还满足了云应用中零信任安全的要求。因此,PUFiot作为一种安全解决方案,非常适合采用RISC-V处理器的物联网设备。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

20325浏览量

254692 -

soc

+关注

关注

40文章

4619浏览量

230079 -

RISC-V

+关注

关注

49文章

2941浏览量

53519

发布评论请先 登录

新思科技ImperasDV解决方案让RISC-V处理器验证效率翻倍

Andes晶心科技推出全新32位RISC-V处理器D23-SE

直播预约 |开源芯片系列讲座第30期:“一生一芯”计划——从零开始设计自己的RISC-V处理器芯片

基于E203 RISC-V的音频信号处理系统 -协处理器的乘累加过程

蜂鸟E203协处理器EAI指令及接口

基于E203 NICE协处理器扩展指令

基于E203 NICE协处理器扩展指令2.0

PIC64GX1000 RISC-V MPU:一款面向嵌入式计算的高性能64位多核处理器

明晚开播 |开源芯片系列讲座第28期:高性能RISC-V微处理器芯片

直播预约 |开源芯片系列讲座第28期:高性能RISC-V微处理器芯片

RISC-V和ARM有何区别?

用于RISC-V设计的基本安全协处理器

用于RISC-V设计的基本安全协处理器

评论