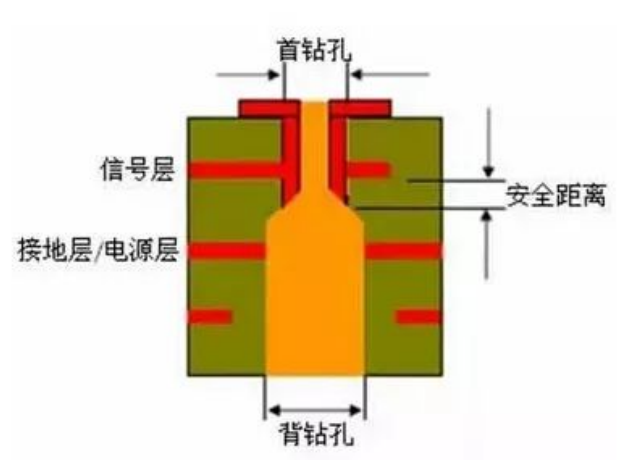

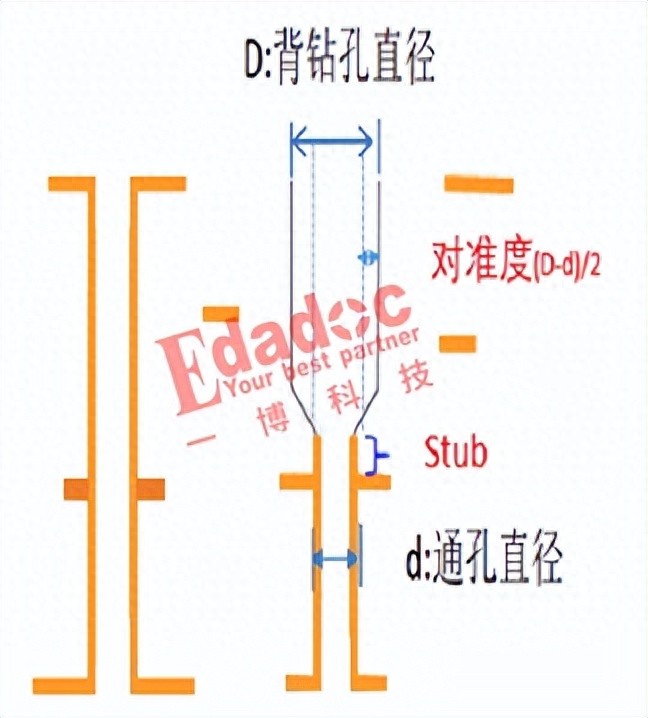

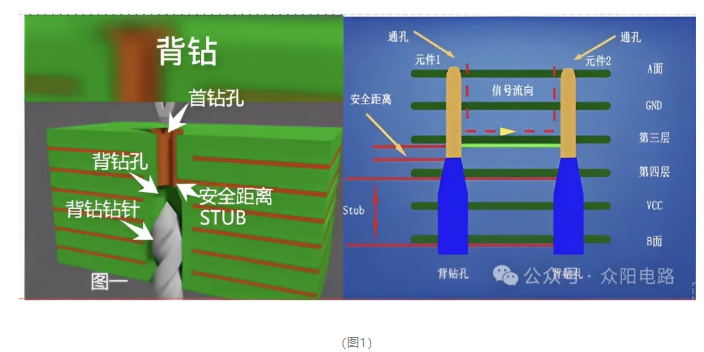

背钻其实就是控深钻比较特殊的一种,在多层板的制作中,例如12层板的制作,我们需要将第1层连到第9层,通常我们钻出通孔(一次钻),然后陈铜。这样第1层直接连到第12层,实际我们只需要第1层连到第9层,第10到第12层由于没有线路相连,像一个柱子,如图1所示。

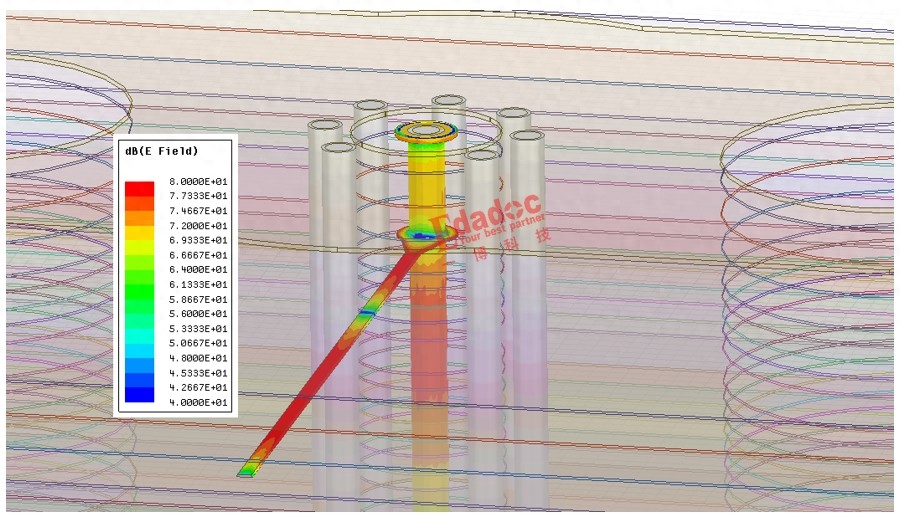

这个柱子影响信号的通路,在通讯信号会引起信号完整性问题。所以将这个多余的柱子(业内叫STUB)从反面钻掉(二次钻)。所以叫背钻,但是一般也不会钻那么干净,因为后续工序会电解掉一点铜,且钻尖本身也是尖的。所以PCB厂家会留下一小点,这个留下的STUB的长度叫B值,一般在50-150UM范围为好。

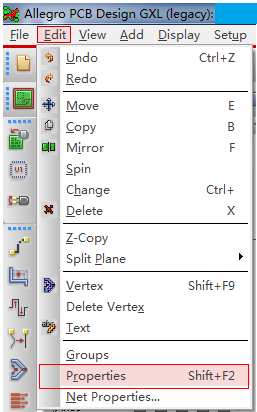

1、执行菜单命令,选择Edit->Properties,激活属性命令,如图2所示。

▲图1 背钻孔示意图

▲图2 背钻孔示意图

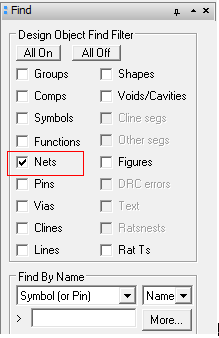

2、在激活“property edit”的命令状态下,find面板中只勾选nets对象。

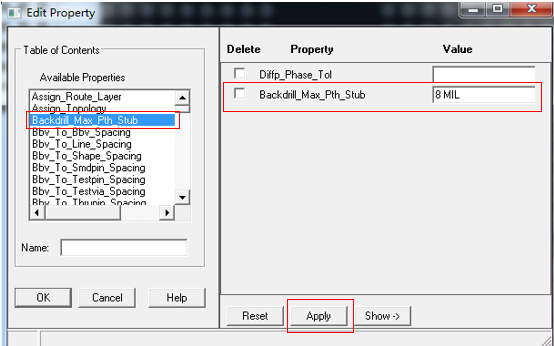

3.然后选择要背钻的网络,随即会自动弹出“Edit Properties”对话框,左边的选项栏中选择“Backdrill_max_pth_stub”选项增加背钻属性,背钻Stub值可以填8,但是工厂加工能力可能达不到,此Stub值意义不大,随后点击”Apply”

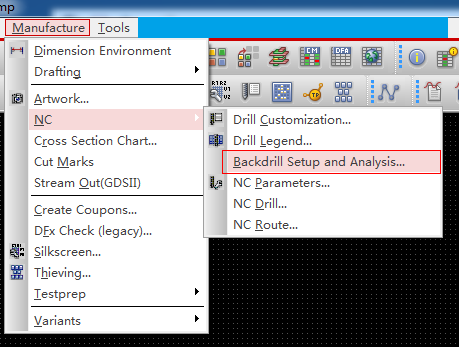

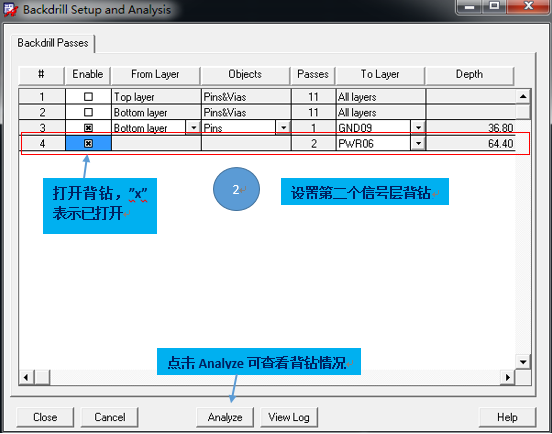

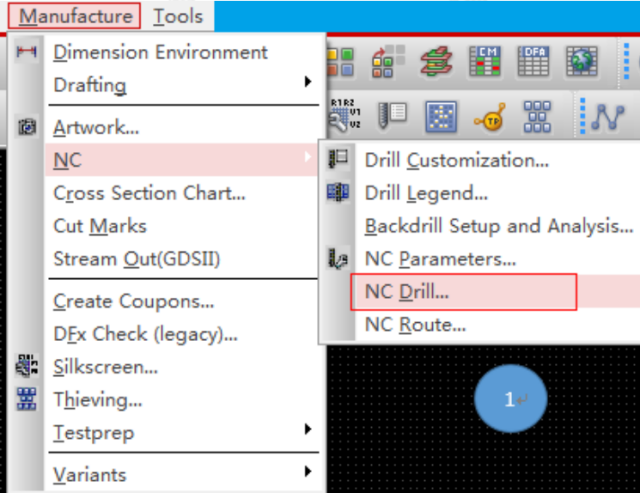

4.选择Manufacture->NC->Bacdrill Setup and Analysis…进入背钻层设置

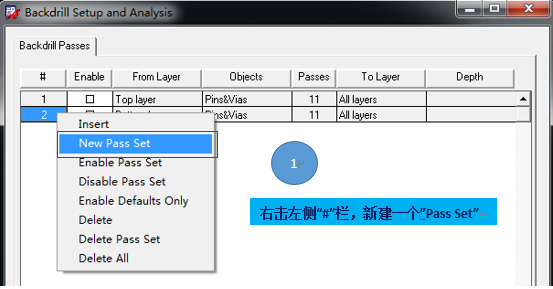

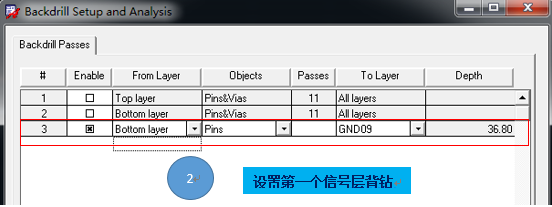

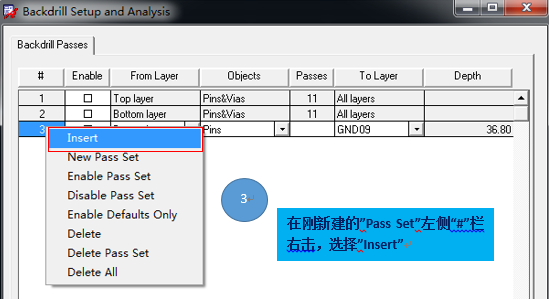

5.设置需要背钻的层,如需要背钻的信号分布在Layer5、Layer8,背钻从Botom->Top方向背钻,将要钻掉的层设置分别设置为Bottom->Layer6、Bottom->Layer9,设置如下。

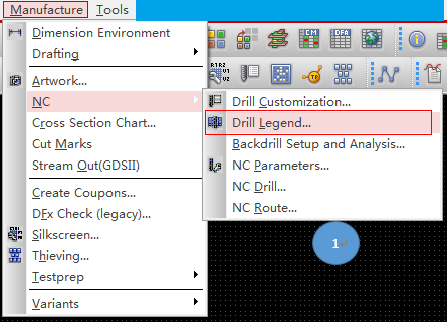

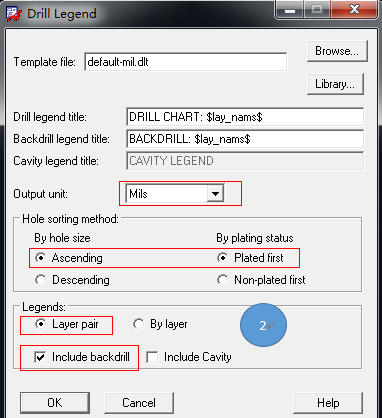

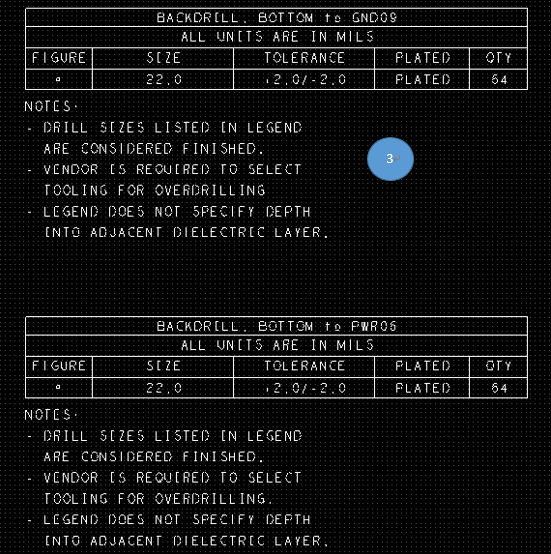

6、选择Manufacture->NC->Drill Legend输出背钻符号

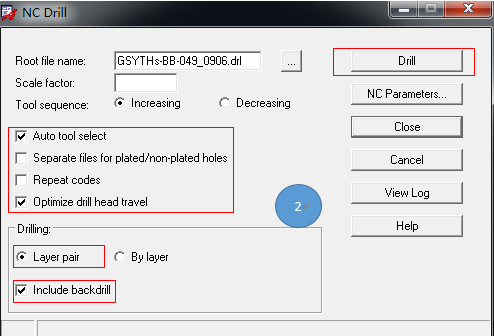

7.选择Manufacture->NC Drill输出钻孔文件

审核编辑 :李倩

-

pcb

+关注

关注

4417文章

23967浏览量

426201 -

电解

+关注

关注

1文章

86浏览量

18374 -

allegro

+关注

关注

42文章

773浏览量

150523

原文标题:Cadence Allegro背钻设置详细介绍教程

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

11:如何在 Allegro 中添加自定义的测试点 I Allegro PCB 设计小诀窍

02. 如何在 Allegro 中快速自定义字体?| 芯巧Allegro PCB 设计小诀窍

01. 如何在 Allegro 中快速区别不同网络?| 芯巧Allegro PCB 设计小诀窍

PCB 背钻塞孔翻车记!绿油凸起竟让焊接 “手牵手” 短路

高速PCB板DDR5数据信号的长STUB要背钻吗?

PCB为啥现在行业越来越流行“浅背钻”了?

毫米之间定成败:PCB背钻深度设计与生产如何精准把控

毫米之间定成败:PCB背钻深度设计与生产如何精准把控

别让孔偏毁了信号!PCB 背钻的 XY 精准度如何做到分毫不差?

别让孔偏毁了信号!PCB 背钻的 XY 精准度如何做到分毫不差?

众阳电路背钻工艺技术简介

Cadence Allegro背钻设置详细介绍教程

Cadence Allegro背钻设置详细介绍教程

评论