二维半导体薄膜在任意表面的异质外延技术

上海超级计算中心用户北京大学陈基研究员与合作者提出了一种在不同晶体对称性、不同晶格常数和三维架构基底上异质外延生长半导体2H-MoTe2薄膜的通用合成技术,克服了衬底对异质外延的限制。2022年8月15日,相关研究成果以“用于大规模异质集成的任意表面上半导体2H-MoTe2薄膜的异质外延”(Heteroepitaxy of semiconducting 2H-MoTe2 thin films on arbitrary arbitrary surfaces for large-scale heterogeneous integration)为题,在线发表于《自然•合成》(Nature synthesis)。

半导体行业依赖技术创新来保持器件小型化和成本降低的步伐。同时,信息的高速传输和处理需要将电子和光子器件集成在同一芯片上。因此,未来发展将同时采用平面和三维 (3D) 复合架构。在材料集成的不同策略中,外延生长是制造具有高质量界面的半导体异质结构的有效途径。然而,在具有大晶格失配的任意材料(更不用说3D架构)上异质外延传统3D 晶体薄膜且不产生具有高密度缺陷的界面是极具挑战性的,因此需要新技术来打破晶格失配和结构不对称对单晶半导体生长的限制。

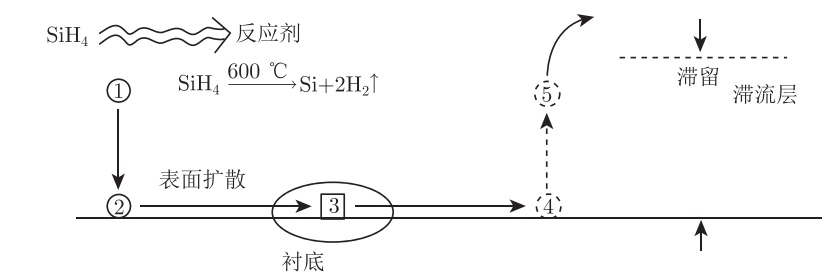

最近,将二维(2D)半导体与传统电子和光子学器件无缝集成引起了人们的极大兴趣,这为硅基芯片带来了新的应用。二维半导体表现出高的机械稳定性以及独特的电子和光电特性,非常适合异质光电集成。实现高密度集成,光互连结构需要尽可能靠近电子器件。为了实现这一目标,首先需要开发一种在任意结构上直接合成单晶二维半导体的异质外延方法,包括在高度晶格不匹配的基底和非平面的3D架构上。因此,必须开发一种新的可以解除衬底限制的合成范式,即不同于传统的垂直外延工艺(如金属有机化学气相沉积(MOCVD)、分子束外延(MBE)等)。

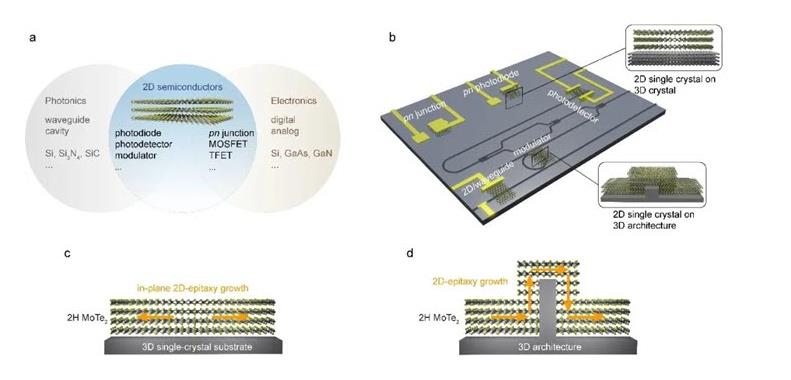

科研团队在前期二维碲化钼(MoTe2)相变与可控制备的基础上(J. Am. Chem. Soc. 141, 2128-2134, 2019; Science 372, 195-200, 2021)进一步提出了一种不受支撑基底限制的平面内二维横向外延技术,将单晶2H-MoTe2半导体薄膜与高度晶格失配的平面晶体或任意形貌的3D架构异质集成(图1),从而发展前所未有的集成技术与器件功能。

研究工作得到国家重点研发计划、国家自然科学基金、北京市自然科学基金等项目以及上海超级计算中心、北京大学长三角光电科学研究院等机构的支持。

-

半导体

+关注

关注

339文章

31279浏览量

266754 -

超级计算

+关注

关注

1文章

45浏览量

11591 -

衬底

+关注

关注

0文章

39浏览量

9637 -

光子器件

+关注

关注

0文章

32浏览量

12191 -

超算

+关注

关注

1文章

118浏览量

9547

发布评论请先 登录

[VirtualLab] 二维叉形光栅产生涡旋光阵列

椭偏仪在半导体的应用|不同厚度c-AlN外延薄膜的结构和光学性质

二维影像扫描引擎在门禁二维码刷卡梯控行业中的应用

新加坡国立大学:研究基于二维材料的多属性传感平台

面向硅基产线:二维半导体接触电阻的性能优化

中航光电推出二维FA光纤阵列组件

类脑视觉芯片里程碑突破:复旦团队首创二维半导体DRAM仿生神经元

半导体外延工艺在哪个阶段进行的

台阶仪应用 | 半导体GaAs/Si异质外延层表面粗糙度优化

二维半导体薄膜在任意表面的异质外延技术

二维半导体薄膜在任意表面的异质外延技术

评论