首先分享一个让电路里面的某些cell可以在layout做LVS的时候被忽略掉。因为有些电路对寄生的电阻电容之类的很敏感,所以可以在前仿的时候就加在电路里面,防止前仿跟后仿差别太大了。

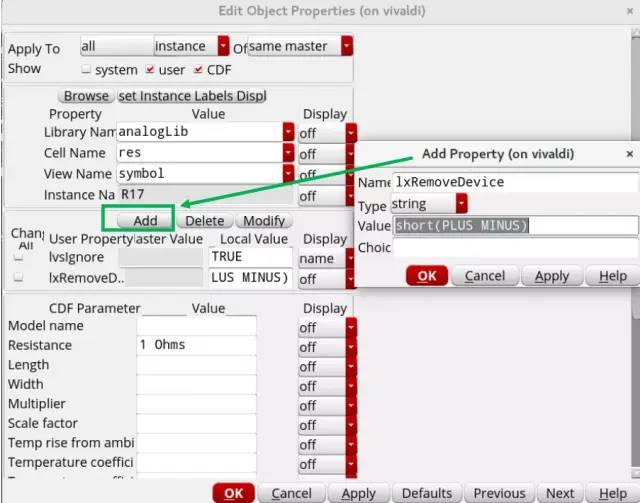

在property里面加上这两条,会被LVS视为短路

PS:知乎评论区有同行推荐的presistor,pcapacitor,pinductor也可以在做LVS的时候被视为短路。(上图里面的办法适用于所有的cell,包括并不限于理想的cap,res,ind,vdc,idc等等)

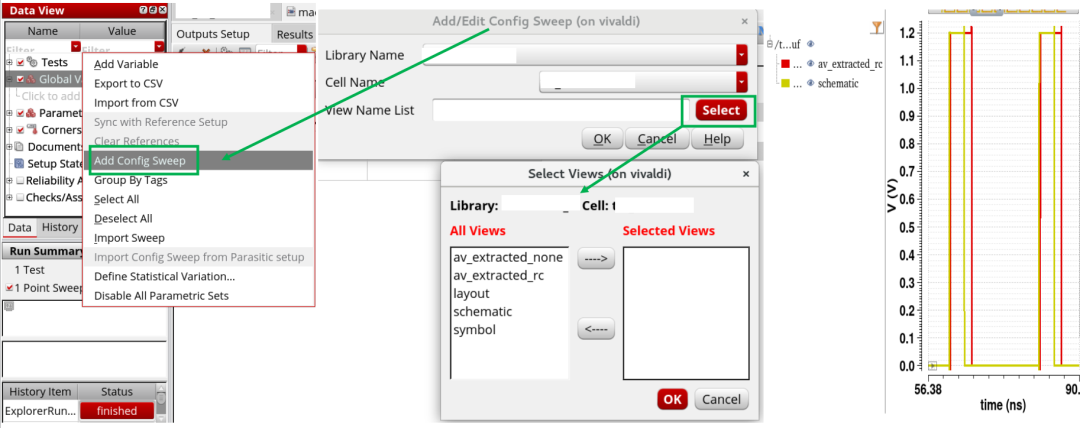

第二个tip,为了同时对比前仿跟后仿的结果,可以采用一种稍微有那么一点点巧妙的技巧,同时跑前仿和后仿:

在adexl或者mastro里面,右键点击Global Variable,出现Add Config sweep,然后选中要跑的cell的views,例如av_extracted_rc和schematic,然后OK加OK,然后跑仿真,就会同时出现前仿和后仿的波形

当然,其实这种办法跟跑两次的差别不大。需要注意的是,config sweep里面选中的是那个有av_extracted的cell,例如你跑t_comparator,那么应该选择comparator的av_extracted_rc和schematic。(不是t_comparator这个test bench)

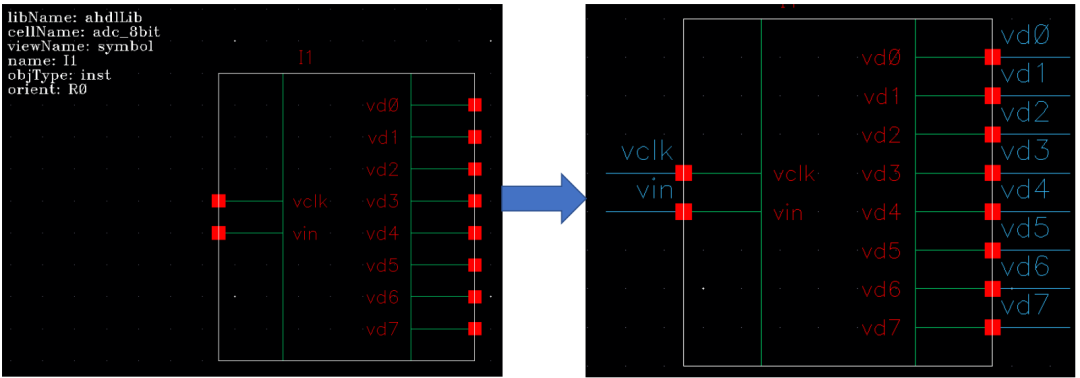

第三个技巧非常非常简单(按空格键),但是遇到拥有很多pin的symbol时,其实非常好用:

拿个理想的adc举例。按i加一个adc到schematic,然后选中这个adc,按一下空格键,就出现了右边这样跟pin名字一样的wire

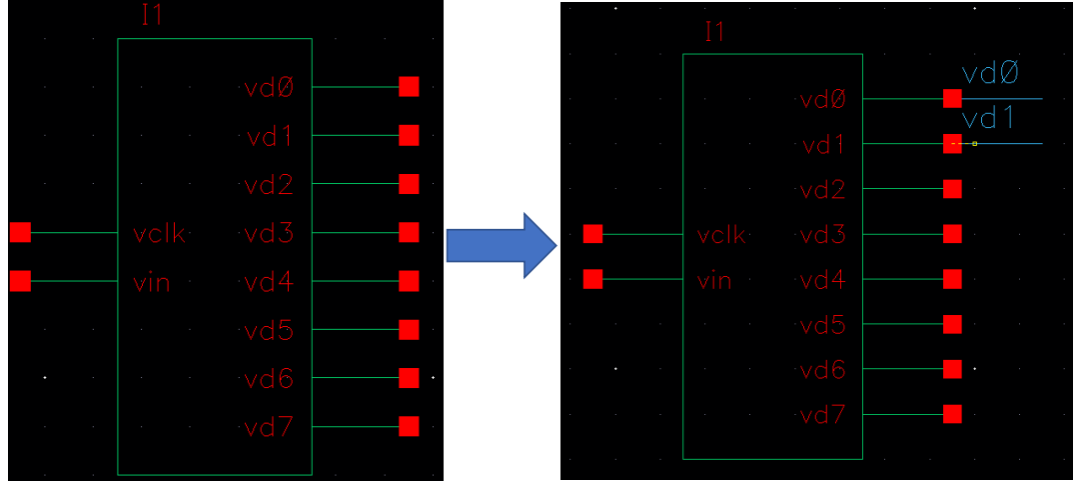

当然,如果你没有选中这个adc,而是直接按了空格键,你还能有选择的加一些wire:

可以一条线一条线的加wire,适用于只加某一些wire的情况。

审核编辑:刘清

-

adc

+关注

关注

100文章

7946浏览量

556871 -

LVS

+关注

关注

1文章

38浏览量

10521 -

电阻电容

+关注

关注

1文章

41浏览量

10143

原文标题:继续分享一些virtuoso小技巧

文章出处:【微信号:analogIC_gossip,微信公众号:通向模拟集成电路设计师之路】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PCB Layout在HDC2010底部是怎么处理?是打一个大孔?还是做焊盘接地?

非规则矩形电阻在Calibre LVS中阻值提取

in-cell panel_In-Cell触摸屏原理

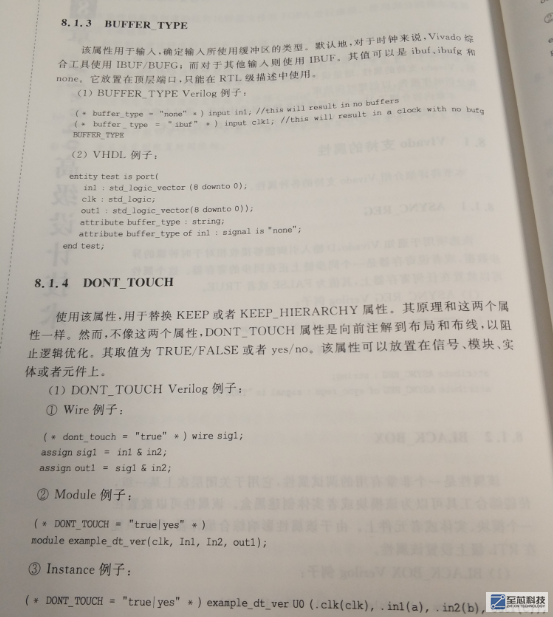

Vivado防止信号被综合掉的三种方法

一个经验丰富的Layout工程师如何做开关电源资料下载

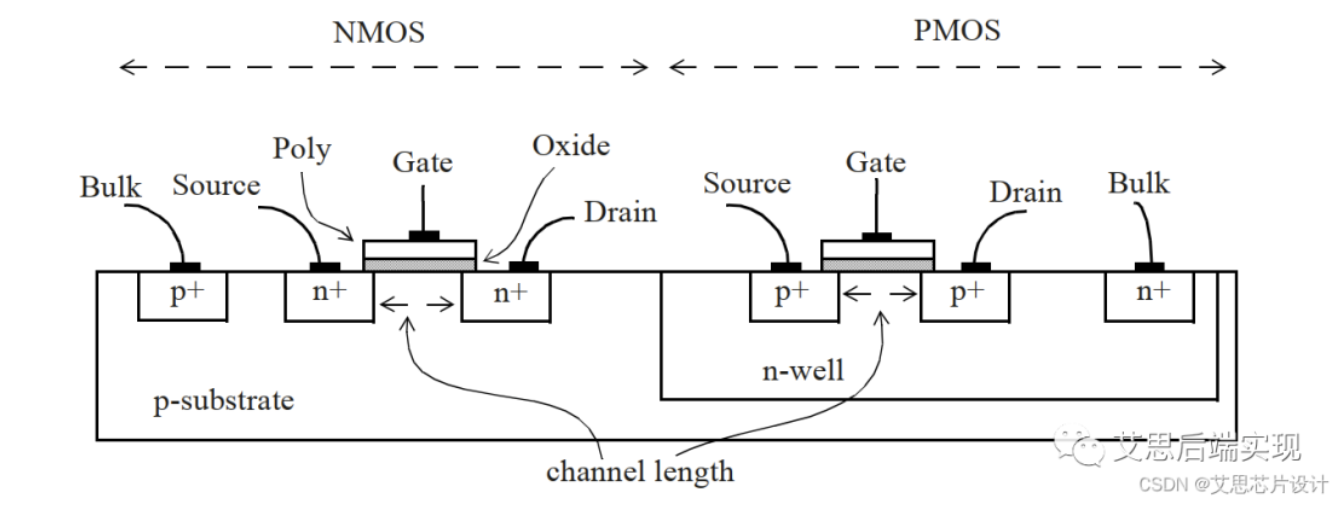

物理验证LVS对bulk(体)的理解和处理技巧

探讨一下std-cell在LVS的特殊处理

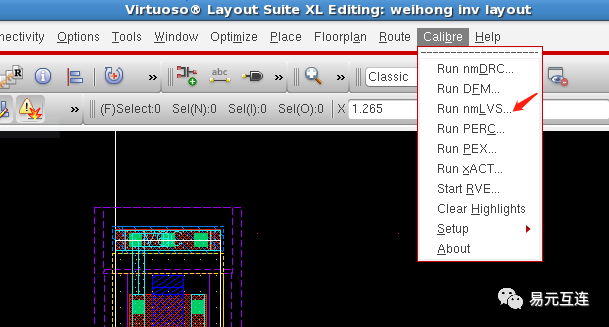

Cadence Virtuoso设计的一个反相器LVS验证案例

分享一个cell在layout做LVS时被忽略掉的方法

分享一个cell在layout做LVS时被忽略掉的方法

评论