此文介绍FPGA管脚的调整技巧,一起来学习吧。

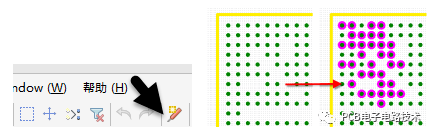

(1)为了方便识别哪些Bank之间可以互调,必须先对FPGA各个Bank进行区分。在原理图编辑界面中,执行图标命令“交叉探针”,单击某个FPGA的某个Bank,直接跳转到PCB中相对应的Bank管脚高亮,这时可以在某一机械层添加标注,进行标记,如图12-2所示。

图12-2 Bank的标记

(2)按照相同的操作方法可以把调整Bank在PCB中进行标记,如图12-3所示。

图12-3 被标记的FPGA

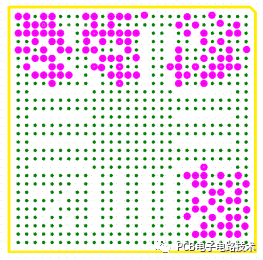

(3)完成上述步骤之后,就可以按照正常的BGA出线方式把所有的信号脚进行引出,并按照走线顺序对接排列,但非连接上,如图12-4所示,飞线是交叉的,但是不直接连上。最后保存好所有文档。

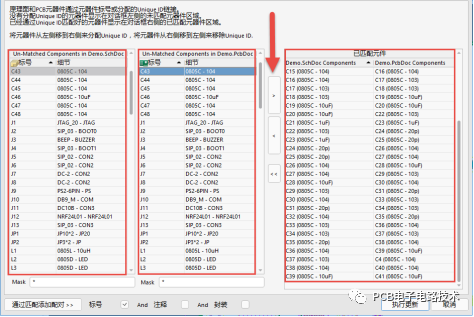

图12-5 元件的匹配

(5)执行菜单命令“工具-管脚/部件交换-配置”,定义和使能可调换管脚元件,如果弹出警告,须重新返回第(4)步进行操作,或者执行从原理图导入PCB的操作,使原理图和PCB完全对应上之后再按照此步骤进行操作,否则会弹出如图12-6所示的警告信息。

图12-6 警告信息

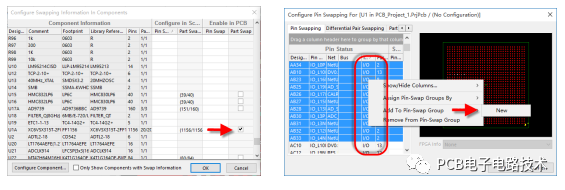

(6)找到FPGA对应的元件位号,勾选使能状态,双击该元件,对该元件的可以调换的I/O属性管脚创建Group操作,单击“OK”按钮,设置完毕,如图12-7所示。

图12-7 可调换FPGA的使能及Group设置

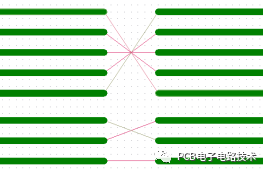

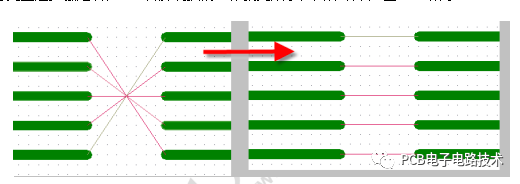

(7)执行菜单命令“工具-管脚/部件交换-交互式管脚/网络交换”,单击之前对接的信号走线,进行线序调换。注意:“Project”工程文件一定要保存一下,再操作。

执行完上述步骤之后,PCB管脚调换的工作就完成了,具体效果如图12-8所示。

图12-8 线序的调换调整

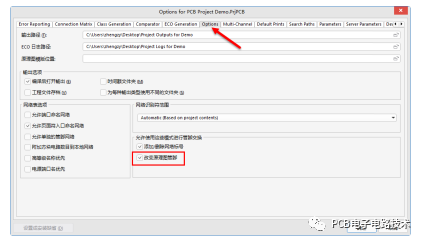

(8)PCB执行调换更改之后,需要把网络交互反导入原理图,如图12-9所示,执行菜单命令“工程-工程选项”,勾选反导入选项“改变原理图管脚”。

图12-9 反导入原理图设置

(9)在PCB设计交互界面中,执行“Update SchemaTIc in Project”命令,按照之前原理图导入PCB那样的方法,完成PCB导入原理图。

因为有些原理图绘制的方式或格式错误,执行反标可能不完全或残缺,建议反标之后利用正导入方式核对一遍或者直接手工方式绘制管脚更换表,再一一进行比对更改。

审核编辑:郭婷

-

FPGA

+关注

关注

1664文章

22503浏览量

639290 -

pcb

+关注

关注

4417文章

23966浏览量

426180

原文标题:FPGA管脚的调整技巧

文章出处:【微信号:PCB电子电路技术,微信公众号:PCB电子电路技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

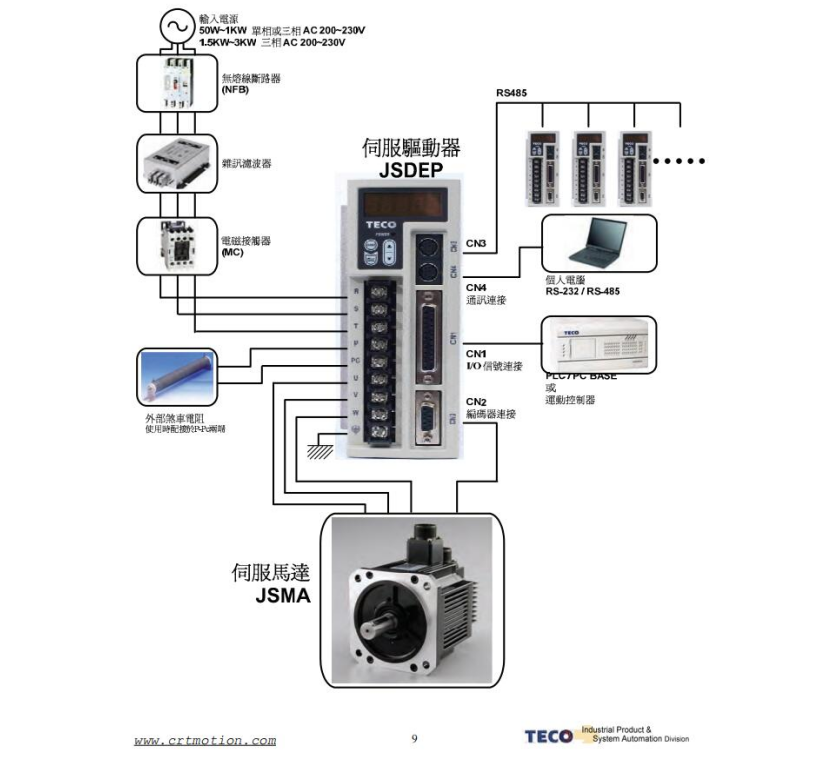

伺服驱动器增益参数的调整方法

动态调整策略的应用场景有哪些?

CW32 MCU的NRST管脚有何特点?

FPGA测试DDR带宽跑不满的常见原因及分析方法

常用伺服参数的调整

动态调整同步周期的具体方法是什么?

电磁流量计的主要参数及调整方法

FPGA技术为什么越来越牛,这是有原因的

FPGA管脚的调整 有哪些方法技巧

FPGA管脚的调整 有哪些方法技巧

评论