要满足苛刻的频率合成器要求,通常需要做到一定程度的设计灵活性。基本的锁相环(PLL)频率合成器能以低成本、高空间效率、低功耗封装提供合理的频谱纯度和频率捷变,因此它在射频(RF)系统核心位置发挥作用已经有段时间了。但是,在要求快速切换速度、低相位噪声或低杂散信号电平的场合,有必要使用更为复杂的架构。通过正确的设计方法,结合使用现代低成本高集成度的PLL和直接数字合成器(DDS)集成电路(IC)可以极大地促进高性能架构的实现。

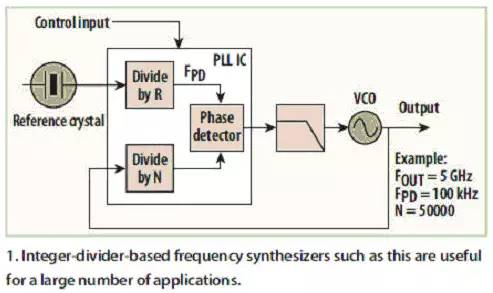

大部分高频系统都使用传统的基于整数分频器的设计(图1)或基于分数N分频器的设计。不管是使用哪种设计,联合使用单个通用频率合成器IC和一个外部压控振荡器(VCO)通常都可以实现要求的功能。VCO功能可以用IC、模块或分立元件解决方案甚至在合成器芯片内部实现,具体取决于所要求的频率范围、相位噪声性能以及空间、成本和功耗约束条件。最终设计通常以制造商的应用笔记为基础,并且一般可以使用可下载的应用程序完成合成器的寄存器加载和相位检测器增益的设置等功能。

图1、像这种基于整数分频器的频率合成器对许多应用来说都非常有用。

不过,对于要求非常高的某些应用来说,基本架构的性能也许远远满足不了要求,特别是在相位噪声、杂散信号电平以及频率切换速度方面。多普勒雷达系统中使用的频率合成器以及工作在微波频率、使用快速频率切换和/或高阶调制方案的通信系统就是这种应用的很好例子。

举例来说,如果一个应用要求整数PLL合成器有高的输出频率、相对小的调谐步长(这意味着高的分频比),这将导致环路带宽内产生很高的相位本底噪声[因为相对于输出的相位检测器噪声将增加20log(N)]。比如在5GHz输出频率和100kHz信道间隔情况下所需的分频比是50000,这将导致94dB环路带宽内的本底噪声超过相位检测器的噪声(在1Hz带宽内的典型值约为-75dBc)。典型的小数N频率合成器IC在1Hz带宽的噪声指标可以达到-85dBc左右。

虽然直接模拟频率合成器(一般由开关可选的倍频器、混频器和滤波器组成)在切换速度和相位噪声方面可能比较优秀,但它们的实现通常太过复杂,特别是当要求很好的杂散信号性能时。数字直接合成器(DDS)可以提供精细的调谐步长、快速频率切换速度和良好的相位噪声,但不采用额外倍频器的话,无法直接提供微波频率输出。

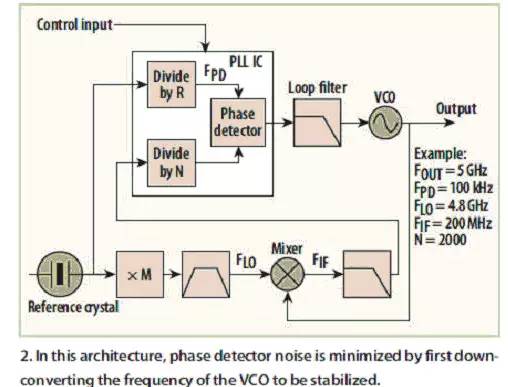

虽然不是专门用于这样的设计,但为更常见应用开发的PLL和DDS类型器件通常可以用作更为复杂、更高性能架构中的构建模块。图2显示了一个基于PLL的架构例子,这种架构完全可以用来提高相位噪声性能。在这个例子中,VCO输出在连接到频率合成器IC输入之前先下变频到一个低得多的频率。这样需要的分频比就降低了,从而减少了来自相位检测器的噪声贡献。对于图示所示例子来说,分频比将从50000降低到2000,环路带宽内的相位本底噪声极限将改善28dB到-103dBc。如果是宽带应用,可以采用多级下变频电路,本振(LO)频率则通过开关选择以保持较低的N值。

图2、在这种架构中,通过先将待稳定的VCO频率进行下变频可以最大限度地减小相位检测器噪声。

架构的改变在取得快速频率切换时间时也非常有用。PLL稳定到一个新频率所需的时间反比于环路带宽。在简单架构中,对小的信道频率间隔要求意味着使用窄的环路带宽,这将导致环路的频率步长稳定时间变慢。在基于整数PLL的设计中,参考频率将等于这个频率步长,而且环路带宽必须比这个步长小大约一个数量级。在基于小数N的设计中,虽然参考频率可以保持高得多的值,但环路滤波器通常仍然必须对落在步长倍数处的信号进行高衰减,从而对环路带宽设置了一个上限。然而,通过将DDS用作PLL内的高频参考源,分频比可以保持低值(这样可以最大限度地减小噪声),同时无需约束环路带宽就能实现非常小的频率步长。

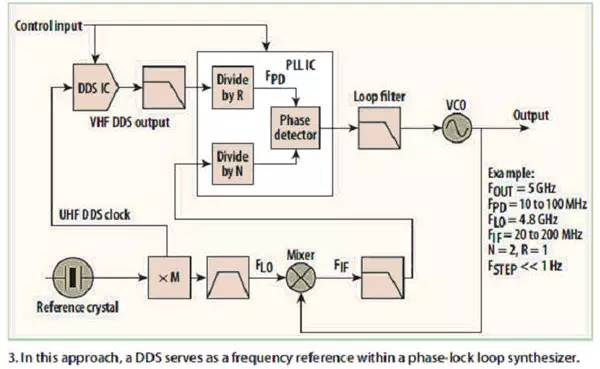

现代DDSIC可以用很小的外形封装产生甚高频(VHF)范围内的输出,并且具有MHz级的调谐步长和优秀的相位噪声。频率和相位调制功能通常也包含在内。近端杂散信号电平取决于相位查找表分辨率和输出数模转换器(DAC),而且一般都非常好(约-80dBc);然而,在输出端会呈现电平很高的其它取样信号。通过将DDSIC用作PLL中的频率参考源,输出频率可以转换成需要的任何频率,多余的取样信号也可以被PLL高效地滤除。图3显示了这种架构的例子。

图3、在这种方法中,DDS用作锁相环合成器中的频率参考源。

PLL可以认为是提供跟踪滤波功能,这是很有益的,因为它能极大地衰减DDS输出端的多余取样信号以及由下变频过程产生的其它信号。根据可以容忍的杂散信号电平,可以要求PLL对电平已经很低的近端杂散信号进行少许衰减或不做额外衰减。这样,PLL的环路带宽可以保持比传统PLL合成器中的实际带宽大许多,从而提高频率切换速度。PLL参考频率可以做得比DDS频率步长高出许多,分频比则非常小,从而实现优异的相位噪声性能。由于更大的环路带宽等同于特定偏移处更大的环路增益,而且来自相位检测器的噪声贡献更低,因此VCO贡献的噪声成份也可以得到有效降低。

值得注意的是,对这种架构中的频率规划细节必须仔细斟酌。参考振荡器、DDS时钟源和PLL参考源的频率必须相对于要求的信道间隔加以仔细选择,以便最大限度地降低所需参考发生硬件的复杂性,避免产生不能被滤除的近端杂散信号。

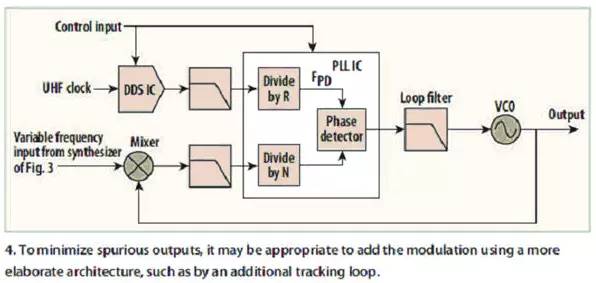

如上所述,许多DDSIC具有频率和相位调制功能,而这些功能可能在要求调制后输出的场合用得到,例如产生频率调制连续波(FMCW)雷达系统要求的线性频率斜坡场合。在实际应用中,为了尽量减少杂散信号输出,最好是增加使用更精巧架构的调制电路,比如通过额外的跟踪环路,如图4所示。

图4、为了尽量减少杂散输出,正确的做法是增加使用更加精巧架构的调制电路,比如通过额外的跟踪环路。

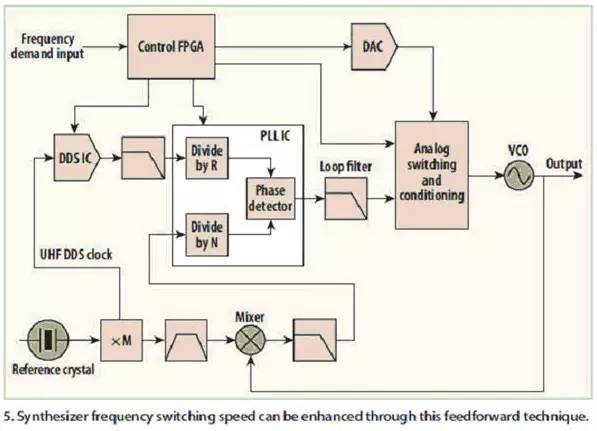

特别是在宽带系统中,通过使用前馈技术可以极大地提高频率切换速度,案例见图5。当接收到一个改变频率的命令时,环路被断开,VCO控制电压随后受DAC的控制,并到达一个预期对应所需新输出频率的值。接着环路再次闭合,同时PLL开始消除任何残留的相位与频率误差。在实际应用中,控制电压会很快调整到接近要求的值,而且由于PLL只需消除很小的残留误差,因此系统总的稳定时间将得到显著缩短。注意,除了加快稳定过程外,这种安排实际上在环路中使用许多频率转换级的宽带系统中已被证明是非常有用的,而如果不这样做的话,PLL可能没有足够的捕获带宽来稳定大的步长。为了实现信道改变过程中严格受控的时间顺序,控制逻辑功能最好由FPGA来完成。在实际使用时,对于拥有串行控制接口的器件来说,写入要求的寄存器数据所需的时间可能是决定可以实现的切换时间中最重要的因素。

图5、通过这种前馈技术可以提高合成器的频率切换速度。

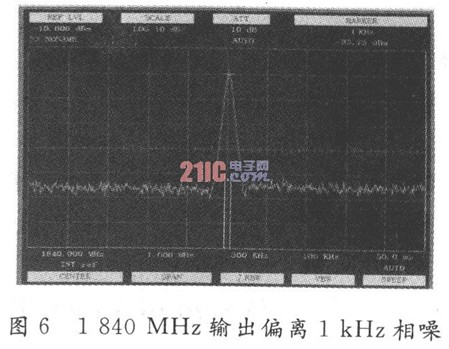

基于上述技术的实用微波频率合成器可以同时实现低杂散信号电平、很快的切换速度和优秀的相位噪声,同时还能提供频率调制(FM)和相位调制功能。通过仔细地选择架构和频率规划,同时在基于现场可编程门阵列(FPGA)的逻辑控制下使用现代PLL合成器和DDSIC,我们完全可以在高功效和高空间效率的封装中实现这种高性能的设计(图6)。

图6、在FPGA控制的架构中组合使用PLL和DDSIC能以高功效和高空间效率的封装提供所需的性能等级。

-

锁相环

+关注

关注

35文章

551浏览量

87248 -

频率合成器

+关注

关注

5文章

199浏览量

32153 -

pll

+关注

关注

6文章

740浏览量

134572 -

DDS

+关注

关注

21文章

614浏览量

151731

原文标题:频率合成器的高性能架构实现技术

文章出处:【微信号:射频问问,微信公众号:射频问问】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

详解频率合成器高性能架构的实现

如何利用FPGA设计PLL频率合成器?

什么是频率合成器

AD9850 DDS 频率合成器的原理及应用

DDS PLL短波频率合成器设计

基于DDS驱动PLL结构的宽带频率合成器的设计与实现

基于DDS的PLL高性能频率合成器设计实现

基于PLL和DDS的高性能频率合成器设计

基于PLL和DDS的高性能频率合成器设计

评论