我们的 28 纳米 AMD 赛灵思 7 系列器件持续广受欢迎,为工业、汽车、测试测量以及医疗市场的客户提供世界一流的技术与领先功能。这些细分市场的客户需要更长的产品寿命,通常要求 15 年的生命周期,许多产品还支持更长的生命周期。

延长产品生命周期

考虑到以上需求,AMD 赛灵思很高兴正式宣布,对所有 7 系列 FPGA 和自适应 SoC 的支持将至少延长至 2035 年。这其中包括我们的成本优化型 Spartan-7 和 Artix-7 FPGA、我们的整个 Zynq-7000 SoC 产品组合,以及 Kintex-7 与 Virtex-7 FPGA。所有速率和温度等级均包含在内。

7 系列器件在 AMD 赛灵思产品组合中拥有独特地位,今后多年里仍将是新设计的理想选择。

Spartan-7 FPGA 能以小型封装提供高单位功耗性能

Artix-7 FPGA 能以低功耗提供高收发器带宽

Zynq-7000 SoC 将基于 Arm 处理器的软件可编程性与 FPGA 的硬件可编程性相结合

我们郑重承诺支持长产品生命周期。由于产业在 2022 年及今后普遍面临供应链挑战,决定在项目中选用哪款器件来开展设计,比以往任何时候都更为重要。如果选用的器件在一年后便来到生命周期尽头,设计成本就会颇为高昂。

尽管一些器件推出已十年有余,我们仍向我们的 7 系列客户做出这份正式承诺,帮助他们坚定信心继续沿用现有 7 系列设计,同时基于功能十分多样的 7 系列技术开发全新项目。

-

处理器

+关注

关注

68文章

20332浏览量

254955 -

amd

+关注

关注

25文章

5707浏览量

140414 -

soc

+关注

关注

40文章

4624浏览量

230180

原文标题:AMD 延长全部赛灵思 7 系列器件产品生命周期至少至 2035 年

文章出处:【微信号:赛灵思,微信公众号:Xilinx赛灵思官微】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Altera三大FPGA系列产品生命周期支持延至2045年

AMD Versal自适应SoC中eMMC烧录/启动调试检查表(下)

AMD Versal自适应SoC中eMMC烧录/启动调试检查表(上)

使用Aurora 6466b协议实现AMD UltraScale+ FPGA与AMD Versal自适应SoC的对接

AMD UltraScale架构:高性能FPGA与SoC的技术剖析

AMD Vivado Design Suite 2025.2版本现已发布

AMD Versal自适应SoC内置自校准的工作原理

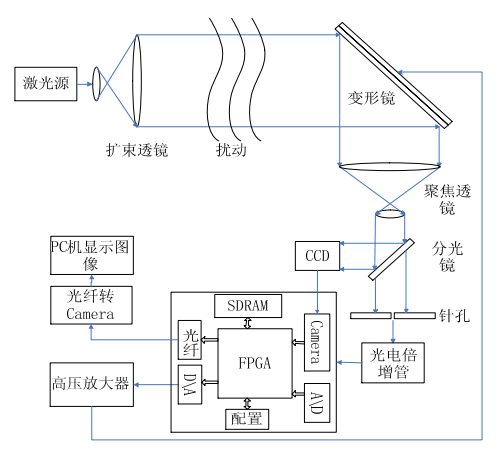

高压放大器驱动:基于FPGA的SPGD自适应光学控制平台的探索

如何在AMD Vitis Unified 2024.2中连接到QEMU

在AMD Versal自适应SoC上使用QEMU+协同仿真示例

基于FPGA LMS算法的自适应滤波器设计

AMD Spartan UltraScale+ FPGA 开始量产出货

利用AMD VERSAL自适应SoC的设计基线策略

适用于Versal的AMD Vivado 加快FPGA开发完成Versal自适应SoC设计

AMD宣布所有7系列FPGA和自适应SoC的支持将延长至 2035 年

AMD宣布所有7系列FPGA和自适应SoC的支持将延长至 2035 年

评论