DVK是用于解码器IP设计和合规性验证的比特流和软件工具链。它是芯片RTL设计、目标设备集成(如智能手机、智能电视、机顶盒)、发货给客户前的软件堆栈验证的必备工具。它经过精心构造,尽可能紧凑,在设计过程中实现最大覆盖范围并最小化验证时间。

DVK 定义

VQ DVK 的意思是:

视频解码器认证

一套全面的测试比特流、可配置的编码器和分析工具,用于验证解码器是否符合标准以及图形报告

适用于VVC、AVS3、AV1、HEVC、VP9解码器开发人员的强大验证环境

允许将测试解码器的输出与“已知正确”结果进行比较的工具

一种旨在确定解码器设计异常以节省验证和支持成本的工具

我们为每个编解码器提供不同的工具- VVC、AV1、HEVC、VP9。它们中的每一个在一组流和它们的数量上都是不同的。例如,VQDVK VVC 由以下比特流组组成:

语法 -方便的小尺寸(小分辨率和仅1-2 帧)以最大限度地覆盖每个语法元素和基本对的交叉覆盖。一个测试流- 一个功能,独立进行单独的“编码块”设计。适用于初始RTL 设计。

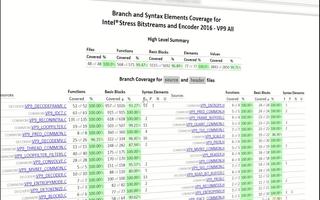

压力 -包括语法流所涵盖的所有功能,分辨率更高,帧数更多。适合解码器设计的高级阶段。

性能 -测试硬件解码器速度的极限。有利于最终验证以证明符合级别要求。

错误恢复 -一组不完全兼容的比特流,用于测试解码器对错误的鲁棒性和恢复能力。有利于最终验证以提供可行的最终用户产品。

主要特征

在本文中,我们将介绍VQDVK 的主要功能,即:

一体化

特殊流

交叉覆盖

分析工具

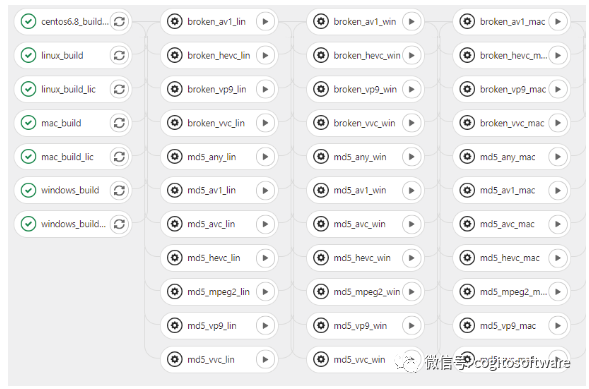

一体化

立即“开箱即用”的好处。DVK合规流可以立即集成到任何CI或验证管道中,以证明客户的产品。

特殊流

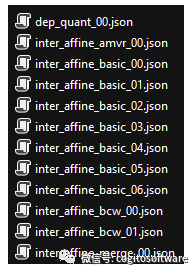

需要一些特别的东西吗?不是问题!DVK团队可以请求特殊流(应在合同中讨论),也可以使用非常灵活的编码器设计轻松生成:DVK的编码器基于参考并支持配置文件。在配置文件的帮助下,用户可以生成他们想要的任何流,因为任何语法元素都可以定义为开/关或特定值,例如“pps_init_qp_minus26”(VVC的语法元素示例之一)。作为一个附加示例,使用这种方法,如果启用“filmgrain”组(AV1示例)的所有元素以在验证期间测试此功能,则可以生成流。

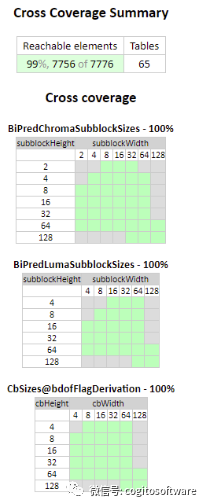

交叉覆盖

有时简单的一维覆盖是不够的。这就是DVK 在 VVC报告中引入 CrossCoverage的原因。CrossCoverage是 2D报告:为了降低成本,它需要智能,因此在某些情况下需要使用一些背景知识(另一个元素)检查元素覆盖率

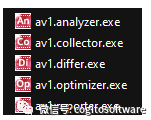

分析工具

分析工具是生成代码、语法和交叉覆盖率报告(跨平台html格式)并分析流并检查流集是否可以降低的专用工具。

非常重要的是,分析工具可以用于任何一组流。因此,如果一个组织已经拥有他们的流视频库,则可以通过这些工具轻松地对其进行分析、缩减或比较。

审核编辑:刘清

-

解码器

+关注

关注

9文章

1202浏览量

42859 -

编码器

+关注

关注

45文章

3903浏览量

141429 -

RTL

+关注

关注

1文章

393浏览量

62391

原文标题:ViCueSoft:解码器验证套件(VQDVK) 的主要优点

文章出处:【微信号:哲想软件,微信公众号:哲想软件】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

了解FPGA比特流结构

DAC1280 TDATA引脚输入的比特流,怎么产生这个比特流,算法是什么?

无法生成比特流

无法生成比特流

无法使用硬件评估许可证生成比特流

如何使用Vivado生成特定的部分比特流

是否需要在flash上切换黄金比特流和多重比特流的位置?

Xilinx是否有用于比特流加密的文档

匹配位置对比特流随机性的影响研究

使用加密和身份验证来保护UltraScale/UltraScale+ FPGA比特流

用于解码器IP设计和合规性验证的比特流和软件工具链DVK

用于解码器IP设计和合规性验证的比特流和软件工具链DVK

评论