电子发烧友网报道(文/周凯扬)数据中心作为CPU、GPU和加速器厂商最为关注的市场,自然也少不了RISC-V这个新架构来掺和一脚。我们在之前的文章中也对RISC-V在数据中心的进展做了一些介绍,RISC-V虽然在服务器通用CPU上发力迹象不明显,但要说AI加速器这类产品,很有可能会是RISC-V打入数据中心市场的最佳方向。

谷歌的RISC-V战略

自己设计芯片的服务器厂商之一,谷歌,似乎也开始打算用上RISC-V。在今年9月美国的AI硬件峰会上,SiFive首席架构师和谷歌的TPU芯片架构师展示了他们的合作方案。谷歌的TPU是谷歌设计专用于机器学习的加速器,用于在数据中心上运行TensorFlow、Pytorch和JAX等机器学习框架。

而TPU的主要计算单元就是矩阵乘法打算(MXU),由脉动阵列中的128x128乘法/累积器组成,在最小配置v4版TPU中包含4个TPU芯片,每个TPU芯片都有8个MXU,是TPU v3版的两倍,而且每个MXU都能使用BF16执行每周期16K的乘积累加运算。

然而,谷歌发现虽然TPU的机器学习算力虽然够用,但客户在利用这类大型AI加速器时,往往无法用它来完成其他的复杂计算负载,所以谷歌的做法是将SiFive的X280处理器核心,作为TPU的协处理器,用来提供维护和运行代码,跑加速器没法运行的内核。

虽然SiFive的X280主打的是加速AI/ML计算,但主要是针对边缘端,比如AR/VR、数码相机等等,并非用于数据中心的大型AI加速器。但在与谷歌等厂商的合作下,SiFive推出了一个名为矢量定制协处理器接口(VCIX)的技术,可以让大型AI加速器直接与X280的32x512位矢量寄存器文件高速通信。

这相比其他方案来说,矢量寄存器层级上的访问不仅可以提供更大的带宽、比PCIe更低延迟,还能简化软件栈、省下更多的硬件资源。X280和TPU核心分工合作,前者负责运行完整的Linux系统和虚拟机管理程序,后者负责密集的机器学习运算。

英特尔HorseCreek初见端倪

早在去年,英特尔就宣布将会用到SiFive的P550高性能RISC-V核心,以及自己的7nm工艺(即现在的Intel4工艺)来打造一款RISC-V SoC,代号名为HorseCreek。虽然到了2022年,SiFive最高性能的核心已经成了P650。但作为一个十三级流水线、三发射、乱序的64位RISC-V核心,P550的性能仍然是相当能打的,SiFive给到的定位也是对标ARM的Cortex-A75,同时只需不到一半的面积。

不过消息公布后,英特尔虽然又开展了一系列与RISC-V相关的行动,比如加入RISC-V国际基金会、IFS支持RISC-V芯片代工和推出RISC-V的FPGA开发平台等等,但HorseCreek却始终不见踪影。

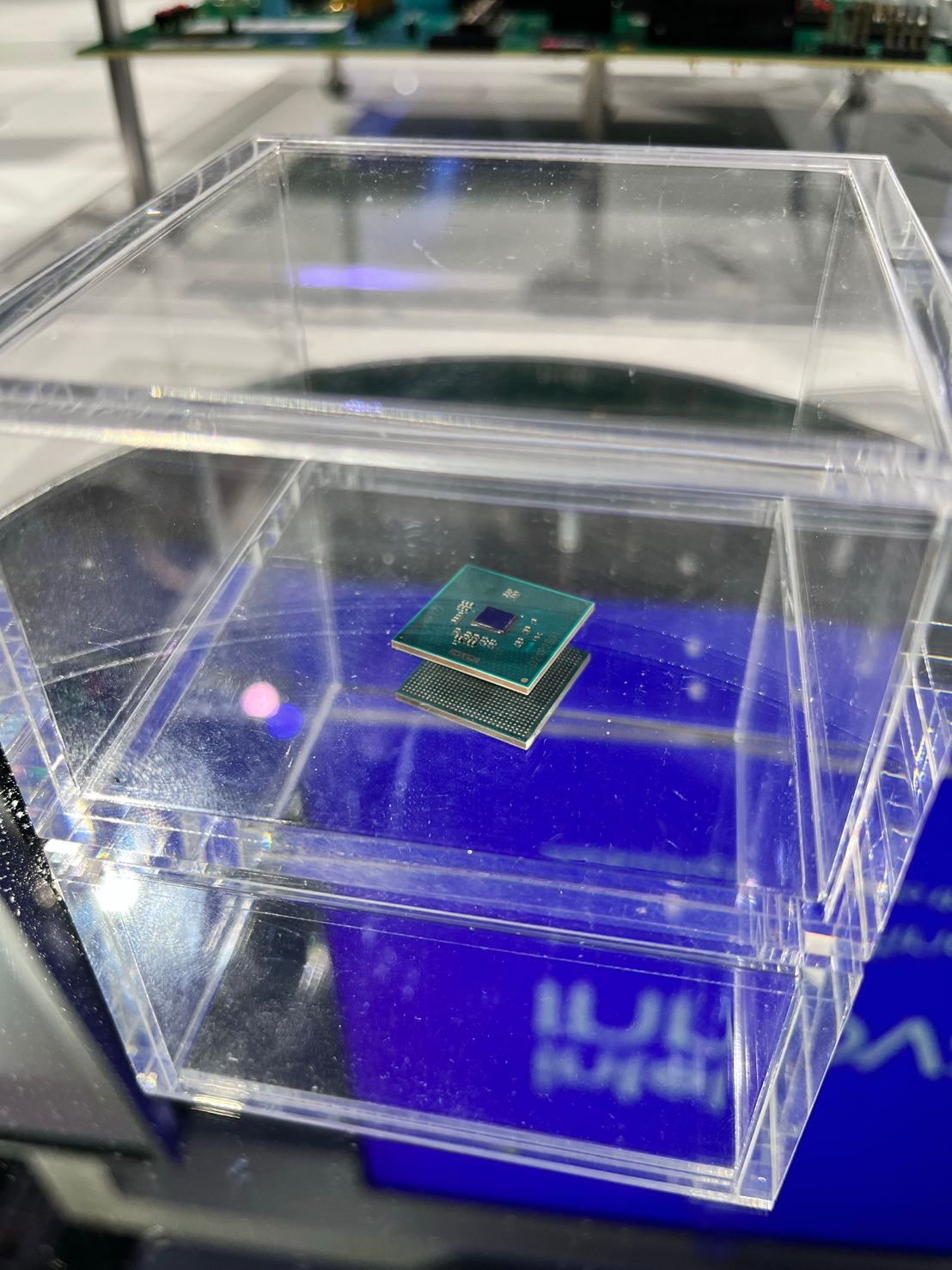

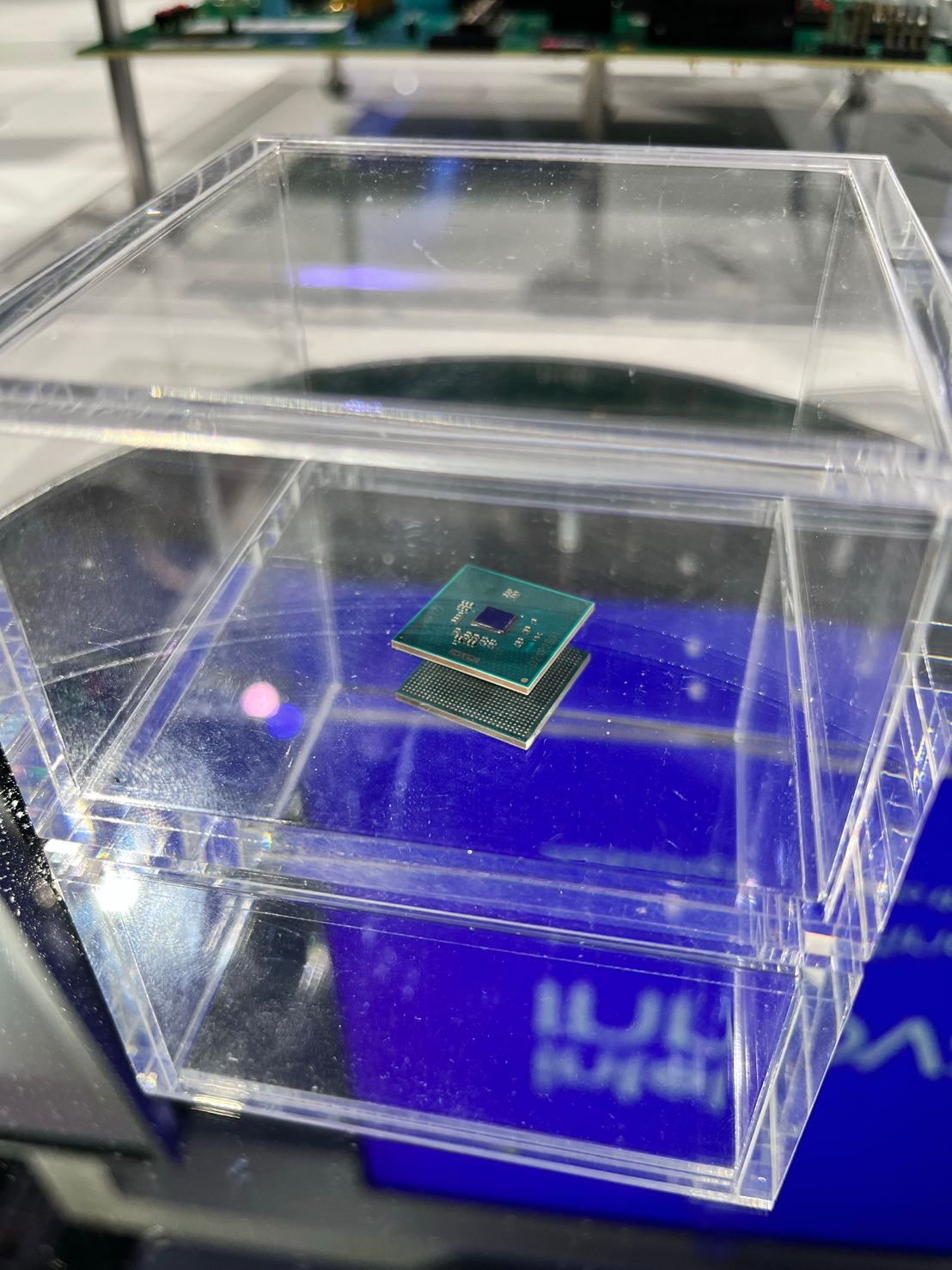

而在今年的IntelInnovation大会上,英特尔的不少合作伙伴都在现场搭建了展台,也有参会者终于在现场看到了HorseCreek的真面目。在Intel4工艺的加持下,HorseCreek将4个2.2GHz的SiFiveP550核心、DDR5和PCIe5集成到了4mmx4mm的单个裸片上,连英特尔CEO PatGelsinger本人也亲自来展台查看HorseCreek的开发平台。

而在今年的IntelInnovation大会上,英特尔的不少合作伙伴都在现场搭建了展台,也有参会者终于在现场看到了HorseCreek的真面目。在Intel4工艺的加持下,HorseCreek将4个2.2GHz的SiFiveP550核心、DDR5和PCIe5集成到了4mmx4mm的单个裸片上,连英特尔CEO PatGelsinger本人也亲自来展台查看HorseCreek的开发平台。

根据展台上公开的数据,HorseCreek配备了三级缓存,包括私有二级缓存和通用三级缓存。DDR5这块集成了英特尔的DDR PHY、DFI接口与Cadence的DDR内存控制器,支持到5600频率的DDR5内存,PCIe5.0部分集成了英特尔的PCIePhy和新思的PCIeRootHub控制器。除了英特尔提供的PLL、内存编译器、标准单元等数模IP以外,HorseCreek还用到了其他的IP,比如西门子的DFT和新思的NOC Fabric。

从以上数据可以看出,HorseCreek是一个集SiFive、英特尔和EDA厂商IP大成的SoC。如此强大的SoC加上丰富的接口支持,完全可以用于数据中心里。不过,HorseCreek的首个终端产品形态应该是SiFive的下一代HiFive开发板。上一代的HiFive Unmatched开发板已经售罄了,在疫情相关的供应链问题下,SiFive已经放弃了补货的打算,转而全力去打造下一代基于HorseCreek的HiFive开发板。

从以上数据可以看出,HorseCreek是一个集SiFive、英特尔和EDA厂商IP大成的SoC。如此强大的SoC加上丰富的接口支持,完全可以用于数据中心里。不过,HorseCreek的首个终端产品形态应该是SiFive的下一代HiFive开发板。上一代的HiFive Unmatched开发板已经售罄了,在疫情相关的供应链问题下,SiFive已经放弃了补货的打算,转而全力去打造下一代基于HorseCreek的HiFive开发板。

又一个千核RISC-V芯片

在戴尔的HPC社区大会上,来自美国的初创半导体公司InspireSemiconductor公布了他们为数据中心提供的RISC-V加速器方案,同时还给出了另一个有趣的说法,那就是现有的高性能计算方案已经“不够好”了。

在他们看来,目前的主流数据中心CPU都太慢了,无论有无加速器的辅助都是如此,而在有了加速器以后,90%的高性能计算都是由加速器负责了。再者就是GPU和FPGA的方案,InspireSemiconductor指出这两者的编程太复杂了,不仅锁定了软件栈,而且需要特定的技能才能获得足够好的计算结果。而ASIC和AI加速器的风险又太高了,从成本、时间上看都是如此。

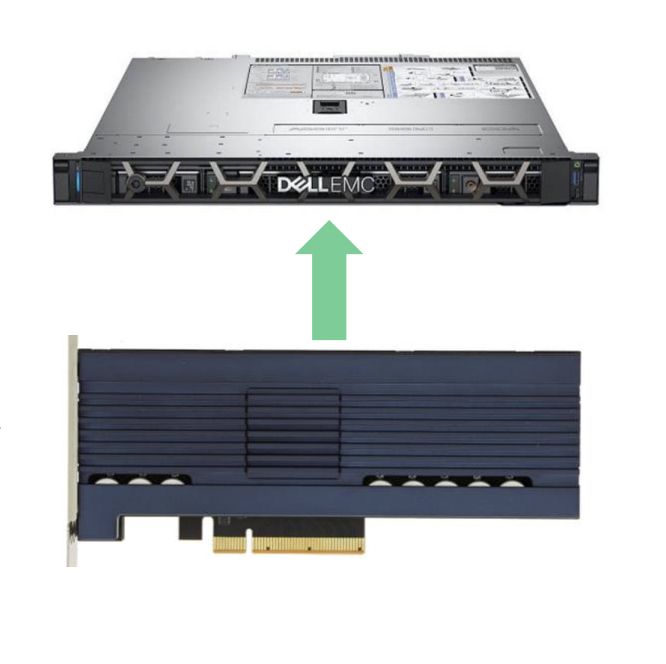

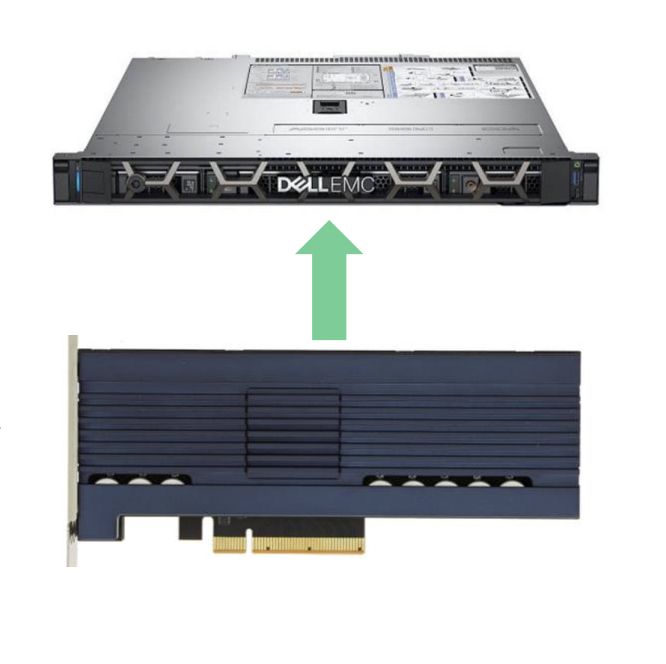

为此,InspireSemiconductor推出了他们的RISC-V加速器方案,Thunderbird。Thunderbird在单芯片上集成了2560个64位的CPU核心,单个PCIe加速卡上的核心数量更是超过5000个。InspireSemiconductor称他们用到了创新的高速互联方案,在高效利用这么多核心的同时,最高可以组成256个芯片的阵列。

相较其他加速器和GPU方案,Thunderbird加速器也有着功耗上的优势,单芯片的功耗在175W左右,同时他们给出了20W/Tflops的能效比,看来Thunderbird的峰值算力大概就在8.75Tflops左右了。虽然会上InspireSemiconductor也展示了谷歌、联想和IBM等客户或合作伙伴的一些反馈,但这些不少是客套话,是否已经用于这些公司的数据中心方案中还不好说。

相较其他加速器和GPU方案,Thunderbird加速器也有着功耗上的优势,单芯片的功耗在175W左右,同时他们给出了20W/Tflops的能效比,看来Thunderbird的峰值算力大概就在8.75Tflops左右了。虽然会上InspireSemiconductor也展示了谷歌、联想和IBM等客户或合作伙伴的一些反馈,但这些不少是客套话,是否已经用于这些公司的数据中心方案中还不好说。

InspireSemiconductor同时承诺了一个对开发者友好的软件生态系统,但他们并没有给出自己的软件方案,而是指出Thunderbird将充分利用RISC-V已有的丰富软件生态系统,比如OneAPI等,所以不必像竞品芯片那样去开发一次性的软件栈。如此一来更适合那些喜欢标准CPU编程模型的开发者,无需像GPU那样去学习CUDA、OpenCL,而是可以用Pragma和MPI这样的标准编译器方案。

AI编程上也是如此,InspireSemiconductor指出流行的AI框架,诸如TensorFlow、Pytorch和Glow等都已有了对RISC-V的支持,Linux也在操作系统支持的行列中。如此看来,InspireSemiconductor目前应该只提供了纯硬件方案,而这样的产品是否能在市面上取得成功,目前看来完全取决于英特尔Codeplay那边的OneAPI软件生态了。

谷歌的RISC-V战略

自己设计芯片的服务器厂商之一,谷歌,似乎也开始打算用上RISC-V。在今年9月美国的AI硬件峰会上,SiFive首席架构师和谷歌的TPU芯片架构师展示了他们的合作方案。谷歌的TPU是谷歌设计专用于机器学习的加速器,用于在数据中心上运行TensorFlow、Pytorch和JAX等机器学习框架。

而TPU的主要计算单元就是矩阵乘法打算(MXU),由脉动阵列中的128x128乘法/累积器组成,在最小配置v4版TPU中包含4个TPU芯片,每个TPU芯片都有8个MXU,是TPU v3版的两倍,而且每个MXU都能使用BF16执行每周期16K的乘积累加运算。

然而,谷歌发现虽然TPU的机器学习算力虽然够用,但客户在利用这类大型AI加速器时,往往无法用它来完成其他的复杂计算负载,所以谷歌的做法是将SiFive的X280处理器核心,作为TPU的协处理器,用来提供维护和运行代码,跑加速器没法运行的内核。

虽然SiFive的X280主打的是加速AI/ML计算,但主要是针对边缘端,比如AR/VR、数码相机等等,并非用于数据中心的大型AI加速器。但在与谷歌等厂商的合作下,SiFive推出了一个名为矢量定制协处理器接口(VCIX)的技术,可以让大型AI加速器直接与X280的32x512位矢量寄存器文件高速通信。

这相比其他方案来说,矢量寄存器层级上的访问不仅可以提供更大的带宽、比PCIe更低延迟,还能简化软件栈、省下更多的硬件资源。X280和TPU核心分工合作,前者负责运行完整的Linux系统和虚拟机管理程序,后者负责密集的机器学习运算。

英特尔HorseCreek初见端倪

早在去年,英特尔就宣布将会用到SiFive的P550高性能RISC-V核心,以及自己的7nm工艺(即现在的Intel4工艺)来打造一款RISC-V SoC,代号名为HorseCreek。虽然到了2022年,SiFive最高性能的核心已经成了P650。但作为一个十三级流水线、三发射、乱序的64位RISC-V核心,P550的性能仍然是相当能打的,SiFive给到的定位也是对标ARM的Cortex-A75,同时只需不到一半的面积。

不过消息公布后,英特尔虽然又开展了一系列与RISC-V相关的行动,比如加入RISC-V国际基金会、IFS支持RISC-V芯片代工和推出RISC-V的FPGA开发平台等等,但HorseCreek却始终不见踪影。

根据展台上公开的数据,HorseCreek配备了三级缓存,包括私有二级缓存和通用三级缓存。DDR5这块集成了英特尔的DDR PHY、DFI接口与Cadence的DDR内存控制器,支持到5600频率的DDR5内存,PCIe5.0部分集成了英特尔的PCIePhy和新思的PCIeRootHub控制器。除了英特尔提供的PLL、内存编译器、标准单元等数模IP以外,HorseCreek还用到了其他的IP,比如西门子的DFT和新思的NOC Fabric。

又一个千核RISC-V芯片

在戴尔的HPC社区大会上,来自美国的初创半导体公司InspireSemiconductor公布了他们为数据中心提供的RISC-V加速器方案,同时还给出了另一个有趣的说法,那就是现有的高性能计算方案已经“不够好”了。

在他们看来,目前的主流数据中心CPU都太慢了,无论有无加速器的辅助都是如此,而在有了加速器以后,90%的高性能计算都是由加速器负责了。再者就是GPU和FPGA的方案,InspireSemiconductor指出这两者的编程太复杂了,不仅锁定了软件栈,而且需要特定的技能才能获得足够好的计算结果。而ASIC和AI加速器的风险又太高了,从成本、时间上看都是如此。

为此,InspireSemiconductor推出了他们的RISC-V加速器方案,Thunderbird。Thunderbird在单芯片上集成了2560个64位的CPU核心,单个PCIe加速卡上的核心数量更是超过5000个。InspireSemiconductor称他们用到了创新的高速互联方案,在高效利用这么多核心的同时,最高可以组成256个芯片的阵列。

InspireSemiconductor同时承诺了一个对开发者友好的软件生态系统,但他们并没有给出自己的软件方案,而是指出Thunderbird将充分利用RISC-V已有的丰富软件生态系统,比如OneAPI等,所以不必像竞品芯片那样去开发一次性的软件栈。如此一来更适合那些喜欢标准CPU编程模型的开发者,无需像GPU那样去学习CUDA、OpenCL,而是可以用Pragma和MPI这样的标准编译器方案。

AI编程上也是如此,InspireSemiconductor指出流行的AI框架,诸如TensorFlow、Pytorch和Glow等都已有了对RISC-V的支持,Linux也在操作系统支持的行列中。如此看来,InspireSemiconductor目前应该只提供了纯硬件方案,而这样的产品是否能在市面上取得成功,目前看来完全取决于英特尔Codeplay那边的OneAPI软件生态了。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

英特尔

+关注

关注

61文章

10275浏览量

179274 -

谷歌

+关注

关注

27文章

6244浏览量

110250 -

数据中心

+关注

关注

16文章

5515浏览量

74644 -

RISC-V

+关注

关注

48文章

2792浏览量

51884

发布评论请先 登录

相关推荐

热点推荐

2025 RISC-V产业发展大会 | 赛昉科技全景展示规模化商用成果

2025年11月24日,RISC-V产业发展大会在珠海开幕。赛昉科技以“推动RISC-V规模化商用”为核心主题,重点展示了面向数据中心、边缘计算及智能终端的全栈产品与成熟应用,全面呈现

赛昉科技BMC全链路解决方案亮相英特尔生态大会,加速RISC-V数据中心管理芯片规模化应用

RISC-V架构创新应用的坚定推动者,赛昉科技携BMC解决方案全新亮相英特尔“数据中心基础设施”展区,并且受邀在“硬件基础架构与生态”论坛上发表演讲。赛昉科技解决方

英特尔携本地生态伙伴发布双路冷板式全域液冷服务器,引领数据中心散热与能效革新

服务器。该创新方案由全本地生态赋能,实现了关键热源的高比例液冷覆盖,在提升可靠性与能效的同时,显著降低能耗与运维成本,为数据中心散热与能效树立全新标杆。

发表于 11-19 21:21

•1171次阅读

赛昉科技重磅发布新产品,RISC-V实现数据中心规模化商用突破

2025年11月14日,中国香港——赛昉科技隆重发布首款基于RISC-V架构的数据中心管理芯片“狮子山芯”。作为一款具有里程碑意义的产品,“狮子山芯”成功实现了RISC-V在数据中心领

赛昉科技RISC-V“狮子山芯”打入数据中心市场,超聚变、英特尔顶力支持

规模化商业落地,为中国的算力基础设施发展注入了新的核心动能。 本次产品发布备受瞩目,赛昉科技创始人兼CEO徐滔、赋生资本创始人李家杰博士、香港投资管理有限公司行政总裁陈家齐女士、超聚变董事长兼CEO刘宏云、英特尔中国区数据中心

RISC-V创新中心与达摩院合作签约

10月30日,RISC-V创新中心与达摩院合作签约暨创新发展交流会在苏州市集成电路创新中心隆重举行,来自全国各地的重点企业、科研机构、行业协会、投资机构等代表出席活动,共话RISC-V

聚焦液冷痛点:英特尔UQD互换性认证助力数据中心高效发展

认证的技术创新之道,及其对降低数据中心运维复杂度、提升系统可靠性、助力液冷产业规模化的重要性。 英特尔数据中心与人工智能集团副总裁兼中国区总经理陈葆立表示:“作为AI模型运行和硬件部署的核心场景,

RISC-V 在数据中心软件生态系统中的机遇与挑战

RISC-V 作为一种开源指令集架构,凭借其灵活性、可扩展性和开源特性,在数据中心领域的应用正从探索阶段逐步向实际落地推进。目前,RISC-V 在数据中心的应用处于 “能跑通但需优化”

发表于 07-18 13:38

•5116次阅读

英特尔2025年Q1营收127亿美元,数据中心与AI业务可圈可点

今日,英特尔公布2025年第一季度财报。数据显示,英特尔第一季度营收达127亿美元,超出预期指引,产品业务营收为118亿美元,其中数据中心

端侧AI、数据中心,RISC-V已“上桌”

电子发烧友网报道(文/梁浩斌)从低功耗、低成本应用,迈向高性能、高算力,是RISC-V发展过程中的必经之路。随着RISC-V生态的发展,包括工具链、IP核的进一步完善,RISC-V正在加速冲击高性能

英特尔至强6处理器助力数据中心整合升级

继去年9月重磅推出英特尔 至强 6900性能核处理器后,英特尔进一步扩充至强6产品家族,于近期发布了包括至强6700性能核处理器及至强6500性能核处理器在内的多款新品,以更丰富的产品组合、卓越性能与出色能效,应对横跨数据中心、

英特尔至强6:如何炼就数据中心“全能型选手”

面对数据中心领域日益激烈的竞争,英特尔紧抓核心产品,继去年推出128核的至强6900P之后,近期又添“新兵”——至强6700P和至强6500P,进一步丰富了至强6产品线。英特尔至强6性能核处理器专为

英特尔Michelle Johnston Holthaus:深耕x86,持续为AI数据中心注入芯动力

“英特尔深耕数据中心市场数十余年,并通过x86架构引领标准制定和行业发展。目前,英特尔的处理器正为绝大多数数据中心提供动力。”英特尔临时联合

英特尔数据中心CPU销量降至14年最低

近年来,英特尔在数据中心CPU市场的表现备受关注。据最新数据显示,由于来自AMD的竞争加剧,英特尔在2024年的数据中心CPU销量创下了十多

贸泽电推出RISC-V技术资源中心

Mouser推出内容丰富的RISC-V资源中心,为设计工程师提供新技术和新应用的相关知识。随着开源架构日益普及,RISC-V从众多选项中脱颖而出,成为开发未来先进软硬件的新途径。从智能

英特尔与谷歌开始为RISC-V进军数据中心铺路

英特尔与谷歌开始为RISC-V进军数据中心铺路

评论