将电阻、电感、电容、传输线、功率分配器/功率合成器和金属互连线等无源元件集成在一个芯片上,从而形成集成无源元件(IPD)。

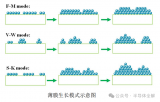

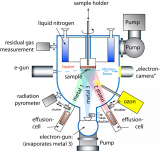

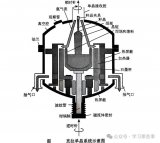

集成无源元件的制备工艺与集成电路制造工艺兼容,主要包括薄膜工艺和光刻刻蚀工艺。集成无源元件可以减小产品尺寸,提高产品性能。 集成电阻形式多样,通常可分为非金属电阳和金属电阻两种。传统意义上,非金属电阻主要用于硅基集成电路工艺,金属电阻在化合物半导体工艺中较为常用。但是,随着硅基集成电路的发展,引入高k金属栅工艺后,金属电阻也被用于硅基集成电路中。非金属电阻是指用半导体材料或多晶硅制备而成的电阻,因半导体材料或多晶硅的摻杂浓度的不同,其电阻率也不同。根据这一特性,利用扩散工艺、离子注人及退火工艺,可以改变半导体材料或多晶硅的掺杂浓度,并通过版图设计得到合适的形状和尺寸,制作所需要的电阻。金属电阻是指利用蒸发或溅射镀膜技术,在绝缘介质上沉积一层金属薄膜,通过光刻刻蚀或剥离(Lift-otf)技术去除多余的金属,从而形成合适电阻值的电阻。常用的金属电阻材料有镍铬合金(NiCr)、氮化钽(TaN)和氮化钛(TiN)等。

集成电容通常分为金属-氧化物-半导体(MOS) 电容、金属-绝缘层-金属(MIM) 电容、pn结电容、叉指结构电容等,可采用半导体加工工艺制备而成。

集成电感分为单匝线圈、多匝线圈、传输线电感。其中,多匝线圈又分为螺旋型和直角型两种。电容、电感通过沉积金属-电镀加厚-湿法刻蚀或干法刻蚀工艺制作,步骤简单,但是需要比较精确的控制,高质量的电容和电感对于滤波、去耦及匹配电路中降低相位噪声起着直接作用。

利用互连线和传输线可以实现芯片上元器件的连接。为了提高芯片的集成度,减小奇生效应,互连线在满足电流密度要求的条件下应尽量窄和短,小电流的互连线制作应选择工艺上能提供的最小线宽,长互连线设计时应考虑互连线带来的延迟效应。当工作领率在微波和毫米波范国时,互连线不可当作纯电阻看待,需要考感寄生参数利趋肤效应的影响。

-

电阻

+关注

关注

88文章

5816浏览量

179950 -

电容

+关注

关注

100文章

6525浏览量

160101 -

无源元件

+关注

关注

1文章

1296浏览量

17531

原文标题:集成无源元件,積體化被動元件,Integrated PassiveDevice (IPD)

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

少模光纤制备工艺:从材料到成纤的全链条解析

2.3DIC集成技术简介

PPI(Passive Plus):高性能射频/微波无源元件领域的卓越领航者

松下工业AEC - Q200无源元件选型指南:为电子设计提供多元选择

金属淀积工艺的核心类型与技术原理

革新科研智造,引领材料未来——高通量智能科研制备工作站

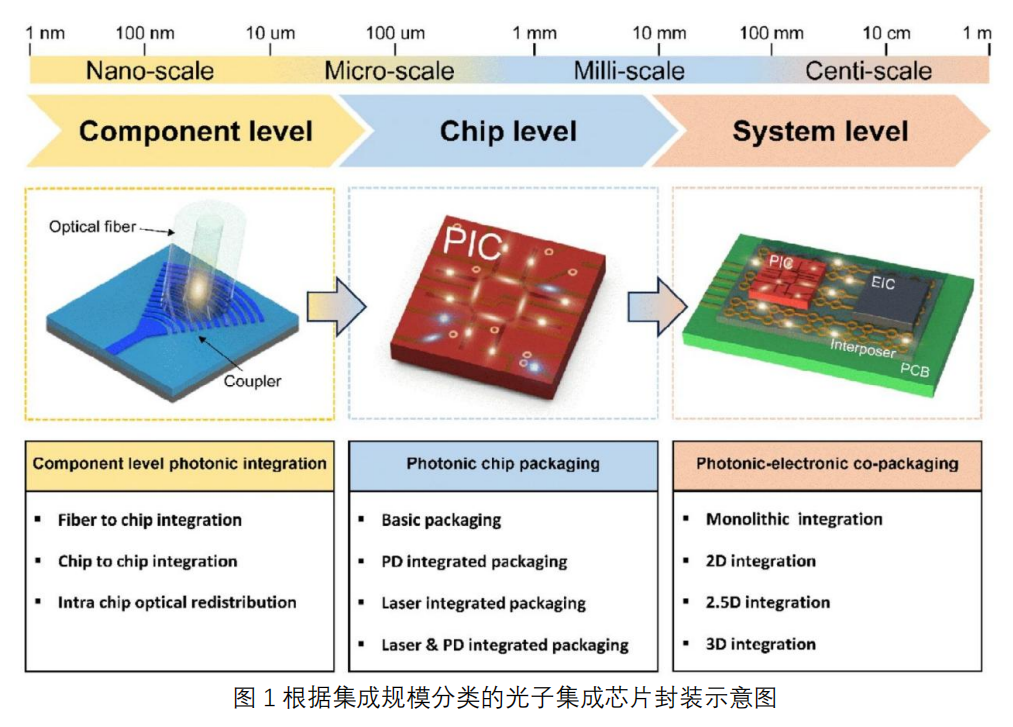

先进PIC光子集成工艺

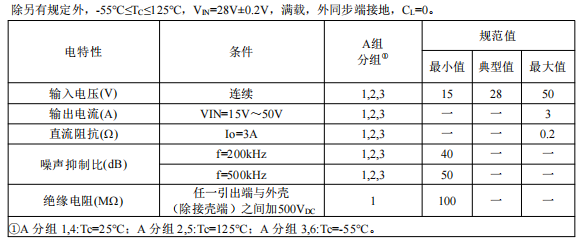

厚膜混合集成EMI滤波器双型号数据对比

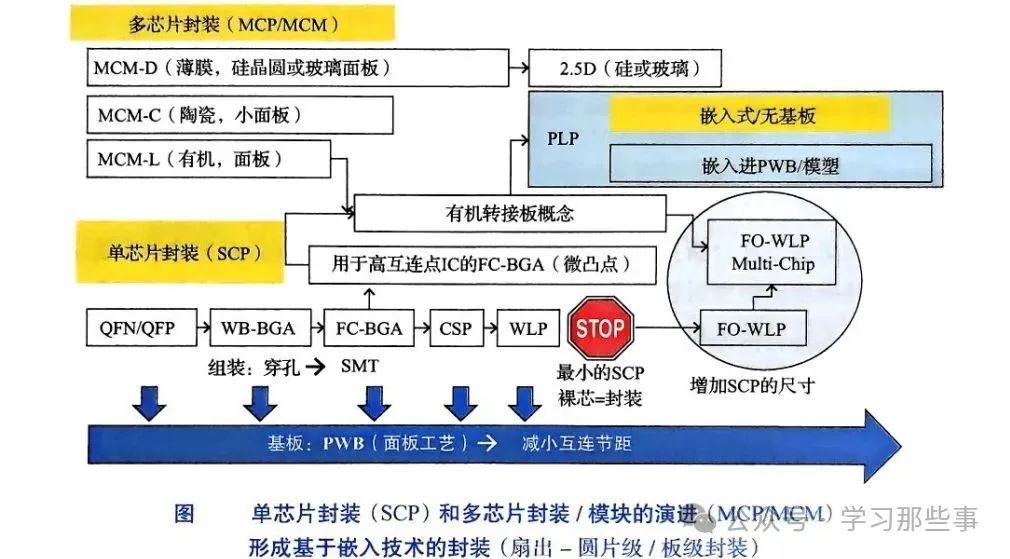

基于板级封装的异构集成详解

Micro OLED 阳极像素定义层制备方法及白光干涉仪在光刻图形的测量

详解原子层沉积薄膜制备技术

集成无源元件的制备工艺

集成无源元件的制备工艺

评论