老师说没电路就不要写代码,但我写个乘法器在综合前都想不出它电路啥样,全加器还行,写Verilog如何做到心中有电路?

首先,你们老师说的是正确的,但可能是说的不够详细,或者你表达的不全。

准确的说,在写Verilog前,要做到心中有数字电路。

数字电路设计主要就是,选择器、全加器、比较器,乘法器,几个常用逻辑门,再加个D触发器,电路基本都能实现了。这些器作为基本单元,对于工程设计来说,并不需要过多的关注它更底层的门或晶体管的样子。

我在学生时代刚开始学数字电路设计的时候,很长一段时间都是眼里只有代码和功能时序,没有一个良好的正向设计思路。比如,知道要实现的功能,二话不说开始新建.v写代码,边写边想,这样导致的结果,准确的来说时序都是调出来的,而不是设计出来的。

写的代码几乎全使用

always @(posedge clk or negedge rst_n)

从不考虑消耗的资源和面积,学生阶段的项目用FPGA也很难把芯片资源用爆,全用的寄存器肯定不会出现时序不满足的情况。

而实际上做设计最应该关注的是PPA(Performance, Power, Area),寄存器多面积必然大,处理必然延时大,功耗怎么小。寄存器打拍是因为组合逻辑路径过长,才往中间插一拍,而不是随便打。

在写Verilog前,不光要心中有电路,还要有关键时序图,有一个硬件的详细设计方案。而且不光在心里,还得写下来,画下来,整理成文档。在动手写代码前,心中就有了谱,清楚的知道,我这个设计能成。

而一个正确的正向设计流程应该是,首先确定设计模块的功能需求,划分整体的硬件结构,可以大致分为几个部分。每一个部分实现一个独立的功能,不同部分之间接口交互确定。

设计分为数据通路和控制通路。

数据通路决定了整体数据流的走向,整个模块计算分为哪几部分,哪些是可以排成流水线,中间的数据流是否需要断掉,用RAM存还是RegFile存储。数据通路中数乘法器单元的面积最大,一般都是采用的是分时复用的方式。整个数据通路的计算流整理出来后,基本上乘法的最大个数也统计出来,然后控制计算模块在不同的时间复用。乘法器的数量和复用程度决定了一个设计是否更优,好的设计是整个数据通路中乘法器几乎空闲不下来。

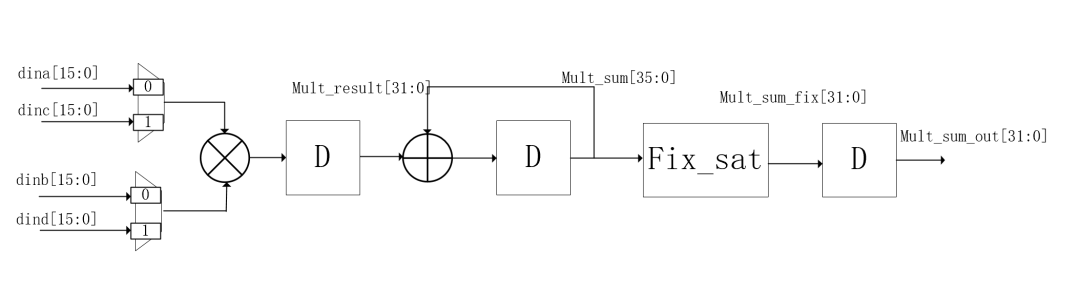

到了单个计算模块,每个模块都能画出一个简单的计算电路图,

上面这个图的意思是,a * b或c * d的结果进行累加,最后饱和截位进行输出。

画出了电路图,就可以大体估算出,整个设计需要的寄存器的数量,乘法器的数据。乘法器和寄存器的量级估算基本上就可以确定整个设计的面积单位量级。

控制通路就是玩时序设计,画出时序图,具体的实现就是各种大大小小的计数器、enable、start、end、valid、flag信号。系统整体的调度,就记住一句话,状态机大法好。当然虽然说状态机可以实现一切时序电路,但并不是所以时序功能都适合用状态机。比如,整个设计的处理都是连续流水处理,那么对于状态机的来说就是一个状态,不需要用状态机了。

控制通路的设计就不是画电路图了,而是画时序图,状态机的跳转,各种控制信号的时序交互,握手,ram的读写控制等等关键时序图,都需要画出来。控制通路上的资源占比很少,一个10bit的计数器就可以计到1023,一个数据打拍就32bit,各种flag就1bit,更不值一提。所以设计中评估资源和优化主要关注的数据通路。

数据通路和控制通路整理完成后,整个设计的处理时间和占用资源基本上就可以估算出来。上面的工作都完成后,然后就是照图施工,你会发现,写代码就完全是个体力活的事情。只要你方案设计的好,图画的好,文档写的清晰,随便找几个会写Verilog的代码都能写出来(夸张的表述)。

回到我们说的Verilog HDL的HDL的全称是Hardware Description language,是硬件描述语言,不是design,是在描述之前,你就得想好要描述的东西。做设计的时候按照这样的思路和套路去想,去做。

再来说说做设计时的描述方式,一些更底层的描述方式,比如

&sel[1:0] 等效于 sel[1:0] == 2'b11

~(|sel[1:0])等效于 sel[1:0] == 2'b0

~a[3:0] + 1'b1 等效于 -a[3:0]

c[4:0] = {a[3], a[3:0]} + {b[3], b[3:0]}等效于c[4:0] = $signed(a[3:0]+b[3:0])

变量乘以一个常数用移位加

assign data_out[5:0] = ({6{data_vld0}} & data0[5:0]) | ({6{data_vld1}} & data1[5:0]) | ({6{data_vld2}} & data2[5:0]) | ({6{data_vld3}} & data3[5:0]);

这是一个4选1的数据选择器,并且要求四个vld不能同时为1。

实际上,抛开代码的可读性,很多代码的写法,并不需要多此一举用更底层的描述方法,高级的描述只要语法和工具支持,就可以直接使用,更底层的描述,我们以为会用更少逻辑,但是工具可能也会优化的更好,比如,变量乘以常数,a * 2‘d3,工具会帮你优化成 a << 2’d1 + a。甚至可能还优化得更好,所以还不如直接用乘法器,*号。

当然也不能过分依赖工具,能复用的逻辑尽量复用,先选后比,先选后加,先选后乘。毕竟自己写出来的逻辑是确定的,而交给工具并不一定会按你想的方向去优化综合。而做一个设计在确保代码功能实现的前提下,还需要考虑的是代码可调试性和可维护性。

最后再扯一段我用过好几次的话

学习Verilog的五个阶段

00:心中无电路,代码无电路

01:心中有电路,代码无电路

10:心中有电路,代码有电路

11:心中无电路,代码有电路

00:心中无电路,代码无电路

达到10就可以了,这时候你就是高手了,再往后就开始玩玄学了。

欢迎纠正,欢迎补充。

审核编辑 :李倩

-

电路

+关注

关注

173文章

6086浏览量

178845 -

寄存器

+关注

关注

31文章

5619浏览量

130419 -

Verilog

+关注

关注

31文章

1374浏览量

114722

原文标题:写Verilog如何做到心中有电路?

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【PCIe 6.0 连载 · 中篇】从设计到实现:高速信号如何做到又快又稳?

高压试验变压器如何做到“免维护”?背后是哪些设计在支撑长期可靠运行?

工业交换机为什么必须支持SNMP?一文讲清它的原理与作用

Verilog HDL语法学习笔记

FPGA 入门必看:Verilog 与 VHDL 编程基础解析!

使用NucleiStudio生成tb仿真需要的.verilog文件

PCIe协议分析仪在数据中心中有何作用?

无感考勤如何做到“无懈可击”?

这款微型MEMS IMU如何做到战术级测量?

海康威视以物联感知和人工智能技术助力水利行业数智化转型

verilog模块的调用、任务和函数

Verilog如何做到心中有电路?

Verilog如何做到心中有电路?

评论