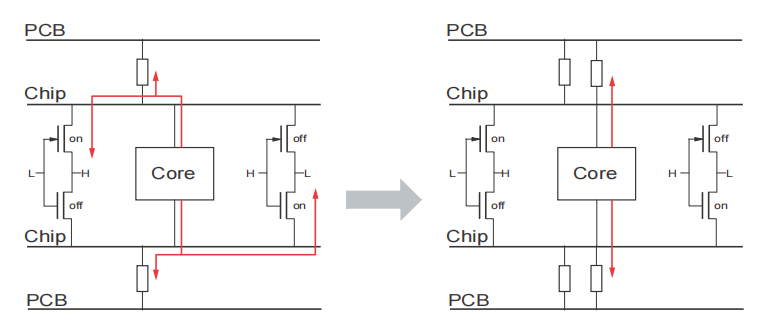

内核到 I/O 口的躁声串扰

任何两个电路在它们的供电时共用同一阻抗,彼此之间将会产生串扰。下例图左边部分说明了核和

I/O 利用同一电源的情况下的核噪声。 这个噪声是由与压降相关的核电流引起的,这里的压降是通过粘

合线和引脚自感引起的,在图 3-3 中,以电阻的形式表示。即使 PCB 的电源电压系统是远离各种纹波电

压,但片内电源也是有躁声的。因为端口缓冲区和内核是同一种内部电源,噪声通过激活的晶体管传递到

每个输出接脚,这不仅影响输出管脚,还影响输入引脚,输入引脚被影响取决于芯片内部的寄生电容(例

如保护电路)。 在对 EME 敏感的情况下,可能需要对每一个引脚滤波,至少对于多引脚的微控制器,这是

基于成本和空间的原因。

共用与隔离电源的串扰

审核编辑 黄昊宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

mcu

+关注

关注

147文章

18652浏览量

388522 -

电路设计

+关注

关注

6732文章

2582浏览量

218190 -

串扰

+关注

关注

4文章

194浏览量

27771

发布评论请先 登录

相关推荐

热点推荐

使用IO口来实现交流检测(AC 220V)

通过IO口可以检测到 50hz 信号,当关闭开关面板瞬间,交流电被断开,交流信号消失,此时驱动端的 MCU 通过IO口读到的是低电平,再上电

发表于 11-19 06:03

在MCU200t板子上蜂鸟E203核的io口的控制方法

只有GPIO这一个变量。

因为我们一直使用的是v2版本,对v1版本不了解,这里就只介绍v2版本的io口控制,欢迎有用过v1的同学进行补充。

我们的板子型号是MCU200t,GPIOA已经跟

发表于 10-31 07:17

高速AC耦合电容挨得很近,PCB串扰会不会很大……

串扰大是肯定大的啦!但是设计工程师也很委屈啊:芯片互联动不动就有一百几十对高速信号的AC耦合电容, 首先我得都塞进PCB板去啊,其次的串扰那都是其次了……

NEXT(Near-End Crosstalk,近端串扰)

一、什么是NEXT(近端串扰)? NEXT(Near-End Crosstalk,近端串扰)是指在线缆传输信号时,靠近发射端处,相邻线对之间因电磁干扰所产生的

MCU是否可以使用普通IO口和数据总线控制cy7c68013a,用异步slavefifo模式增加一个与PC通信的USB口?

cy7c68013a的固件已经配置成异步slave模式,是否有MCU用IO口控制cy7c68013a通过数据总线来实现与PC的USB口通信,这样应用的示例程序或教程?

目的就是在现

发表于 05-30 06:32

OLI-P——分布式偏振串扰测量利器

在保偏光纤系统中,偏振串扰是导致性能劣化的核心因素之一。传统偏振检测手段仅能获得链路整体消光比,而分布式偏振串扰测量通过连续、高精度地捕捉整条光纤链路的偏振耦合分布,成为保障系统可靠性

电子产品更稳定?捷多邦的高密度布线如何降低串扰影响?

在高速PCB设计中,信号完整性、串扰、信号损耗等问题直接影响电路板的性能稳定性。随着5G通信、服务器、高速计算、汽车电子等行业对高频、高速信号传输的需求增加,如何优化PCB布线以降低**信号衰减

ADC电路的串扰怎么解决?

,ADC是SAR型 18位单通道全差分输入的ADC。ADC的后端是MCU,MCU将数字信号处理之后再画到显示屏上显示实时波形。

调试发现显示的信号有串扰,表现为某一路信号悬空之后,相

发表于 01-07 06:15

MCU—IO口的噪声串扰

MCU—IO口的噪声串扰

评论