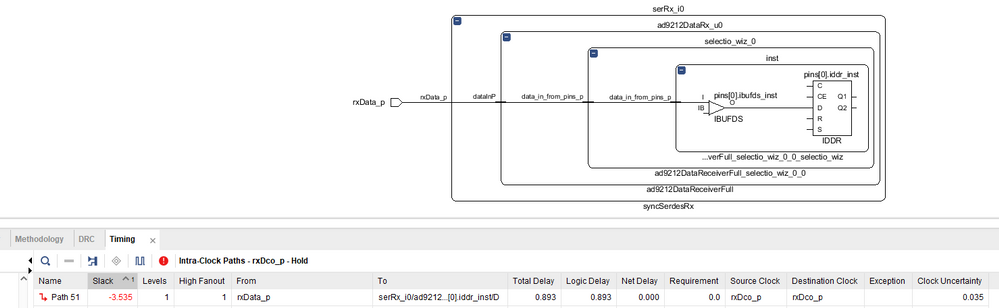

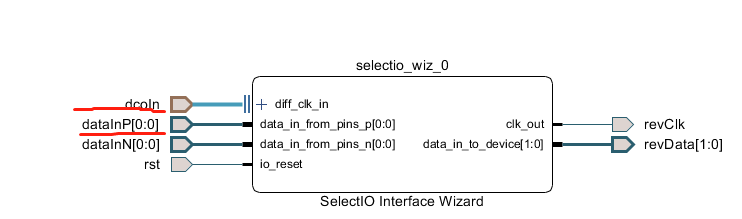

Q:使用 zynq 器件, select io 解码串行数据, data 和 clock 直接进入, 未进行其他处理, 综合有关于 data 保存时间的时序错误, 请问什么问题? 实测接收功能基本正确

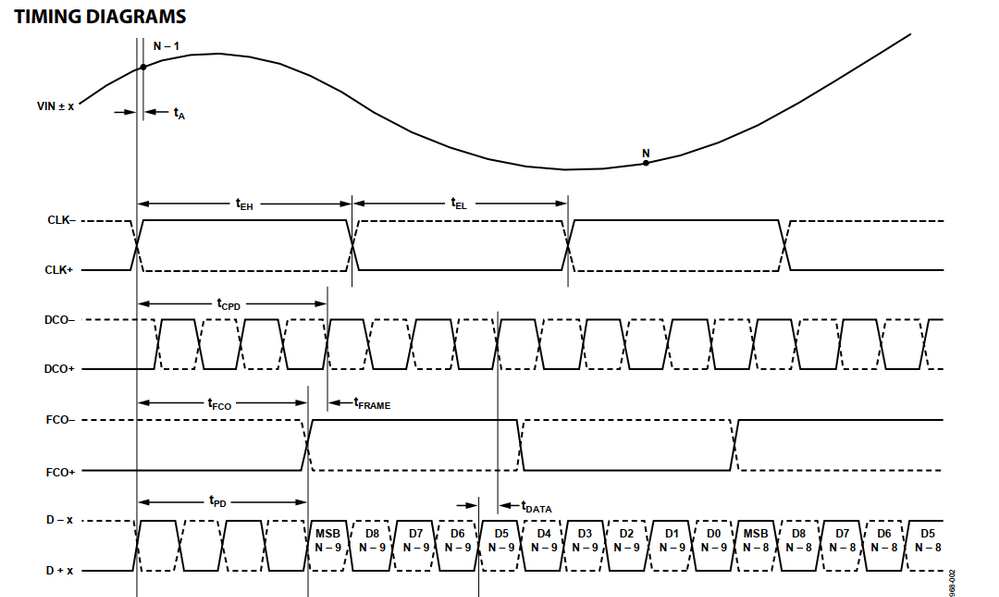

器件时序, 约束采用的是其中的 tframe = 1.3 - 1.9ns

约束:

set_input_delay -clock [get_clocks rxDco_p] -clock_fall -min -add_delay -1.300 [get_ports rxData_n]

set_input_delay -clock [get_clocks rxDco_p] -clock_fall -max -add_delay -1.900 [get_ports rxData_n]

set_input_delay -clock [get_clocks rxDco_p] -min -add_delay -1.300 [get_ports rxData_n]

set_input_delay -clock [get_clocks rxDco_p] -max -add_delay -1.900 [get_ports rxData_n]

set_input_delay -clock [get_clocks rxDco_p] -clock_fall -min -add_delay -1.300 [get_ports rxData_p]

set_input_delay -clock [get_clocks rxDco_p] -clock_fall -max -add_delay -1.900 [get_ports rxData_p]

set_input_delay -clock [get_clocks rxDco_p] -min -add_delay -1.300 [get_ports rxData_p]

set_input_delay -clock [get_clocks rxDco_p] -max -add_delay -1.900 [get_ports rxData_p]

A:应该是 set_input_delay 约束写错了

参考 vivado language template 的话,这个 data 接口符合 source synchronous--> center aligned --> DDR 的模板

其中参数

dv_bre = dv_bfe = 1.3ns

dv_are = dv_afe = (1/2 period - 1.9)ns

所以约束里的

-max 值是(1/2 period - 1.3)

-min 值是(1/2 period - 1.9)

Language template在 vivado 图形界面 tools 菜单里。

关于 template 的介绍,可以先学习 inputdelay/output delay 的理论基础,结合实践琢磨一下,这套 template 使用的方法还是有点巧妙的

经验是通过时序图对比,找到最匹配的 template,确定里面对应参数的值,套用 template里面的约束模板就可以。

可以找出这个 source synchronous --> centeraligned --> DDR 模板,看里面的时序图跟用户手册里的时序图对比下

时序图里没有画出 data 有效数据跟无效数据(就是阴影部分)的范围,但 tFRAME 的值之所以是 1.3~1.9,就是因为 data 有有效数据跟无效数据范围的原因,把时序图的有效数据和无效数据范围画出来,就容易跟 template 里的时序图进行匹配了。

审核编辑 :李倩

-

串行

+关注

关注

0文章

256浏览量

35188 -

Data

+关注

关注

0文章

63浏览量

39031 -

模板

+关注

关注

0文章

110浏览量

21021

原文标题:本周一问 | Select io 解串行数据, 时序约束不通过问题

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

电能质量在线监测装置的相序错误记录功能可以保存多久?

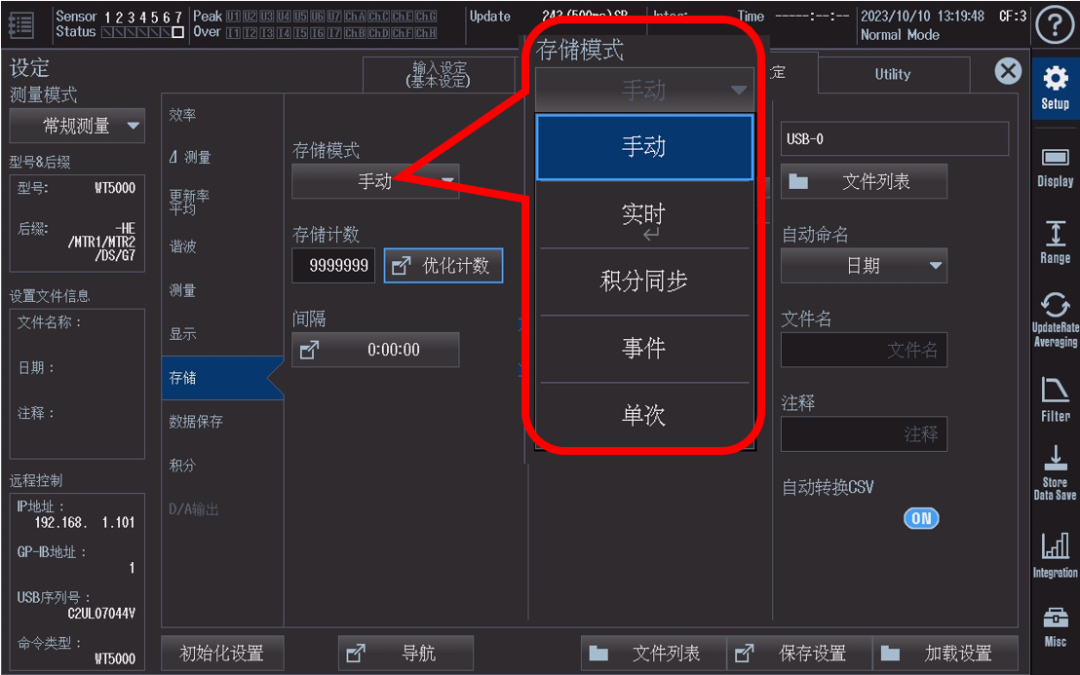

功率分析仪的“存储”与“数据保存”模式如何保存测量数据呢?

HarmonyOS实战:一招搞定保存图片到相册

如何自动测量CAN收发器的延迟时间?

如何将dif_time打印到 uart 或将其保存在文件中?

FPGA时序约束之设置时钟组

一文详解Vivado时序约束

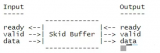

AXI握手时序优化—pipeline缓冲器

求助,关于ADC124S021的时序疑问求解

ADMV9625: 60 GHz Millimeterwave Short Data Link Preliminary Data Sheet adi

MAX17853: 14-Channel High-Voltage Data-Acquisition System Data Sheet adi

关于data保存时间的时序错误

关于data保存时间的时序错误

评论