DDR 内存正在迅速成为不仅是领先技术,而且是内存设计中唯一使用的技术。因此,DDR 系统在科技行业的需求量很大。与原理图和 PCB 设计软件集成的高速仿真工具可以为设计人员提供广泛的强大功能,以帮助完成整个 DDR 设计过程。从建立布局前约束到自动布线技术和布局后验证,这些工具消除了设计过程中的猜测,同时让工程团队确信他们的系统将按预期运行。

将用于此 DDR 演示的设计是 SiFive 的 HiFive Unleashed、基于 RISC-V 的开发板。除了几个其他接口和功能外,该板还具有 8 GB 的带 ECC 的 DDR4。

在原理图中,两个差分选通网络以及一条数据总线上的四个数据网络可以直接导出到 HyperLynx LineSim 进行布局前仿真(图 2)。借助 HyperLynx DDR 中的广泛功能,使用组件 IBIS 模型模拟真实世界的场景使工程师能够在布局电路板之前确定和优化传输线行为。供应商通常为 DDR 控制器和用于 I/O 行为建模的 DRAM 组件提供 IBIS 模型。

图 2:四个数据网络和差分选通网络可以从原理图工具中导出到 Linesim

在 LineSim 中,数据和选通网络的引脚和映射已自动从其原理图符号中继承。然后,除了来自组件 IBIS 模型的驱动强度和 ODT 值之外,工程师还可以分配控制器的特定引脚缓冲区数据。在这种情况下,具有 48 欧姆终端值的中等驱动强度将用于预期目的。一旦引脚被分配并指定为输入或输出,它们的 LineSim 符号将准确反映缓冲区方向和引脚名称(图 3)。

图 3:网络及其相关缓冲区显示在 LineSim 中

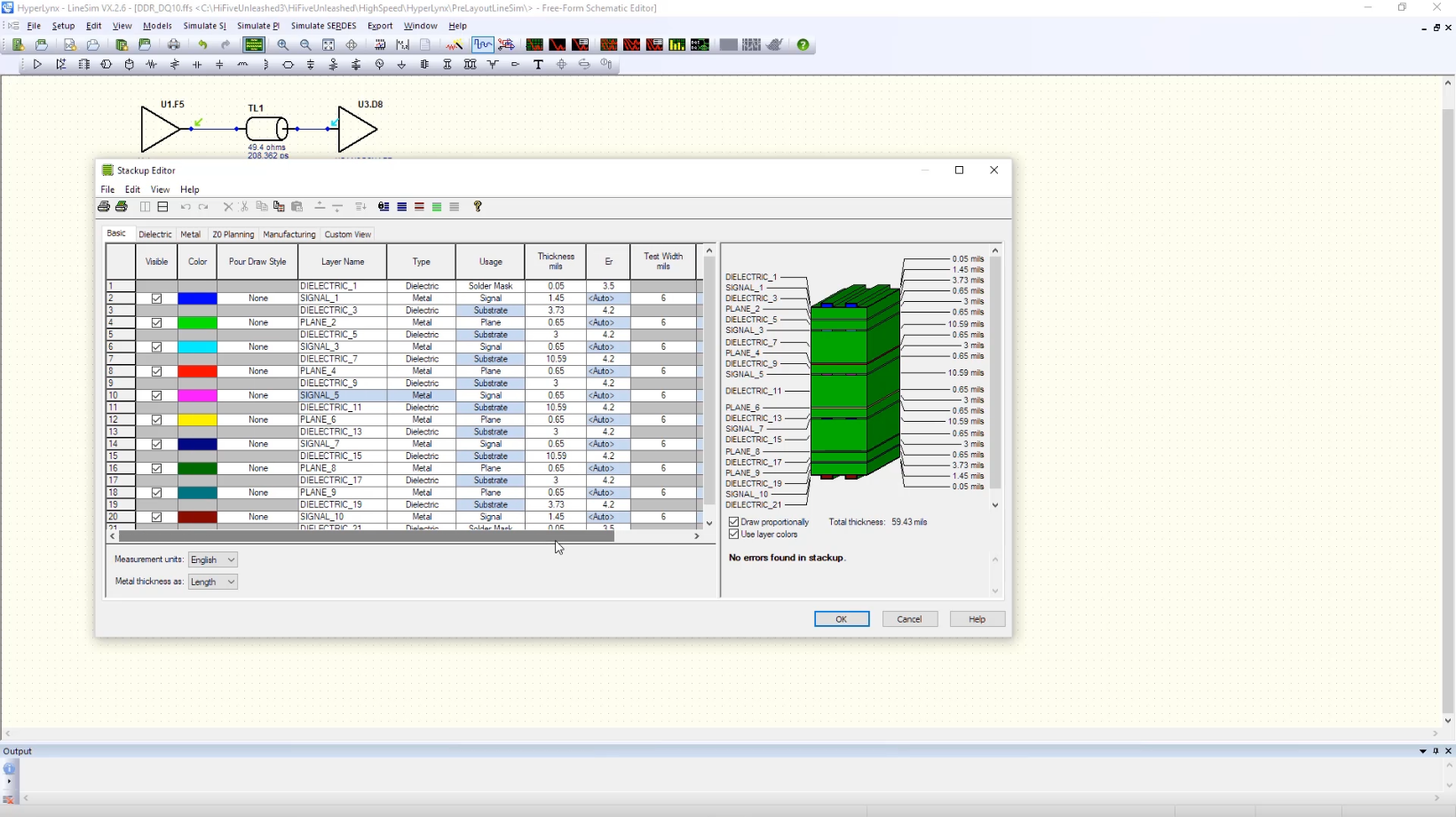

除了材料的介电常数外,层厚还会对电子元件的功能产生重大影响,尤其是在高频下。工程师能够在 HyperLynx 中创建层堆叠并计算信号、平面和电介质数据(图 4)。布局前 DDR LineSim 中的堆叠功能允许了解此信息将如何影响阻抗值和信号行为。

图 4:叠加编辑器可以帮助确定初始叠加数据

可以创建耦合区域以帮助规划和可视化潜在的信号放置和分组,以及确定走线阻抗和耦合距离。这些区域在对走线长度、宽度和间距运行仿真扫描时很有用,以便为布局约束找到可接受的参数。在这个例子中,工程师创建了两个耦合区域:一个用于数据网络,一个用于选通网络。将差分迹线添加到其耦合区域后,可以调整宽度和间距参数以微调值,同时确保满足阻抗容差(图 5)。在此示例中,电路板将被密集封装,因此工程师将尝试最小化走线宽度和间距,同时仍保持接近 100 欧姆差分阻抗规范。

图 5:LineSim 中选定耦合区域的迹线宽度和间距值可视化

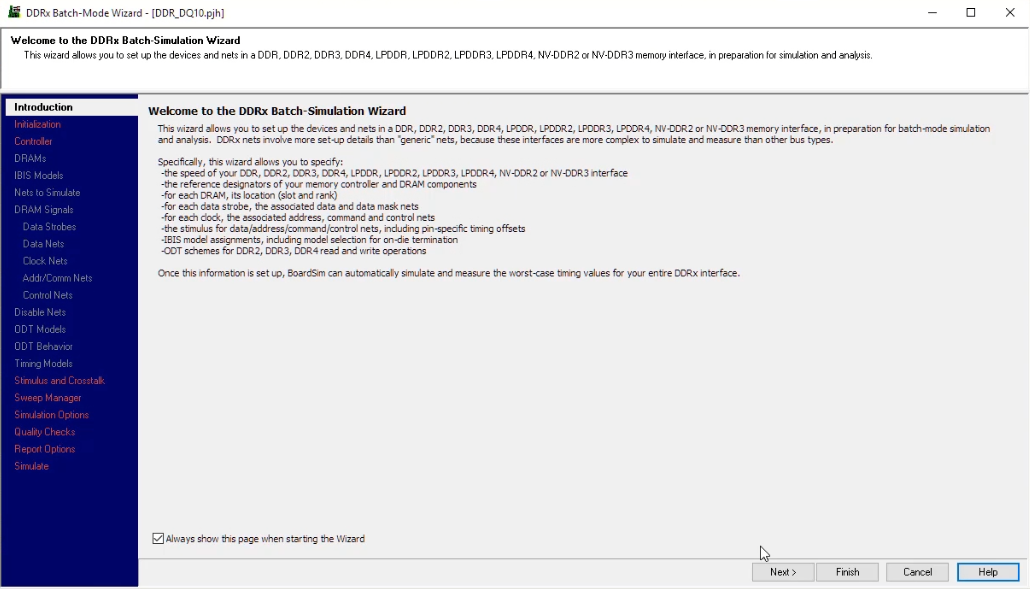

一旦分配了组件模型和耦合区域,网络就可以进行仿真了。DDRx 向导引导用户逐步完成设置过程(图 6)。首先,必须在“初始化”页面上指定 DDR 接口的类型以及数据速率。接下来,控制器和 DRAM 设备必须使用“控制器”和“DRAM”页面上的相应参考标志来分配。在选择 DRAM 时,用户还会注明插槽数和等级。插槽代表设计中存在的 DIMM 模块的物理数量。由于此设计没有可拆卸的 DIMM 模块,因此将有零个插槽。板上的板载 DRAM 模块只有一个芯片,对应一个等级。

图 6:DDRx 向导引导用户逐步完成设置过程

因为工程师最初对确定物理网络参数将如何影响数据网络上的时序感兴趣,所以在“要模拟的网络”页面上只选择“数据时序”部分。如果需要,还可以使用模拟偏斜时序以及地址和命令时序的选项。几乎所有 DRAM 供应商都遵循通用命名约定以遵守 JEDEC 标准。DDRx 向导使用此标准约定来自动确定“DRAM 信号”页面上的 DDR 内存总线信号。只需要模拟一个数据网即可找到初始时序信息,因此可以在“禁用网络”页面上禁用除一个网络之外的所有网络。片上终端是内置在 DRAM 硅中的动态终端电阻,用于阻抗匹配。不同的 ODT 设置会对信号质量产生很大影响。在“ODT 模型”页面上,可以选择源自 IBIS 模型的控制器和 DRAM 设备的动态 ODT 值。“刺激和串扰”页面允许用户在检查 SI 损伤时控制运行多少伪随机序列。为了更快的仿真运行时间,可以使用更小的位模式。为了获得更准确的结果,可以使用更长的位模式。

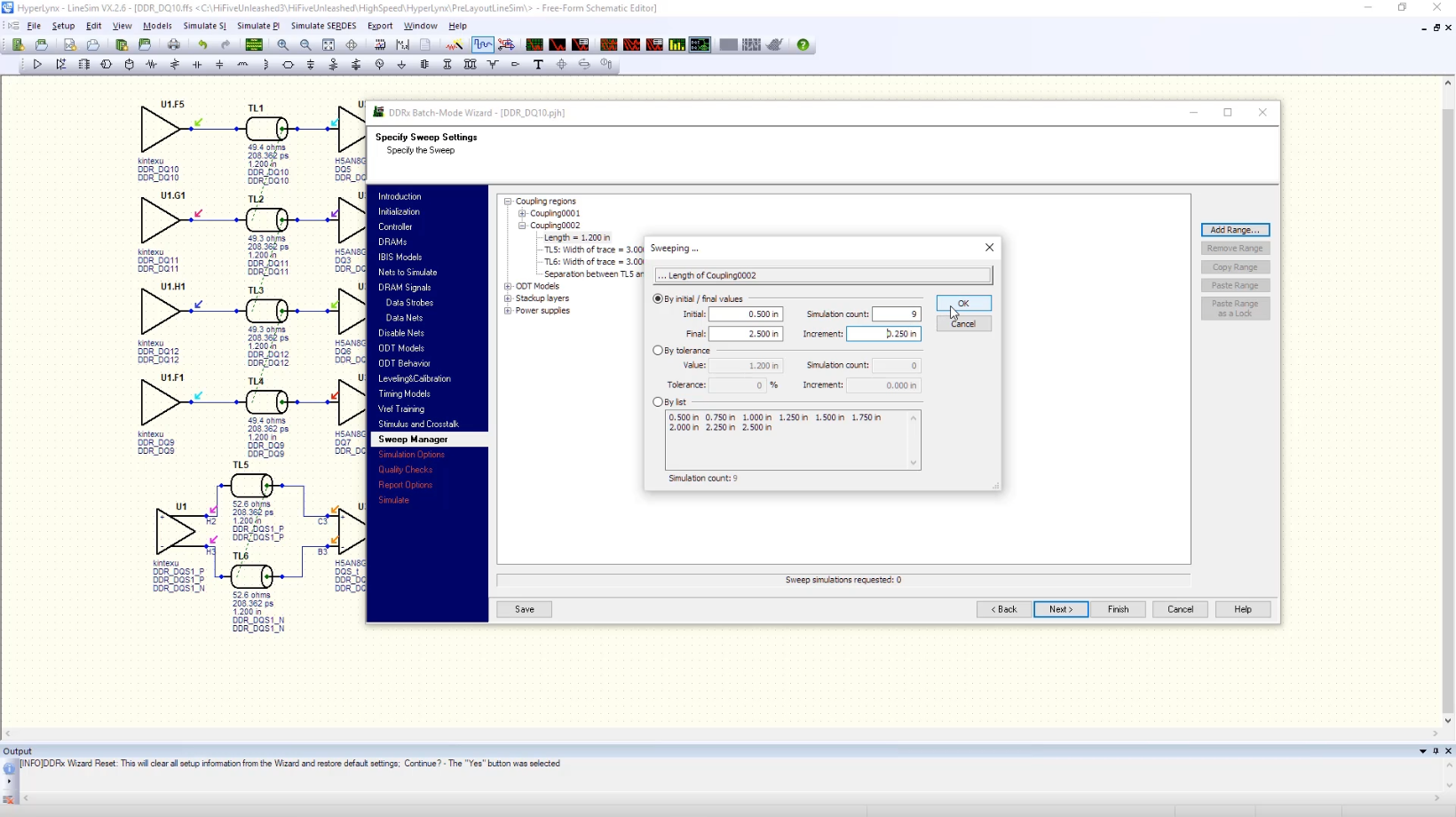

布局前仿真 DDRx 向导允许用户设置扫描以确定一系列值将如何影响信号行为。在这种情况下,工程师希望了解不同选通网络长度对数据信号质量的影响。在“Sweep Manager”页面上选择差分耦合区域,可以指定从半英寸到两英寸半的长度范围,增量为四分之一英寸(图 7)。这些值是根据大约 1.2 英寸的初步数据净长度选择的。

图 7:可以设置扫描以模拟不同的频闪网长度

模型角可以为IC在典型或极端参数值下的性能提供有价值的见解。通过在“模拟选项”页面上仅选择快速和慢速模型角点,工程师可以深入了解信号在两种极端情况下的表现。如果他们在这些条件下通过考试,那么他们可以在典型情况下通过考试。在其余的设置阶段,不需要调整太多其他内容。一旦启动模拟,模拟器将逐步完成先前定义的9次扫描中的每一次。完成后,输出HTML报告将显示每次扫描的结果。红色单元格和通过表示失败,绿色单元格表示失败。在写入命令期间,很明显,在大多数情况下,当差分选通长度低于四分之三英寸或超过四分之一英寸(图8)时,会发生故障。这表明数据网络和选通网络之间存在大约正负半英寸的可接受长度差异。read命令模拟相同的响应。

图 8:输出 HTML 报告显示每次扫描是通过还是失败

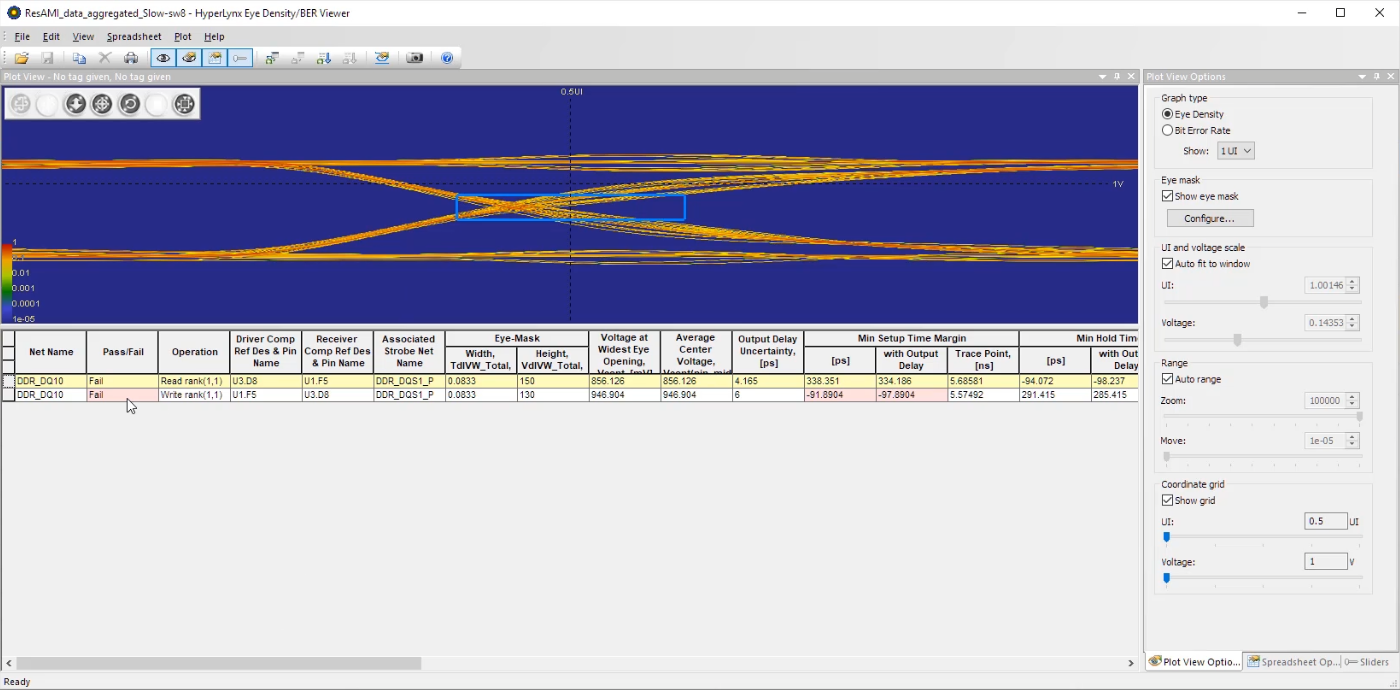

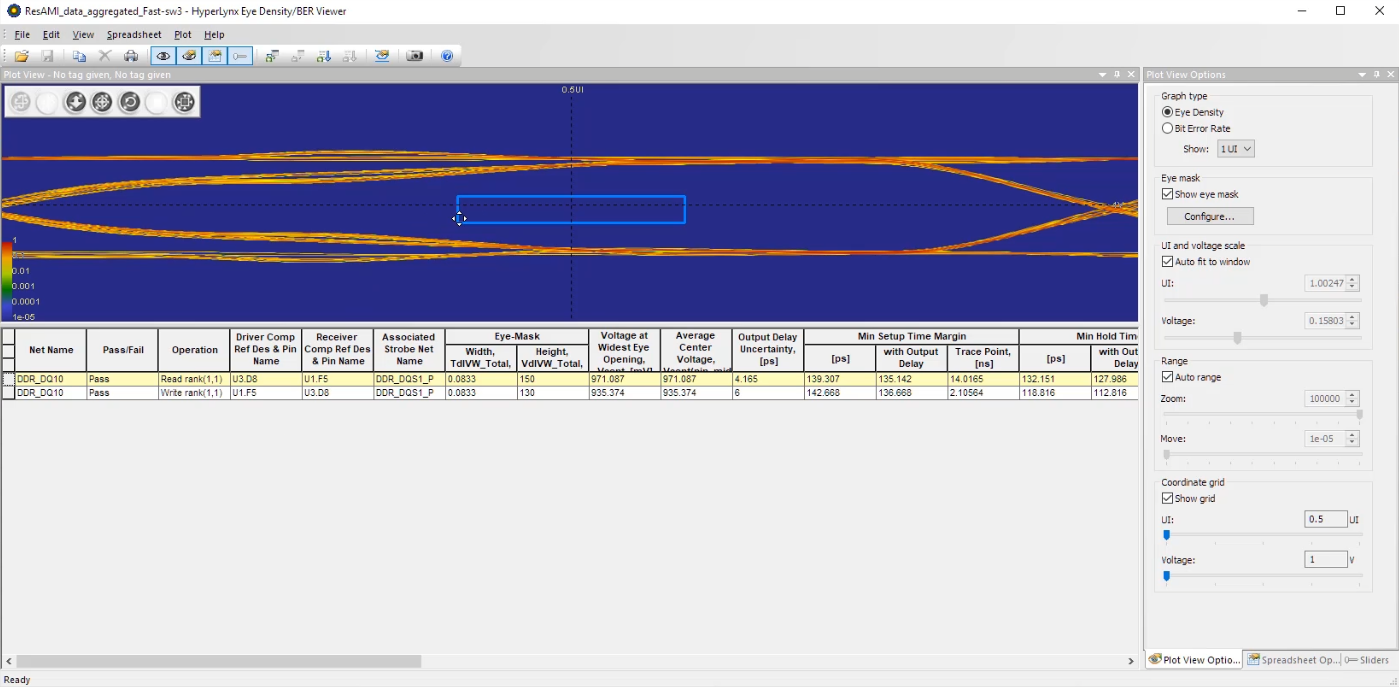

可以查看每个扫描的眼密度链接以便更好地进行比较。图中的眼图模板考虑了 DQS 边缘变化并自动放置。第一个图表(图 9)显示了大于 2 英寸的差分频闪网长度。第二个图(图 10)显示了可接受长度参数内的选通长度。这两个图表显示了通过和失败之间的明显区别。

图 9:当差分选通网络长度大于 2 英寸时显示信号复杂性的眼图

图 10:眼图显示明显更好的信号质量和可接受的差分选通网络长度

回到 LineSim,工程师在原理图中添加了两个地址网络(图 11)。这种布局使用翻盖技术来节省空间。这种布线拓扑结构是通过放置通孔来实现从引脚到内部走线层的层变化。还为位于同一内层的地址网络的每个段创建了耦合区域,包括耦合到数据网络的段。

图 11:LineSim 示意图中显示的地址网络和相关耦合区域

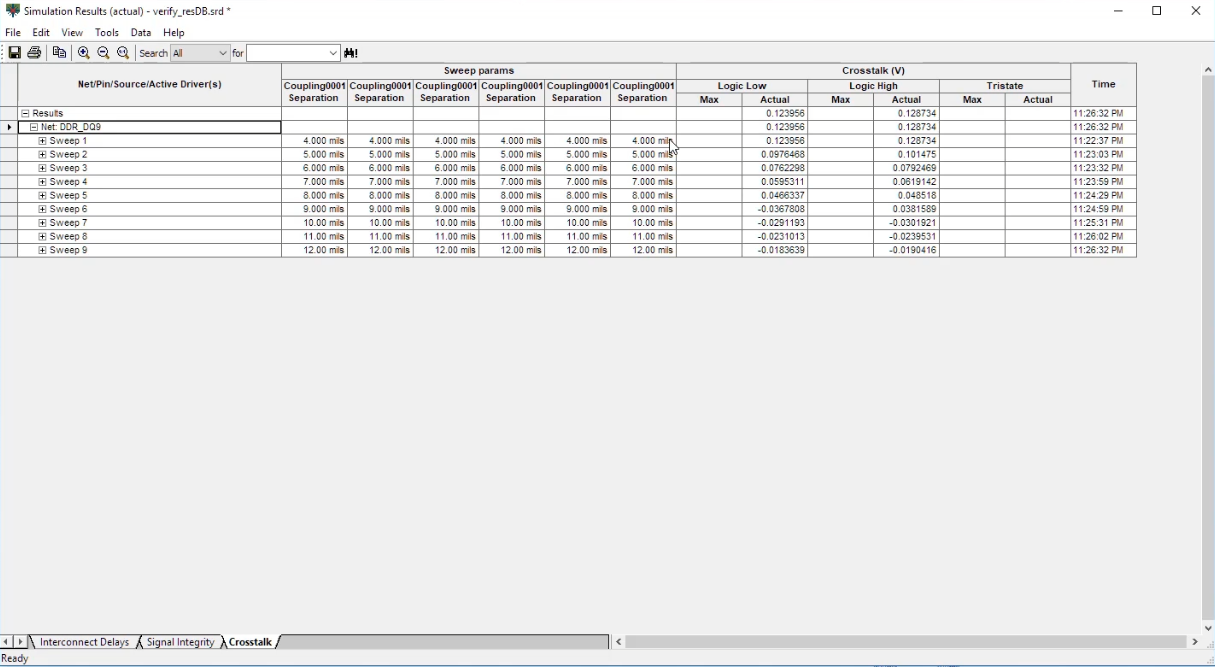

工程师将运行交互式模拟,而不是运行另一个批量模拟,以查看来自地址网络的受害数据网络上的串扰。要了解走线间距如何影响串扰结果,地址和数据网络之间的宽度可以从 4 mil 扫描到 12 mil。通过将数据位 9 识别为受害者,可以确定附近攻击者网络在该特定迹线上引起的噪声量。然后可以将这些发现纳入布局实践中。仿真完成后,结果显示,当走线间距为 4 mil 时,串扰水平最高(图 12)。然而,即使看到的最高串扰量也约为 120 mV,这对于性能来说可能是可以接受的。如果电平开始达到 150 mV 以上,

图 12:串扰仿真结果表明,最高水平的串扰发生在走线间距为 4 mil 的情况下

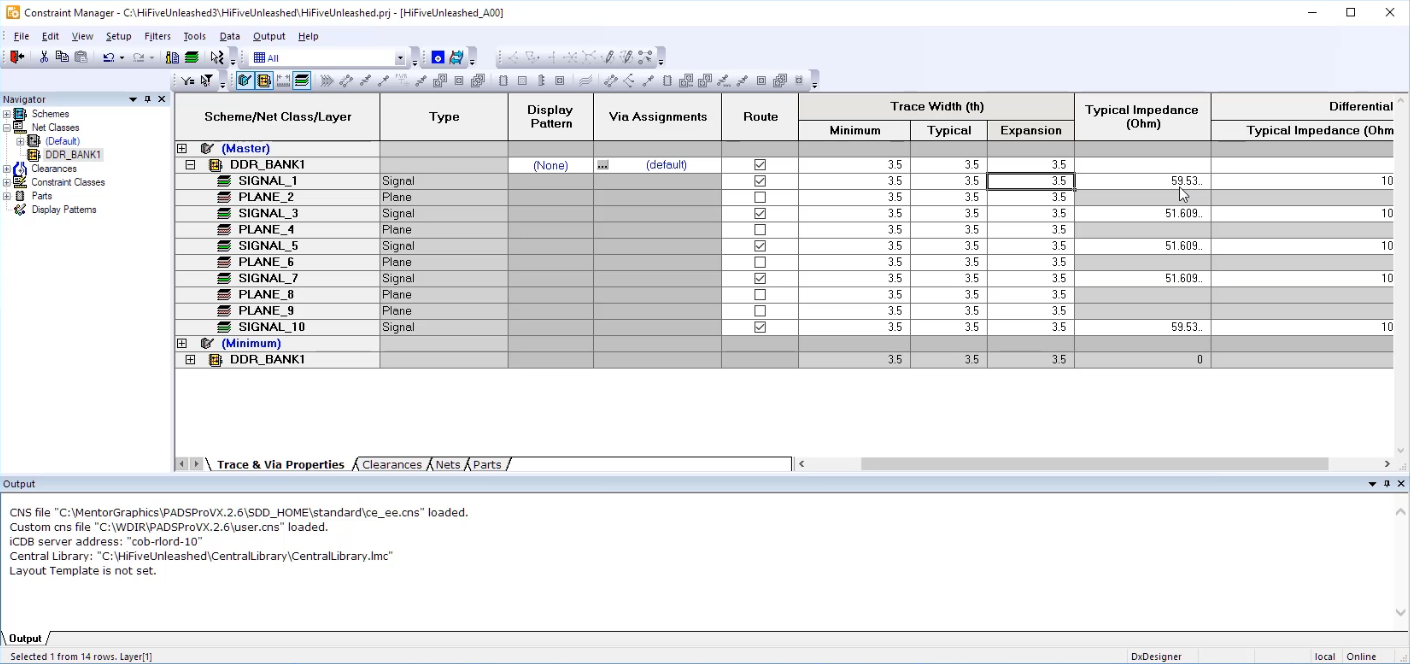

利用从运行这些布局前仿真中发现的信息,工程师可以使用原理图工具中的约束管理器创建初始约束。约束管理器允许用户创建网络类、间隙规则和约束类,以确保满足物理布局和布线要求。可以创建网络类来定义指定网络的宽度和间距要求。工程师创建了一个名为“DDR_BANK1”的网络类,其中包含单个 DRAM 模块的数据和数据掩码网络。考虑到来自叠层的介电和阻抗信息,数据和数据掩膜网络的宽度应约为 3.5 密耳,以将单端阻抗值保持在 50 欧姆左右。输入值后,约束管理器会根据迹线宽度显示近似阻抗值(图 13)。顶层和底层阻抗不会那么重要,因为位于这些层上的走线的唯一部分将是设备引脚的扇出。一旦在约束管理器中定义了参数,布局工具将要求在布局和布线时遵守这些约束。可以从原理图和布局工具访问约束管理器,以便工程师和布局专家之间的简单协作,以及动态编辑。一旦在约束管理器中定义了参数,布局工具将要求在布局和布线时遵守这些约束。可以从原理图和布局工具访问约束管理器,以便工程师和布局专家之间的简单协作,以及动态编辑。一旦在约束管理器中定义了参数,布局工具将要求在布局和布线时遵守这些约束。可以从原理图和布局工具访问约束管理器,以便工程师和布局专家之间的简单协作,以及动态编辑。

图 13:输入迹线宽度值后,约束管理器会计算阻抗值

可以创建间隙规则来定义网络、组件和电路板对象之间的物理间隙约束。约束类允许用户将具有相同或单独的网络类分配的网络组合在一起,同时还允许向每个网络添加物理要求。除了 DRAM 的单个约束类别外,工程师还为数据和选通网络创建了单独的清除规则。约束类将包含数据库的所有数据、数据掩码和选通网络。一旦创建了约束类,并添加了适当的网络,就可以为这些网络定义许多物理参数,包括阻抗容差和长度匹配要求。LineSim 模拟表明选通网络必须在数据网络的半英寸范围内匹配,可以在约束类中定义。此外,工程师希望确保数据和数据屏蔽网络的长度在 200 mil 范围内匹配(图 14)。

图 14:数据和数据掩码网络的长度应在 200 mil 范围内匹配,该范围在约束管理器中定义

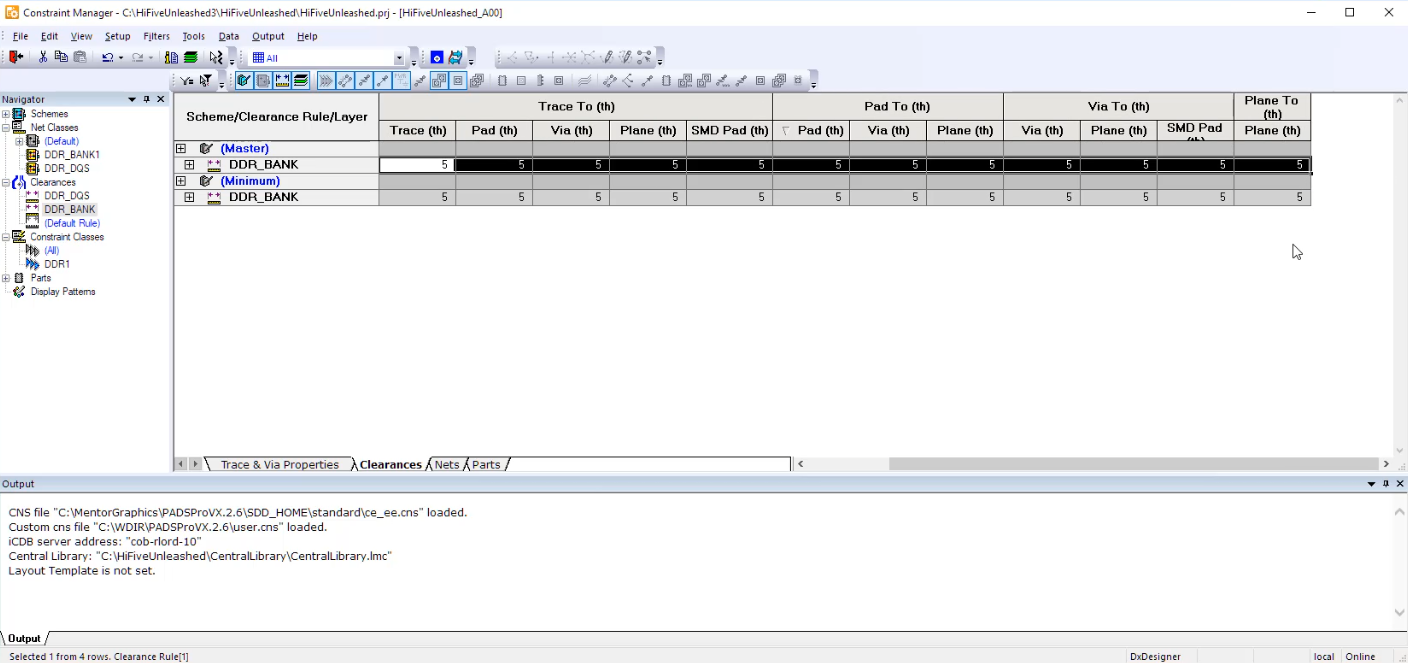

串扰仿真结果确定,即使数据网之间的间距为 4 mil,串扰水平也应在合理范围内。为了安全起见,工程师已将间隙规则要求设置为 5 mil 间距阈值(图 15)。如果执行额外的模拟计算,还可以应用更精确的走线、焊盘和通孔之间的间隙值。类间间隙矩阵允许用户指定在网络类之间应用哪些间隙规则。

图 15:约束管理器中定义了 5 mil 间隙阈值

分配了初始网络约束后,设计人员就可以为适当的 DRAM 布线。对于这种布局,SoC 被放置在电路板的中间,DRAM 模块就在它的下方。每个组件引脚的扇出已放置在顶层和底层。此 DRAM 的其余网段将在第 5 层布线。在 Net Explorer 面板中,选择 DDR1 约束类将突出显示网络的引脚连接(图 16)。

图 16:在 Net Explorer 中选择先前定义的 DDR1 约束类将突出显示引脚连接

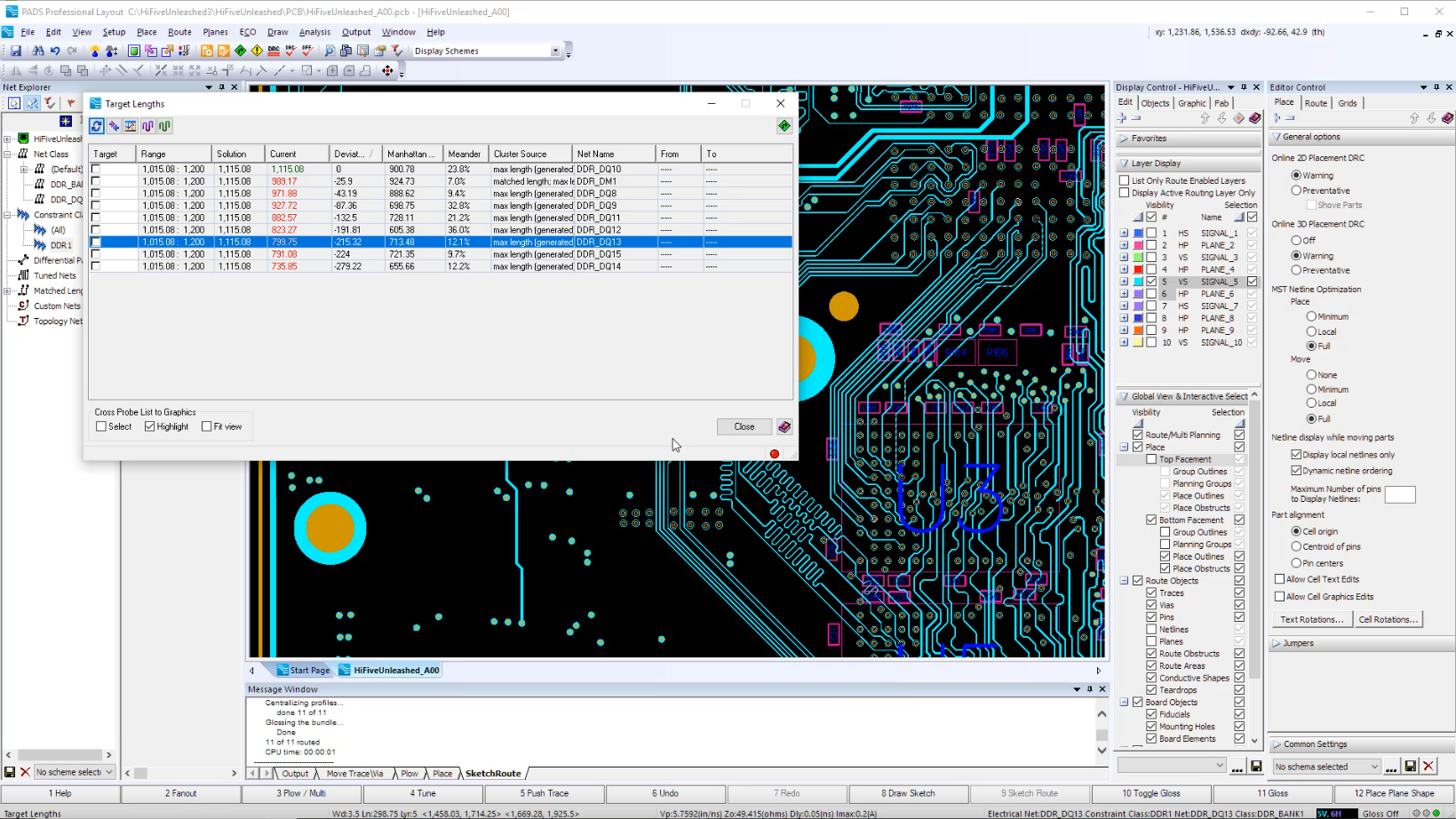

现在,设计者只需选择约束类,按键盘上的 F8 键打开草图布线,用鼠标绘制他们想要的布线路径,工具将自动布线。右键单击其中一个路由数据网络并选择目标长度,可以轻松查看匹配组中每条迹线的实际长度值(图 17)。这有助于可视化走线是否在工程师之前设置的 200 mil 长度匹配约束范围内。很明显,走线长度不符合指定要求,因此设计人员可以使用自动调谐功能快速蛇形匹配该组中的所有走线信号。

图 17:Target Lengths 功能使用户可以清楚地看到他们的走线长度是否调整正确

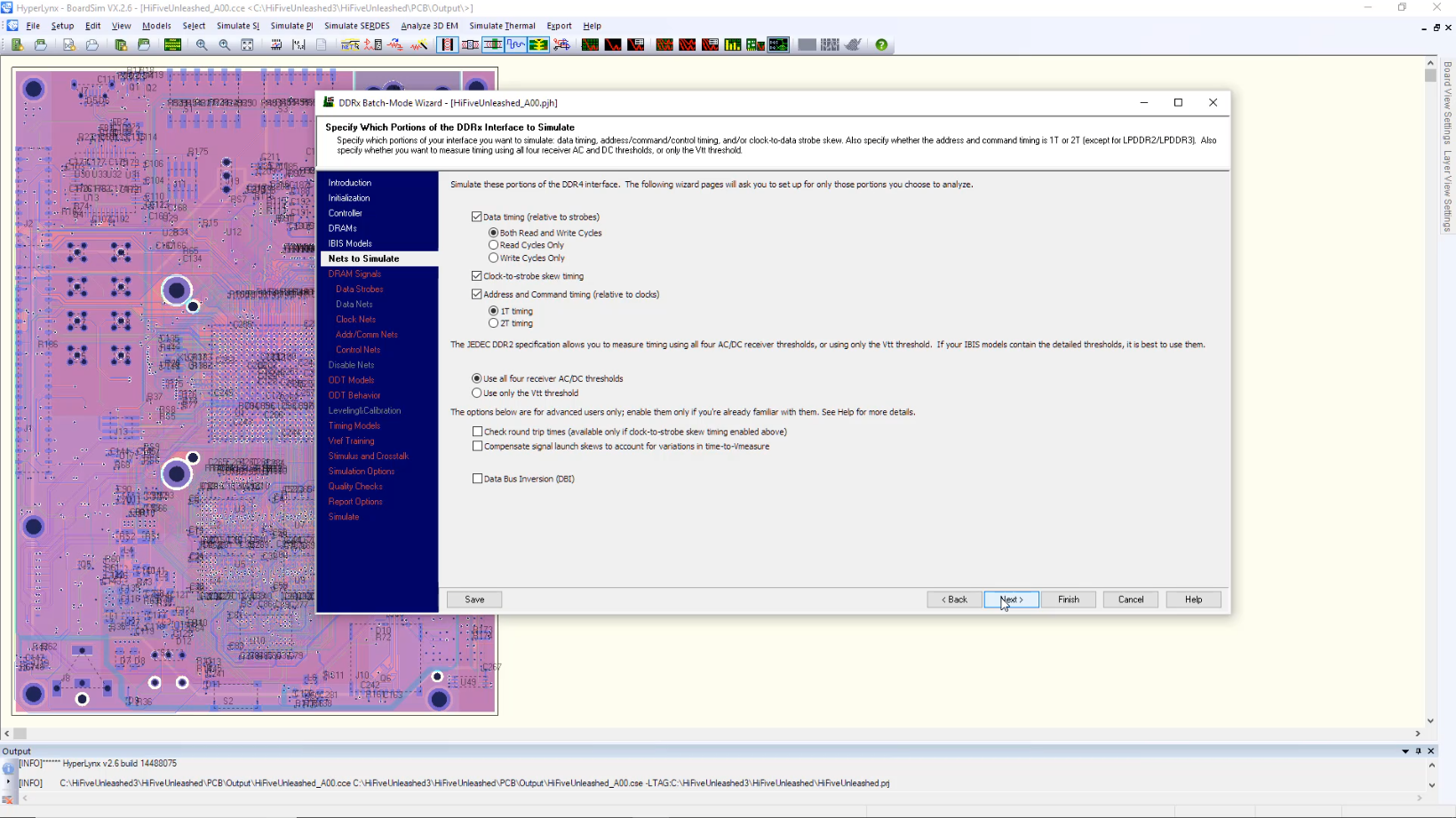

接口正确布线后,用户可以将布局直接导出到 HyperLynx DDR 以进行布局后分析。运行布局后分析的目的是验证电路的正确功能和完整性。布局后仿真将考虑网络和叠层的实际长度和阻抗值,以及来自相邻走线和组件的影响。加载 HyperLynx BoardSim(图 18)后,设计人员将首先启用信号之间的耦合效应、信号与区域填充之间的耦合效应以及损耗效应,以更准确地预测信号行为。通过布局后 DDR 分析,用户可以运行交互式仿真和批量仿真,以全面了解系统功能。交互式仿真期间生成的示波器视图将为单独选择的网络提供真实的波形和值。对于此演示,将仅显示批量模拟。

图 18:HyperLynx BoardSim 布局后工具视图

在布局后的 DDRx 向导中,工程师最初会指定此接口为 DDR4,传输速率为每秒 2400 兆。接下来,必须分配控制器组件。这一次,在分配内存组件时,工程师将选择所有 9 个 DRAM。由于整个 DRAM 接口已布线,因此可以通过模拟数据时序、时钟到选通信号偏斜以及地址和命令来收集重要的功能信息(图 19)。在这种情况下,感兴趣的网络是地址网络之一以及刚刚路由的数据和选通信号。用于布局前模拟的相同 ODT 设置也将在此处应用,但重要的是运行具有不同 ODT 值的多个模拟。

图 19:从布局后仿真中提取的时序信息可以对电路性能提供有价值的洞察

内存控制器本身必须在运行中补偿时钟和选通信号之间的偏差。它通过在必要时添加适当的延迟来实现这一点,称为写入均衡。The DDRx Wizard can account for write leveling during simulation when the checkbox on the “Leveling and Calibration” page is selected. 默认 DRAM 时序模型符合 JEDEC,但控制器模型应特定于设计的控制器设备。时序模型向导可以从“时序模型”页面启动,用于根据供应商时序参数设置和创建自定义时序模型。模拟快速和慢速模型拐角可为最极端的情况提供性能信息。HyperLynx DDR 中提供的定制级别允许用户创建高度特定于设计的参数和限制,

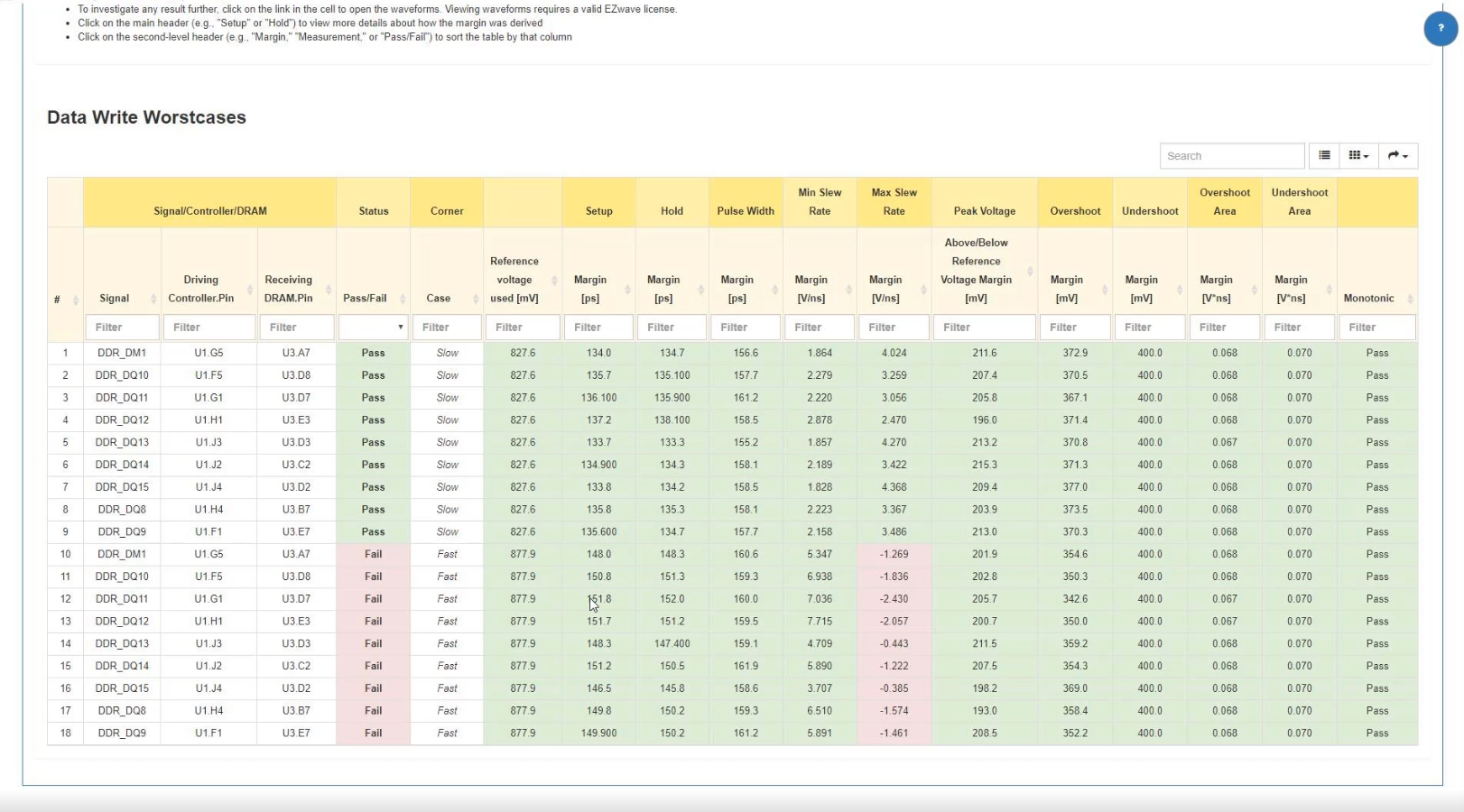

一旦模拟完成,HTML报告表明,对于慢速模型转角情况,数据写入命令将传递给所有网络,但快速模型转角情况无法达到最大转换速率裕度(图20)。可能需要进一步研究这些误差,并进行额外的模拟。HTML报告中的每个结果都包含一个超链接,该超链接将打开该实例的EZwave示波器视图。

图20:HTML模拟报告显示,快速模型转角情况未达到最大转换率裕度

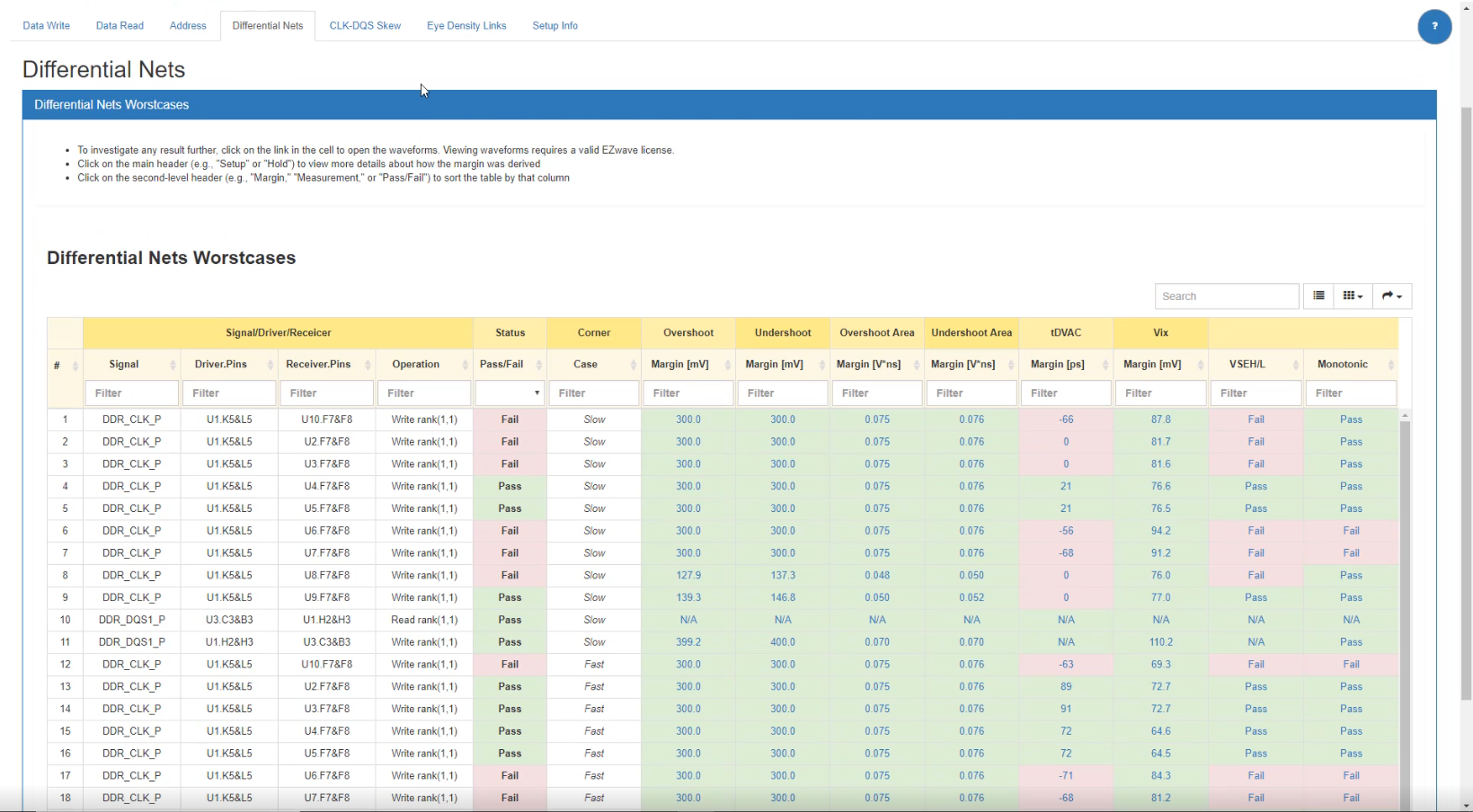

“差分网络”选项卡显示了多条记录道上发生的许多错误,可能需要进一步注意和调查(图21)。由于控制器上启用了写平衡选项,因此满足所有倾斜裕度。眼睛密度链接页面允许对每个模拟结果进行进一步调查和可视化。

图21:Differential Nets选项卡显示了许多错误

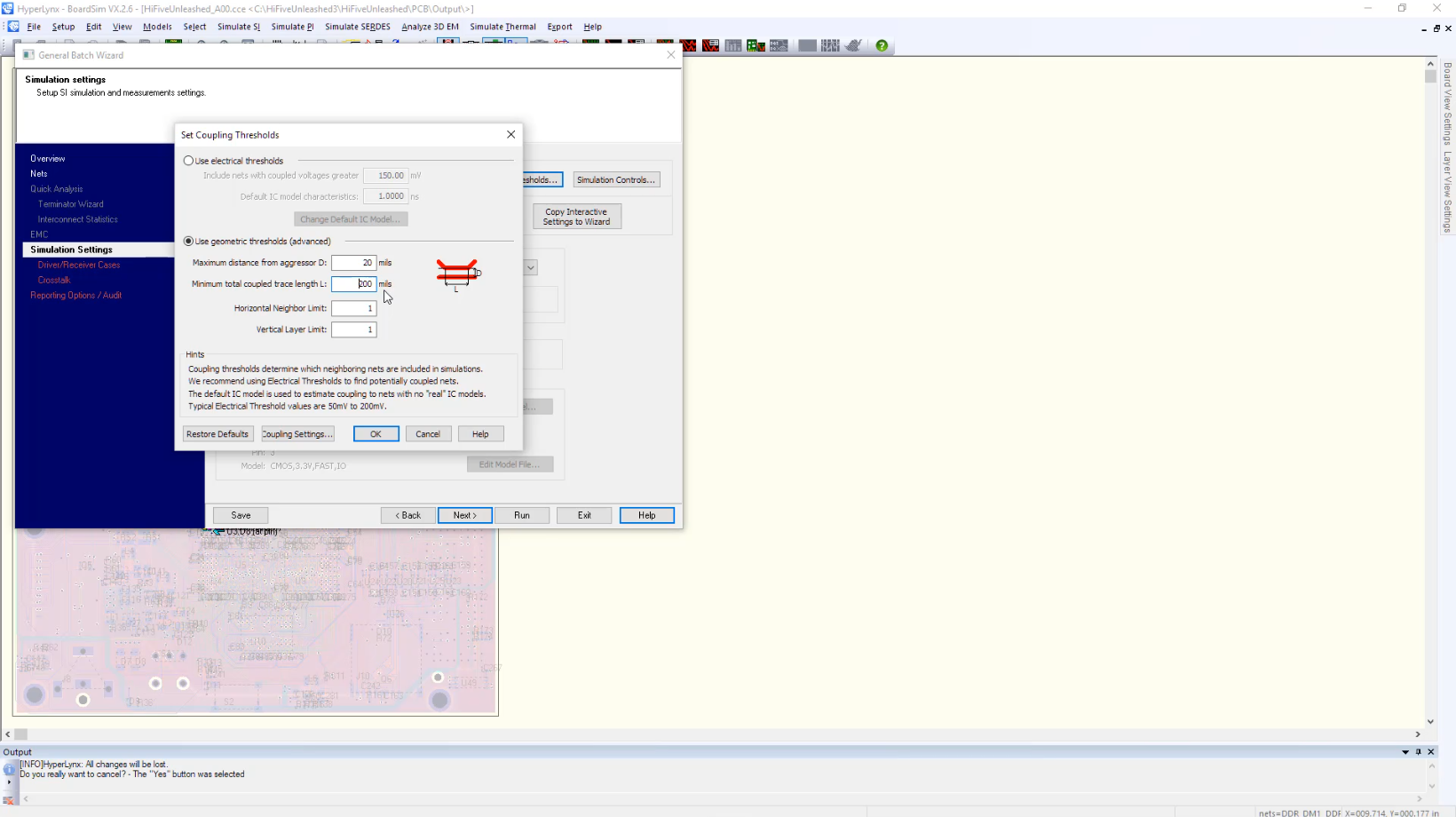

在本演示的最后一部分,将使用通用批处理向导仅模拟数据和数据掩码网络上的串扰效果。当大多数串扰发生时,仅模拟快速模型角点可以解释这种情况。然后,工程师将自定义耦合阈值,使其具有紧密的参数,与侵略者的最大距离为20密耳,最小耦合轨迹长度为200密耳(图22)。最后,每个网络上允许的最大串扰电平将指定为50 mV。

图22:耦合阈值可根据具体设计要求进行定制

一旦模拟完成并显示HTML报告,工程师可以安全地确定数据网络不会受到不可接受的串扰。任何网络上的最大串扰略低于40 mV(图23),仍远低于确定的50 mV阈值。

图23:没有任何网络超过50 mV串扰阈值

HyperLynx DDR 中提供的强大功能使工程师能够在设计过程的所有阶段可视化现实世界的性能障碍。使用这项技术,可以在关键信号完整性并发症发生之前捕获和反转,并完全避免它们。借助集成的仿真和设计工具,用户可以消除 DDR 设计过程中的猜测,同时消除复杂的信号完整性问题并防止昂贵的电路板重新设计。

审核编辑:郭婷

-

DDR

+关注

关注

11文章

762浏览量

69588

发布评论请先 登录

基于RISC-V开发板的DDR演示的设计方案

HYPERLYNX 仿真工具使用指南

PCB布局及原理图交互式抓取

使用AM437x无VTT终端的DDR3参考设计包括BOM及原理图

如何导出单个原理图和布局

多功能的PCB原理图输入工具Cadence OrCAD Capture介绍

CadenceOrCADCapture电路原理图输入工具的优点

从PCB原理图到电路板布局

中兴原理图sch设计(EDA工具手册)

EDA工具手册Cadence教程之原理图设计资料概述

EDA工具手册Cadence教程之原理图设计的资料免费下载

使用集成的原理图、布局和仿真工具消除DDR设计中的猜测

使用集成的原理图、布局和仿真工具消除DDR设计中的猜测

评论