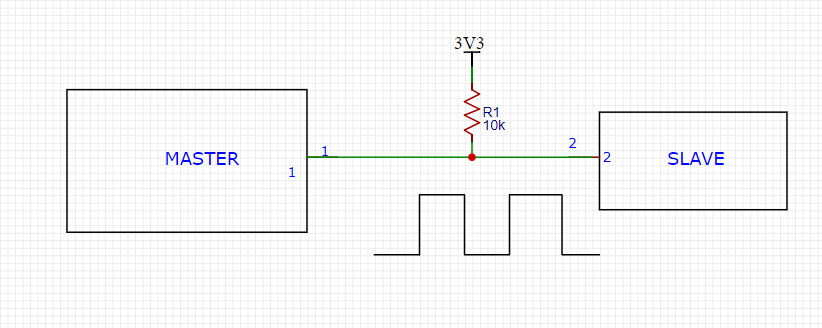

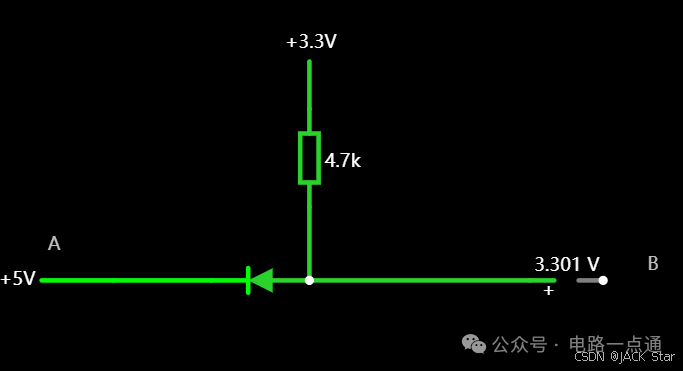

一般在芯片的GPIO口内部是开漏的状态下,外部需要连接上拉电阻,一般连接方式如下图,而且理想的高低电平应该是低电平电压值接近0V,高电平状态值在3.3V左右。

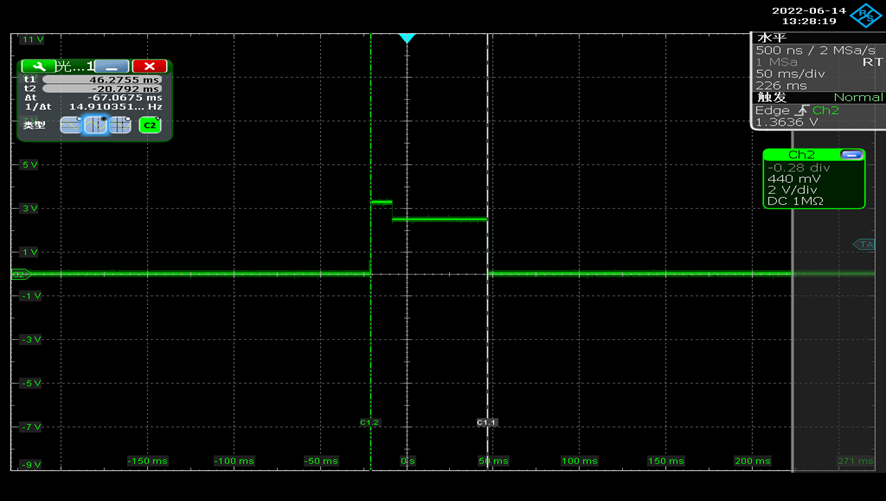

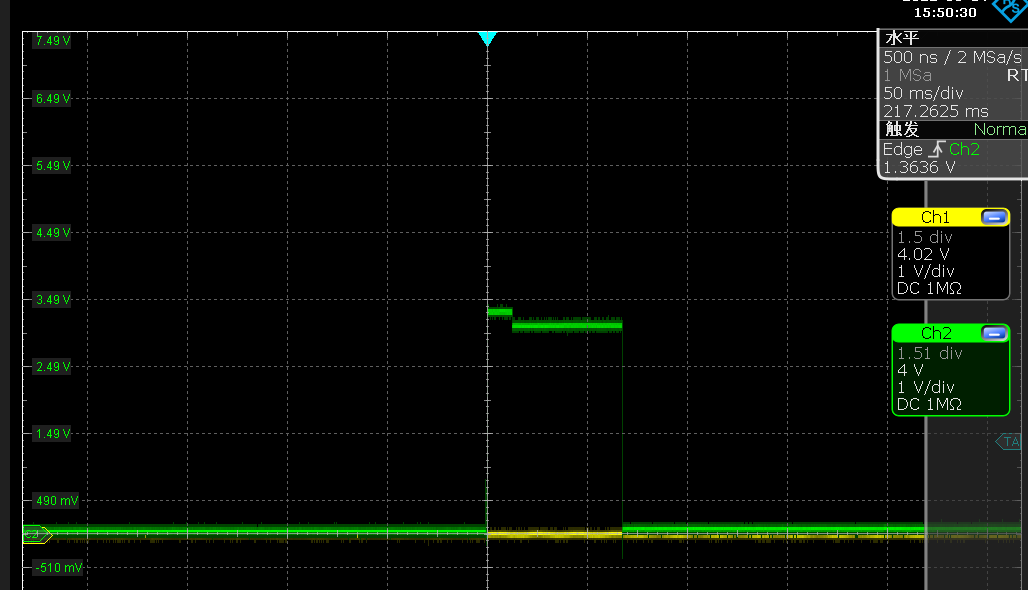

但是在这边实际测试的情况下却遇到一个问题:高电平状态电压先是3.3V,后面又被拉低到2.567V。

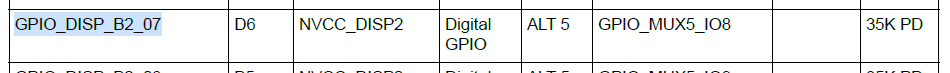

这个情况非常奇怪,开始被没有找到原因,直到翻看MASTER 芯片的规格书,发现它的这个GPIO口内部是有一个35K的下拉电阻的。

根据分压原理,35K的下拉电阻和10K的上拉电阻,中间的分压点电压计算就是3.3V*35/(35+10)=2.567V。理论分析对得上实际测试结果。

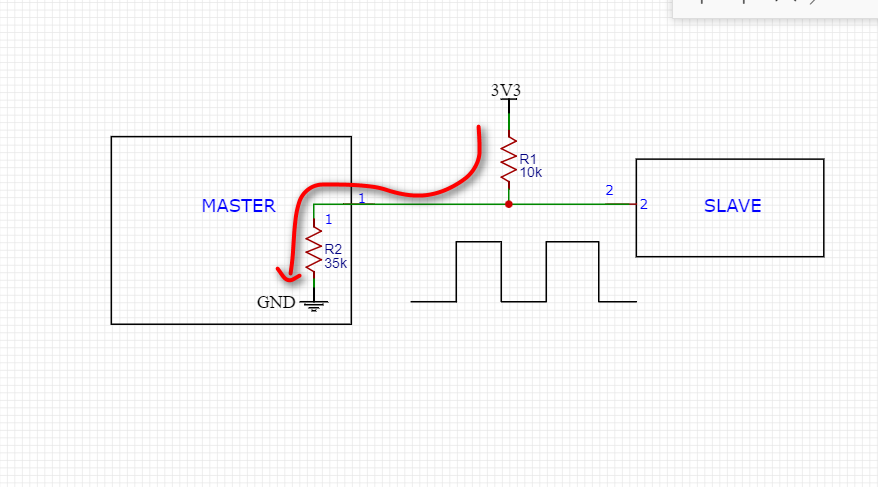

那么在这种情况下,预防高电平状态的电压阈值不够,就只能把上拉电阻值调小了,最后选择调整为2.2K。那么进行计算,分压点电压V=3.3V *35/(35+2.2) =3.1V。

那么3.1V的电压就没有什么风险了。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

上拉电阻

+关注

关注

5文章

366浏览量

31724 -

电平

+关注

关注

5文章

373浏览量

41794 -

GPIO

+关注

关注

16文章

1334浏览量

56470

发布评论请先 登录

相关推荐

热点推荐

探索 FIN1048:3.3V LVDS 4 位直通高速差分接收器

探索 FIN1048:3.3V LVDS 4 位直通高速差分接收器 在电子设计领域,高速数据传输和低功耗是永恒的追求。今天要给大家介绍的是 Fairchild Semiconductor(现属于

基于UCC2891的48V转3.3V正激变换器设计与应用

基于UCC2891的48V转3.3V正激变换器设计与应用 在电子设备的电源设计中,高效、稳定的电源转换是至关重要的。今天我们来深入探讨一下基于UCC2891有源钳位电流模式PWM控制器的48V转

MAXM17545 3.3V输出评估套件:高效电源模块评估利器

MAXM17545 3.3V输出评估套件:高效电源模块评估利器 在电子设计领域,电源模块的性能直接影响着整个系统的稳定性和可靠性。MAXM17545 3.3V输出评估套件为我们提供了一个便捷的平台

MAX17572 3.3V输出评估套件:高效DC - DC转换评估利器

MAX17572 3.3V输出评估套件:高效DC - DC转换评估利器 在电子设计领域,DC - DC转换器的性能对于整个系统的稳定运行至关重要。MAX17572 3.3V输出评估套件为评估

MAX17574 3.3V 输出评估套件:高效电源转换的理想之选

MAX17574 3.3V 输出评估套件:高效电源转换的理想之选 在电子设计领域,电源转换模块的性能和稳定性至关重要。今天,我们将深入探讨 MAX17574 3.3V 输出评估套件,它为评估

深入解析MAX17545 3.3V输出评估套件

深入解析MAX17545 3.3V输出评估套件 在电子设计领域,高效、稳定的电源转换至关重要。MAX17545 3.3V输出评估套件为我们评估MAX17545高压、高效同步降压DC - DC转换器

MAX17542G 3.3V输出评估套件:高效电源转换解决方案

MAX17542G 3.3V输出评估套件:高效电源转换解决方案 作为电子工程师,我们在设计电源电路时,常常需要一款性能可靠、设计成熟的评估套件来验证和优化设计。今天,就为大家介绍MAX17542G

探索MAX17541G 3.3V输出评估套件:高效电源转换的理想之选

探索MAX17541G 3.3V输出评估套件:高效电源转换的理想之选 在电子设计领域,电源转换模块的性能和稳定性至关重要。今天,我们就来深入了解一下Maxim Integrated推出

MAX17505 3.3V输出评估套件:高效DC - DC转换评估利器

MAX17505 3.3V输出评估套件:高效DC - DC转换评估利器 在电子设计领域,DC - DC转换器的性能对于整个系统的稳定性和效率至关重要。今天,我们就来深入了解一下MAX17505

深入解析DS1836/A/B/C/D 3.3V/5V MicroManager

特性 电源相关特性 电源复位 :支持 5V 或 3.3V 电源上电复位,在电源瞬变期间能产生复位信号,并且在 (V_{CC}) 恢复到正常范围后,

NRF52840 在3.3V供电时VIL(MAX)是0.99V还是0.35V

nRF52840 在 3.3V 供电时,GPIO 输入低电平最大值 VIL (MAX) 为 0.99V ,并非 0.35V。你之前没找到该参数,大概率是没定位到规格书中 GPIO 电气

发表于 01-30 20:05

SN74LVT574PWR 具有三态输出的 3.3V ABT 八路边沿 D 类触发器

SN74LVT574PWR特征●宽供电范围:2.7V-3.6V,典型3.3V,适配3.3V系统,兼容5V输入信号。●高驱动能力:高

NRF52840 在3.3V供电时VIL(MAX)是0.99V还是0.35V

nRF52840 在 3.3V 供电时,GPIO 输入低电平最大值 VIL (MAX) 为 0.99V ,

规格书权威参数来源在 Nordic 官方 nRF52840 规格书的GPIO 电气特性章节

发表于 12-17 16:13

为什么是3.3V与1.8V?3.3V与1.8V是哪里来的?

3.3V是因为当年演进到.35um工艺的时候栅极氧化层厚度减到了7nm左右,能承受的最大源漏电压大概是4V。减去10%安全裕量是3.6V。又因为板级电路的供电网络一般是保证+-10%的裕量,所以标准

信号被上拉,但电平不是3.3V的原因

信号被上拉,但电平不是3.3V的原因

评论