您知道系统架构师在片上系统 (SoC) 设计中的具体工作吗?如果您已经认识或经验丰富的系统架构师,那么可能无需进一步阅读。但是,如果您是我们众多正在探索该行业机会的年轻读者之一,请继续阅读,看看这是否是您或可能是您。

对系统架构师的需求不断增长,因为领先的数字 ASIC 设计每年都变得更加复杂,并且需要数十人的团队在它的所有不同方面工作。根据先进的芯片设计公司 Sondrel 的说法,系统架构师对于协调设计项目的各个方面都很重要。

Sondrel 的设计架构主管 Paul Martin 将系统架构师比作管弦乐队的指挥。他说:“他或她必须对一个项目所需的所有技能有深刻的理解,并知道它们何时适合项目的顺序,就像指挥对管弦乐队的所有部分在正确的演奏中所做的那样时间。只有在这种情况下,它才能确保每个项目都符合规范并按时按预算进行。我们成功做到这一点的声誉是每个季度都会引入更多项目,这就是为什么我们在全球所有设计中心招聘多技能工程师作为系统架构师来满足需求。”

具有数十亿门的高级节点芯片设计的复杂性需要经验丰富的工程师的大型团队。正如 Sondrel 首席执行官 Graham Curren去年在其工程师招聘活动中解释的那样,“例如,我们最近完成了一项 16nm 设计,需要 100 多人全职工作一年多。这种资源部署通常只能在大型蓝筹公司内部使用。”

Curren 提到的 16nm 芯片是当时公司为客户设计的最大的芯片,一个 500 平方毫米的芯片,拥有超过 300 亿个晶体管、4000 万个触发器和 23000 个用于 I/O、电源和接地的焊盘。大约三分之一的芯片平面图是处理实时图像处理的客户 IP 块。Sondrel 支持图形处理器单元块、两个中央处理器单元、片上高速缓存存储器、PCI 和 USB 接口以及存储器控制器到片外存储器,在一个邮票大小的芯片上使用超过 7 公里的金属轨道.

一次性设计出如此复杂的芯片是不可能的,因为它有 3 亿个可布局的逻辑单元,而布局工具一次只能处理 300 万个,而运行时间不会变得过多。因此,它被划分为大小可控的功能块,分布在金字塔结构的四个层次上。

为了达到这一点,在 SoC 开发周期的早期,产品经理、系统架构师和相关的技术利益相关者讨论并详细说明产品需求。每个组都倾向于对产品有一个特定的心理模型,通常是产品经理专注于最终用途和产品应用。同时,系统架构师关注功能和执行,以及需求的实现。

这个“需求捕获阶段”识别、制定和记录所有已知的功能和指标,包括清晰完整的提案中的性能需求。此外,该练习确定了尚未完全理解或以后可能包括在内的功能,并试图确定和计划完成此类功能的鉴定和量化所需的任务。

完成后,或在程序开始时尽可能完成时,系统架构团队的需求会经历一个分析阶段,其中包含来自设计和实施团队的适当输入。这个迭代过程的结果是一个架构设计规范,其中包括一个架构设计,其所有功能、功率估计、性能和面积都已确定。

在初始阶段包含设计和实施工作可确保对规范和体系结构的更高水平的准确性和验证,并确定指导设计选择所需的敏感性。

架构分析包括架构探索、IP选择/规范、需求验证和项目执行计划的生成,主要任务在后期阶段详细阐述。

候选架构的架构探索是一个主要组成部分。它通过对提案进行建模和评估已知或参考用例来改进架构设计,动态地允许定义系统拓扑并分配要分配的资源(内存、总线结构数据/控制路径等)。

虽然它允许评估和验证功能的各个方面(连接性、时序、性能)以确保设计的正确性,但使用更详细和准确的模型的后期阶段用于确定和纠正架构实施期间的潜在错误.

SoC 架构探索的初始部分是一种严格的方法,用于捕获 SoC 需要执行的一个或多个应用程序用例和数据流。准确而完整的用例描述对于与利益相关者进行沟通并在产品定义阶段早期就需求达成一致是必要的。系统架构师寻求提取产品需求并表达它们,以便技术和非技术利益相关者能够跟上产品意图和架构选择,而无需过多的技术细节。

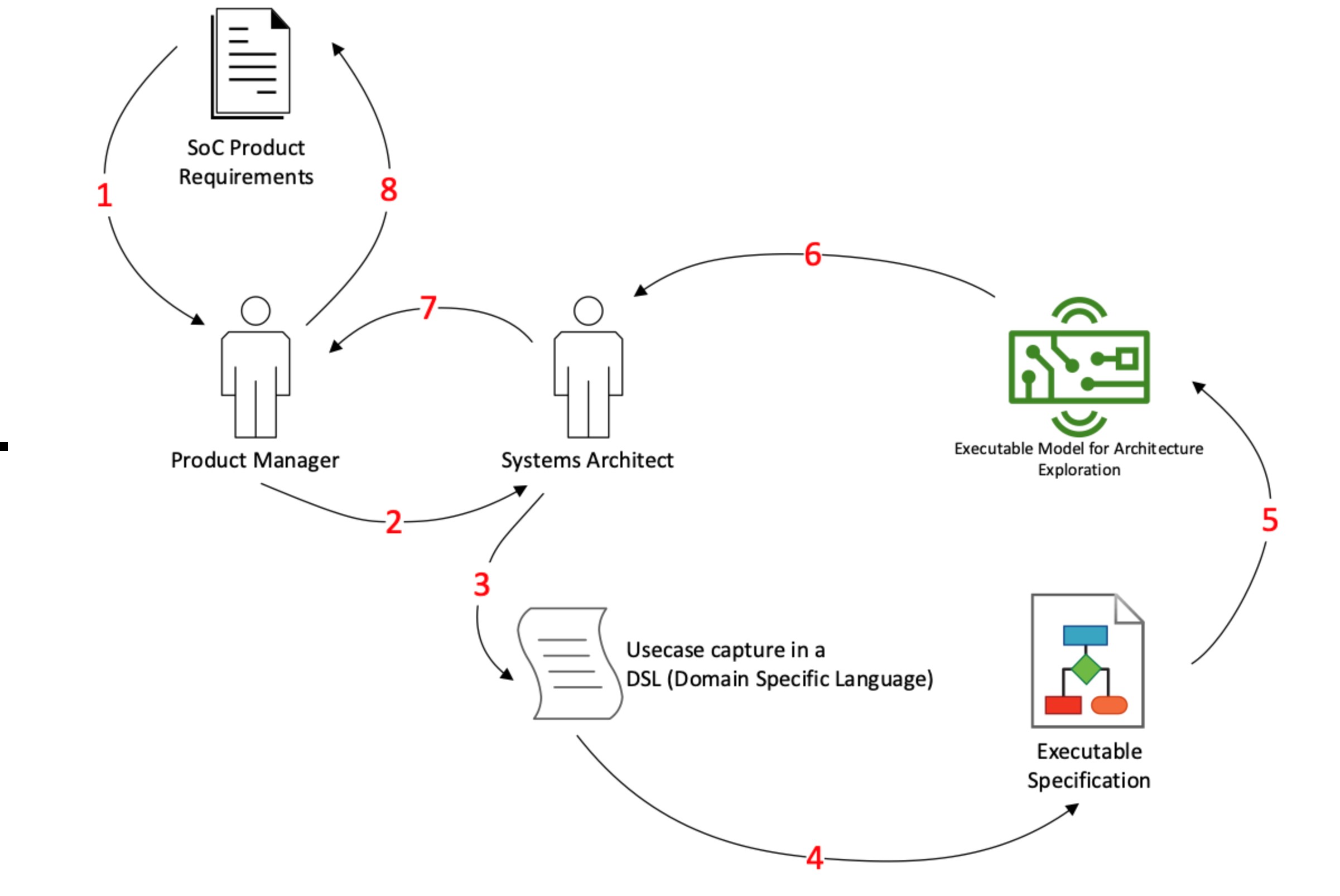

从产品需求到可执行架构模型的流程。(来源:桑德雷尔)

这个协作过程有八个步骤:

产品经理对潜在的 SoC 解决方案进行市场分析、行业趋势和产品需求定义。

产品用例需求通常通过演示文稿、电子表格或文档传达给系统架构师。

建模流程所需的需求转换为 DSL 格式。

工具生成用例的可执行规范和可视化。

工具还生成用例架构探索所需的周期精确的 SystemC 模型。

系统架构师检查探索练习的结果,并逐渐收敛到 SoC 的最佳架构。

系统架构师与产品经理交流调查结果。

产品经理可能决定修改需求或与系统架构师合作以进一步完善候选 SoC 架构。

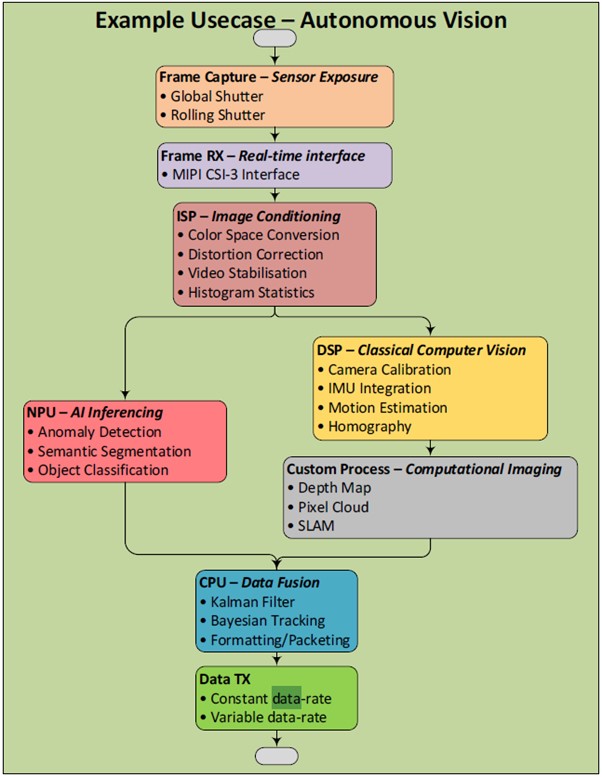

为了说明用于系统架构探索的 SoC 应用用例,Sondrel 发表了一篇论文,涵盖了在程序的架构阶段使用建模。下图显示了一个典型的自主视觉用例数据流图,其中节点代表处理功能,边代表数据流。

示例自主视觉用例数据流。(来源:桑德雷尔)

流程中的具体阶段是:

帧曝光——相机传感器拍摄其视野快照的时间间隔。图像传感器可以配置为全局快门或滚动快门模式,每种模式都有一个与之相关的曝光时间。

帧 RX – 成组的图像像素通过实时接口(例如 MIPI CSI-3)发送到 SoC 的时间间隔。

图像调节——在实际计算阶段之前对接收到的数据执行的任何图像预处理、过滤或汇总步骤。

经典计算机视觉——众所周知的视觉处理算法,例如,相机校准、运动估计或立体视觉的单应运算。

计算成像——视觉算法通过像素云或深度图估计等自定义处理步骤得到增强

AI 推理——基于神经网络的图像处理,用于语义分割、对象分类等。

数据融合——最后阶段的传感器融合和跟踪。还可能包括格式化或打包处理。

数据 TX – 可以通过 PCIE 或实时接口(例如 MIPI CSI-3)以恒定或可变数据速率传输。

本文接着定义了两个仿真结构,应用用例模型和硬件平台模型,然后是一个完整的仿真模型,用例任务映射到硬件平台的子系统上。完整的论文“系统架构探索的 SoC 应用用例捕获”可从Sondrel获得。

审核编辑 黄昊宇

-

芯片

+关注

关注

463文章

54429浏览量

469377 -

soc

+关注

关注

40文章

4624浏览量

230204 -

设计

+关注

关注

4文章

828浏览量

71487 -

架构师

+关注

关注

0文章

48浏览量

4936

发布评论请先 登录

Altera Agilex FPGA与SoC实现更智能的AI

为何AI数据中心的系统架构师首选Arm平台

Springboot+SpringData+SpringCloud微服务架构课程

新思科技EDA工具和车规IP助力芯粒架构汽车SoC设计

当主控芯片架构不断变化时,系统研发团队真正需要什么样的开发平台?

高通Oryon架构之父宣布离职:曾一手定义移动芯片黄金时代

【工程师必看】三星电容在车载智能座舱/中控系统中的选型与案例分析

AMD UltraScale架构:高性能FPGA与SoC的技术剖析

高集成度、全数字化架构!SPAD-SoC优势和技术路线

人脸识别和AES加密协同的SOC设计架构

浮点指令扩展中16位指令的处理

在TR组件优化与存算一体架构中构建技术话语权

Tenstorrent 首席架构师:未来 RISC-V 会是计算机的主流

如何释放异构计算的潜能?Imagination与Baya Systems的系统架构实践启示

什么是 SoC 设计中的系统架构师?

什么是 SoC 设计中的系统架构师?

评论