用于精心管理电源的片上系统 (SoC) 的新 DSP 内核、具有正交频分多址 (OFDMA) 的电力线通信 (PLC) 芯片高噪声智能电网环境,以及电子设计自动化 (EDA) 设计流程的独特方法,可为 SoC 设计人员带来巨大回报。

DSP 性能与节能

DSP 对便携式多媒体设备至关重要,但是在保持电源管理的同时实现高性能以及在电池供电操作的预期范围内是两件事并没有很好地结合在一起。找到一种在控制功耗的同时提供更高 DSP 性能的方法创造了一个有趣的突破。

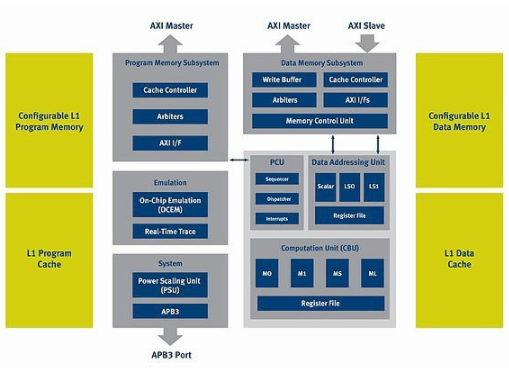

图 1: CEVA-X1643

CEVA 最新的 DSP 内核 CEVA-X1643 提供 1 GHz 的处理速度和一个集成的功率调节单元 (PSU),可处理动态和泄漏功率的高级电源管理。PSU 控制内核中的多个时钟源和电源域,以及从完全开启到调试旁路到内存保留到完全断电的多种操作模式。AXI 总线接口还提供低功耗功能,例如在没有流量运行时关闭。

CEVA

www.ceva.com

www.embedded-computing.com/p46219

电力线通信采用 OFDMA

多年来,国防和宽带通信网络一直使用频率捷变无线电来避免干扰并提供强大的通信。智能电网的一个恒定特征是噪声——大负载快速切换并且经常在电力线上产生大量电气噪声。在这个最新的创新中结合这两个想法。

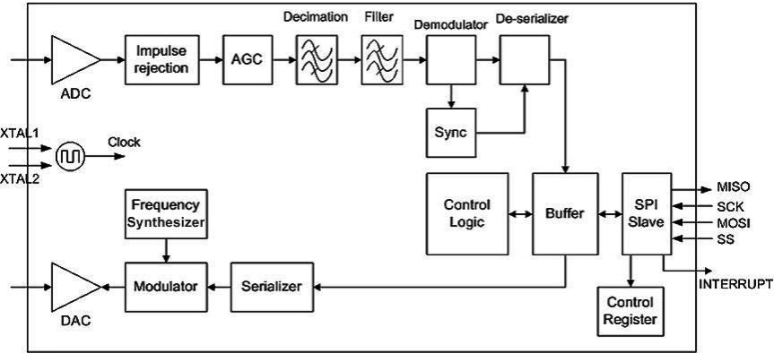

图 2: Semitech SM2200

Semitech 的 SM2200 PLC 芯片将 OFDMA 收发器用于管理电力线数据的任务,例如用于智能电网的数据。它适应噪声环境,选择最有效的运行频率,并使用多接入方案来帮助同时与多个节点通信。SM2200 可以很容易地与微控制器结合来构建数据链路。

Semitech Semiconductor

www.semitechsemi.com

www.embedded-computing.com/p46220

EDA 设计流程使 SoC 断电

今年设计自动化大会的最大主题之一是低功耗设计流程。随着速度越来越快和几何尺寸越来越小,SoC 中的动态和泄漏功率成为更大的问题,这已经不是什么新闻了。在设计流程中优化功率可能是一项耗时的手工工作,可能会引入更多错误并减慢整个过程。

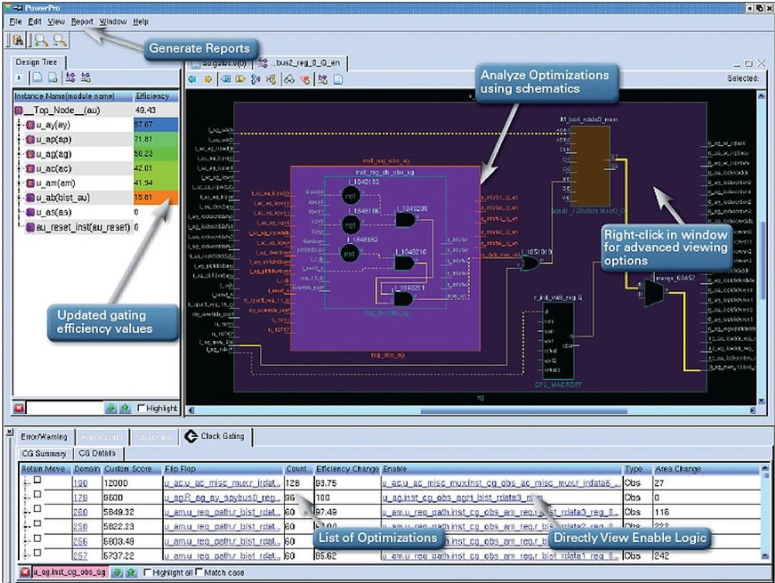

图 3: Calypto PowerPro MG

Calypto Design Systems、Virage Logic 和半导体技术学术研究中心 (STARC) 共同承担 SoC 电源的主要组成部分:片上存储器。Calypto 的 PowerPro MG 使内存门控逻辑与 Virage Logics 的 SiWare 内存编译器中的浅睡眠、深度睡眠和关机等内存模式协同工作。内存编译器自动生成 PowerPro MG 模型,STARC 已在无缝、低功耗 EDA 设计流程中实现了该模型。合作公司声称通过该方法可降低 50% 的动态功耗和 40% 的泄漏功耗,这对于 SoC 设计人员来说是一个好消息。

审核编辑:郭婷

-

存储器

+关注

关注

39文章

7755浏览量

172176 -

soc

+关注

关注

40文章

4622浏览量

230157 -

编译器

+关注

关注

1文章

1672浏览量

51904

发布评论请先 登录

SOP8封装/4通道/自适应算法:FTX-Basic-Touch电容触摸IC实测与方案解析

超低功耗自适应线性功率双端口ADSL/ADSL2+线路驱动器ADLD8403深度解析

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】跟着本书来看EDA的奥秘和EDA发展

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】+ 芯片“卡脖子”引发对EDA的重视

LMH0394:3G HD/SD SDI低功耗扩展距离自适应电缆均衡器的卓越之选

LMH0395:3G HD/SD SDI双输出低功耗扩展范围自适应电缆均衡器的深度解析

LMH1219:低功耗12G UHD自适应电缆均衡器的技术解析与应用指南

什么是低功耗设计,如何评估低功耗MCU性能?

【书籍评测活动NO.69】解码中国”芯“基石,洞见EDA突围路《芯片设计基石——EDA产业全景与未来展望》

电磁干扰自适应抑制系统平台全面解析

基于FPGA LMS算法的自适应滤波器设计

CYW43907使用AP功能时是否具有自适应功能?

Texas Instruments LMH0044SQ/NOPB 自适应电缆均衡器的参数特性、EDA模型 数据手册分享

自适应PLC芯片和低功耗EDA设计流程

自适应PLC芯片和低功耗EDA设计流程

评论