CORE Generator里有很多的IP核,适合用于各方面的设计。一般来说,它包括了:基本模块,通信与网络模块,数字信号处理模块,数字功能设计模块,存储器模块,微处理器,控制器与外设,标准与协议设计模块,语音处理模块,标准总线模块,视频与图像处理模块等。

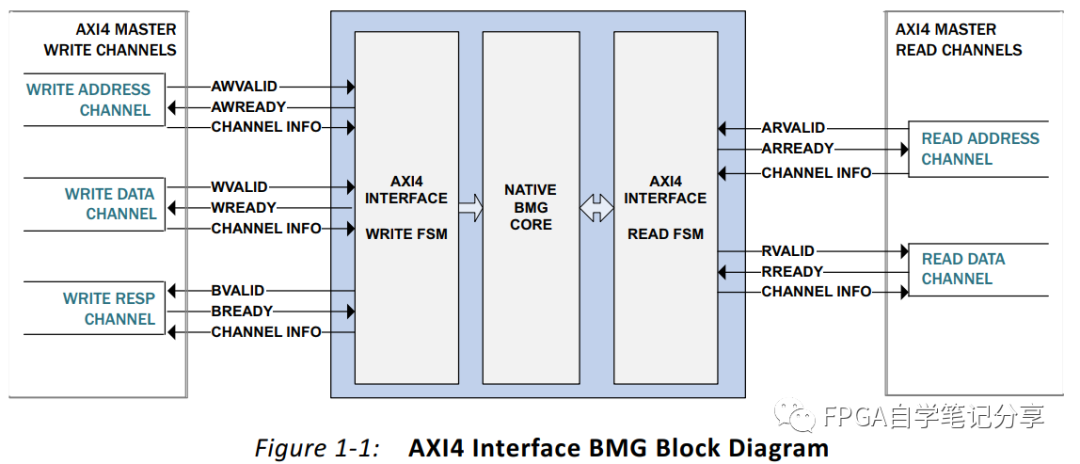

在Xilinx的IP核里有xilinx core generator 里面的memory interface generator 和block ram,使用这两个可以使用FPGA内部和外部的RAM。memory interface generator 是 ddr2/ddr3/qdr2 这些外部存储器的接口,block ram 是 fpga 芯片内部片上的存储器。接下来介绍一下block ram。

block ram有三种:单口RAm、简化双口RAM和真双口RAM。

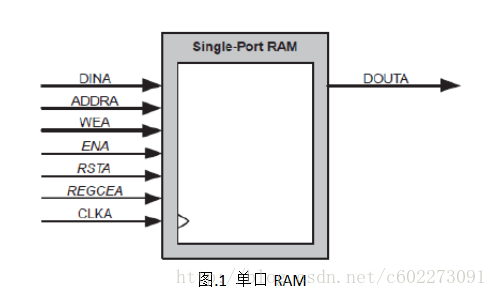

单口:

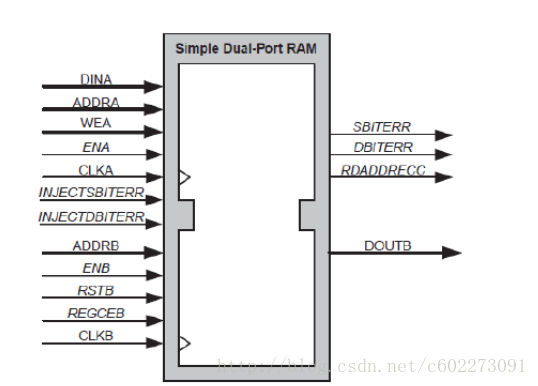

简化双口,A写入,B读出:

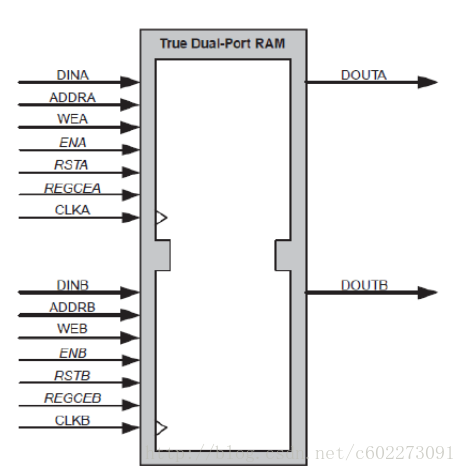

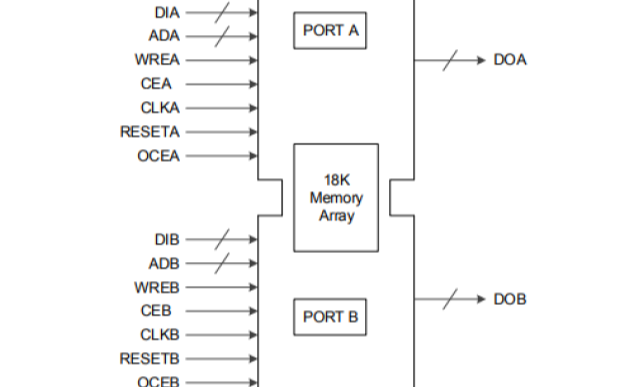

真双口,A和B都可以读写:

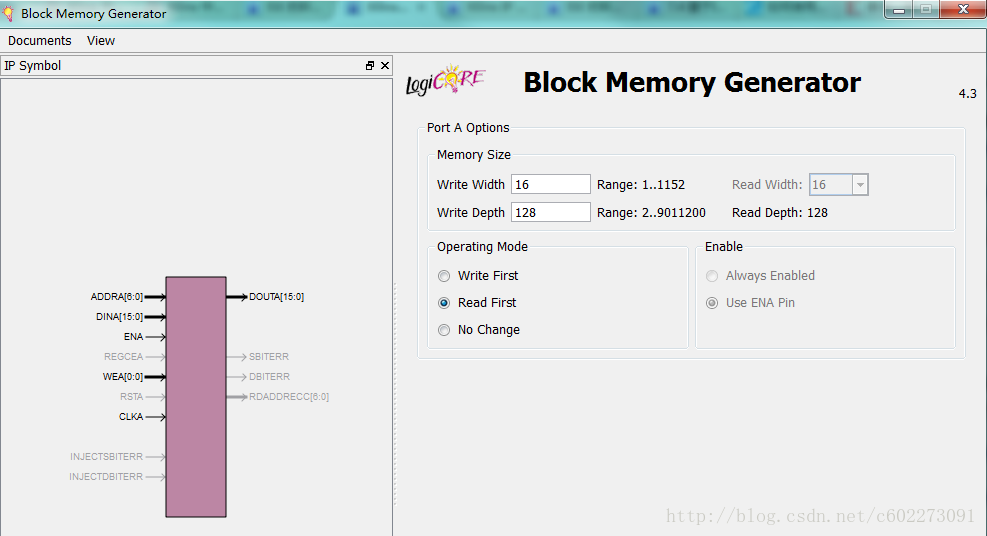

使用IP核,确定数据位宽和深度:(超出地址范围将返回无效数据,在对超出地址范围的数据进行操作的时候,不能够set或者reset)。这里我选择的是16位的位宽,128的深度。

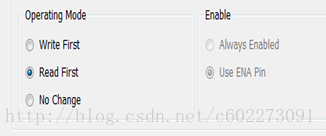

设置操作模式:(写优先,读优先,不改变)

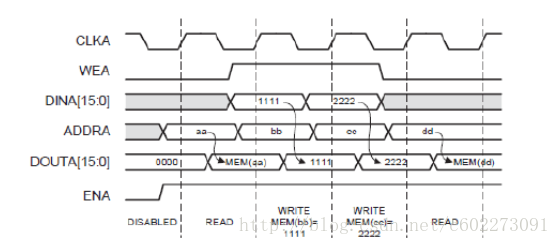

这里的写优先的意思就是你写入的数据,会出现在输出端口,不管你给的地址是什么。这种好处就是保证了你读出的数据是最新的。

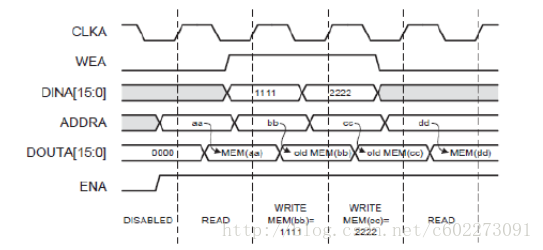

读优先指的就是:不管你写入的数据,是先把你要读的数据读出。

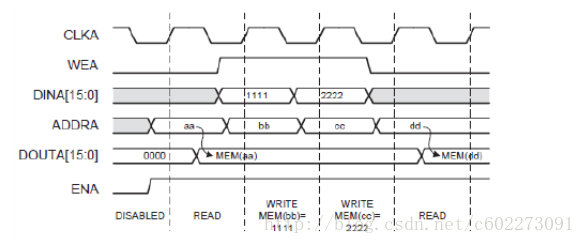

不改变模式就是正常的模式,该读的时候读,改写的时候写:(一般没有特殊要求就是选这个)

接着写coe文件,打开txt,输入:

MEMORY_INITIALIZATION_RADIX=10;

MEMORY_INITIALIZATION_VECTOR=

512,515,518,522,525,528,531,535,538,54,......12,23;

保存之后为coe格式。

这个如果很少就自己输入,如果比较大,比如一幅图片,那就使用matlab吧!

举个例子,你要生成ROM:

% 生成 ROM 的 .coe文件

clc clear all close all x = linspace(0, pi/2 ,1024); % 在区间[0,2pi]之间等间隔地取1024个点 y_cos = cos(x); y_sin = sin(x); y_cos = y_cos * 2^16; y_sin = y_sin * 2^16; fid = fopen('D:/cos_coe.txt','wt'); fprintf(fid, ' .0f ' , y_cos); fclose(fid); fid = fopen('D:/sin_coe.txt','wt'); fprintf(fid, ' .0f ' , y_sin); fclose(fid);

比特写功能(byte_write):

当使用8bit一字节的时候没有优先级,而存储在宽度限定为8bit的倍数。当使用9bit一字节的时候,每一个字节都包含一个优先级位,存储限定为9bit的倍数。9bit的一般不用于NO_CHANGE模式。对于双口的RAM,只能是读优先或者写优先。

我们要设置为primitive原语的模式,还可以选择增加复位等功能,但是复位不能异步,只能同步实现。

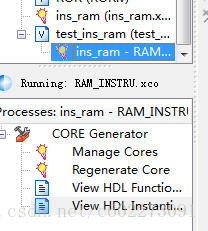

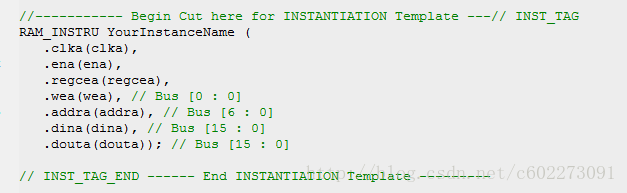

最后生成了IP核之后,点击你的IP核的下方,然后可以看到你的instance,你就知道怎么用这个IP核了。另外对于IP核的使用,其实你看datasheet那就更好了。

原文标题:FPGA开发之RAM IP的使用

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1663文章

22494浏览量

638984 -

Xilinx

+关注

关注

73文章

2205浏览量

131831 -

generator

+关注

关注

0文章

57浏览量

33720 -

Block

+关注

关注

0文章

26浏览量

15172

原文标题:FPGA开发之RAM IP的使用

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Xilinx FPGA IP之Block Memory Generator功能概述

Xilinx FPGA IP之Block Memory Generator AXI接口说明

Xilinx FPGA入门连载48:FPGA片内RAM实例之RAM配置

Spartan 3E XC3S250E中的100Kbit RAM模块使用问题

Xilinx Block RAM能否在一个时钟周期内始终如一地返回数据?

请帮助我解决Block RAM问题?

创建Block RAM IP不起作用

请问9K Block RAM设计中那些2 9K Block RAM在哪里?

为什么为spartan6生成fifo ip_core时会出现警告?

XILINX BMG介绍

对于Xilinx FPGA的片上存储资源的统计介绍

FPGA的RAM存储资源详细资料说明

xilinx core generator里面的block ram介绍

xilinx core generator里面的block ram介绍

评论