先进的测试设计 (DFT)技术提供了高效的测试解决方案,通过提高顺序触发器的可控性和可观察性来处理更高的测试成本、更高的功耗、更高的测试面积和更小尺寸的引脚数。反过来,这提高了 SoC 的良率。可靠性和可测试性是当今 ASIC 世界的重要因素。

SoC 只不过是在单个硅衬底上集成多个处理器内核、微控制器、接口、DSP(数字信号处理器)和存储器的集成电路。在这个时代,它是任何数字系统中最重要的部分之一,因为它有助于节省电力、成本和空间。

内核只不过是 SoC 设计公司的知识产权或 IP 内核。SoC 设计公司为内核提供测试,而 SoC 设计人员提供对嵌入在芯片上的内核的测试访问。它是通过插入带有测试逻辑的包装器结构来插入包装器链的层次结构。我们可以最大限度地减少核心测试问题,并可以减少 SoC 的顶层管脚数。

本文简要介绍了分层 DFT 技术的重要性,该技术利用包装链来克服测试大型 SoC 设计的问题。它显着减少了 ATPG 测试时间、内存占用和引脚数。最终,它缩短了上市时间。

测试核心包装器

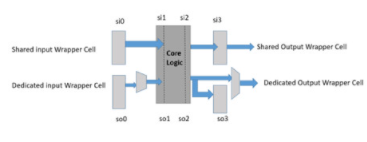

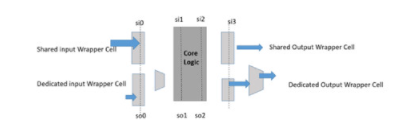

对于 DFT,可以在 SoC 级集成之前单独测试每个内核。在进行集成时,当它们配置为内部测试模式时,可以单独或分组测试内核的内部逻辑。但是,当配置为外部测试模式时,可以测试内核的周边逻辑。通过这样做,我们主要关心的是在不同的配置中划分 SoC 测试,以大大减少模式生成工作,进而减少测试时间。

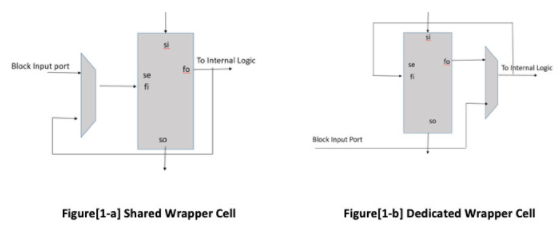

包装细胞结构

测试包装模式

向内或 INTEST 模式

在 INTEST 模式下,通过驱动输入包装单元的输入,我们测试分区并通过输出包装单元捕获输出。这是通过禁用内核外部的扫描链来完成的。它有助于使用 ATPG 对分区核心进行隔离测试。在捕获期间,输入包装器单元使用单独的输入包装器扫描启用信号进行移位,这避免了从分区外部捕获 x。而输出包装单元捕获分区的内部状态。

(图[2]:向内(测试)模式)

外向或 EXTEST 模式

在 EXTEST 模式下,封装器被启用并配置为驱动和捕获设计之外的数据。它本质上通过在这种模式下绕过它来禁用内部链。因此,它也减少了 ATPG 测试时间。要测试分区和展开逻辑之间的顶层逻辑,我们可以使用这种模式。在捕获阶段,值被分区外的输入包装单元捕获,并且输出包装单元在捕获期间移动,以避免从分区的未驱动的内部扫描链中捕获 x。

(图[3]:外向(外部)模式)

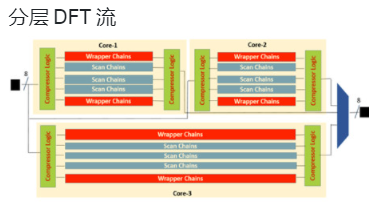

分层 DFT 方法

(图[4]:分层DFT实现(从核心到芯片级))

大型设计问题,如工具内存、大 ATPG 运行时间和引脚限制,可以通过分层 DFT 技术解决。在这种方法中,芯片可以被分成多个更小的块或内核,可以有效地访问和处理。由于在核心级别生成模式,它会减少引脚数、内存和测试运行时间。也可以并行运行内核。

每当内核配置为内部模式时,输入包装器就会启动到内核中,并且输出包装器会观察内核输出。在这种情况下,将测试包装器边界内的核心逻辑。所有链都连接到压缩器,它生成可以重新定位到顶层的核心级别模式。它还有助于合并多个核心的模式。对于外部模式,所有包装链都连接到核心边界,并为顶层生成模式。当涉及到全芯片级时,所有包装器链和顶级链都连接到顶级压缩器。

分层 DFT 流

(图[5]:测试访问机制)

图 5 显示了顶层管脚在各个内核层压缩器逻辑和顶层压缩器逻辑之间共享。它导致执行分层 DFT 的顶层芯片管脚减少。可以单独测试单个内核,也可以并行测试以减少测试时间。扫描插入到块级别。当块在顶层组装时,链可以通过以下两种方式之一连接:连接或直接连接到 I/O。在级联扫描链方法中,来自一个块的扫描链与来自另一个块的链级联。

分层 DFT 的优点/缺点:

使用分层 DFT 的一些优点是:

通过使用自动化工具,我们可以在 SoC 级别组装核心级别的链。

如果核心层级链是平衡的,那么工具就很容易平衡 SOC 层级链。

通过保持有限数量的用于扫描链的引脚是可以管理的。

它提供了更多的核心级渠道。

ATPG 运行时间更短,需要更少的内存,从而显着减少了测试时间。

一些缺点是:

当设计包含多个时钟边沿并在扫描链穿过内核时在上升沿和下降沿之间来回遍历时导致移位问题时触发触发器。

为了避免时序问题,我们必须通过使用锁定锁存器来处理内核级别和 SoC 级别的不同时钟域。

万一,在单核级别出现的时序问题可能会损坏所有其他内核,因为链在多个内核中使用。

在本文中,我们探讨了包装器的重要性和包装器单元的类型。如上所述,包装器的特征和功能访问以及包装器对不同块的访问。我们已经看到了使用包装器的分层 DFT 方法以及围绕核心逻辑的包装器单元的互连。最后,我们提到了包装器的生成以及如何使用包装器核心来最小化面积和性能影响。分层核心包装器具有广泛的工业用途,我们已经展示了使用包装器单元的结果。eInfochips为大型 SoC 使用分层 DFT 实施成功地为其大多数客户 提供DFT 解决方案。

作者:Sunil Bhatt,Chintan Panchal,B. Ashok Kumar

审核编辑:郭婷

-

微控制器

+关注

关注

49文章

8881浏览量

165756 -

处理器

+关注

关注

68文章

20336浏览量

255063 -

soc

+关注

关注

40文章

4628浏览量

230216

发布评论请先 登录

【高端人才招聘】格见半导体 资深数字后端工程师 上海&成都

【高端人才招聘】格见半导体 资深数字后端工程师

射频干簧继电器如何为SoC测试“开路”?

大型设备结冰测试的关键技术、标准与设施选择

芯片测试覆盖率99%就够了吗?给DFT设计提个醒

TDE1708DFT智能功率开关:特性、应用与设计要点

肖克利 | 双层 9m³步入式高低温试验箱—工业级环测核心设备

利用分层DFT技术克服测试大型SoC设计的问题

利用分层DFT技术克服测试大型SoC设计的问题

评论