存储器数据的稳定可靠是MCU安全运行的基础,但环境因素和存储器本身的物理特性都可能造成存储器数据异常,本文将详细介绍RAM&ROM常用安全机制。

存储器(ROM,RAM)数据的安全可靠是MCU稳定运行的基础,在汽车功能安全设计中,存储器相关的安全机制也是系统基本保障的重点之一。通常,不同的汽车芯片都有自己的存储器校验机制以及相应的处理手段来保证功能的正常运行。下面会对常见的处理机制进行一些介绍。

RAM的校验纠错机制

RAM的校验机制相对ROM的校验机制较少,校验机制基本都属于MCU本身的特性,通过内部硬件实现,对于用户来说是透明的。而一般用户使用时也不会主动的对RAM进行校验。1. Parity BitParity Bit(奇偶校验位)是一种数据校验机制,常用与判断数据在存储过程中是否发生了比特位错误。

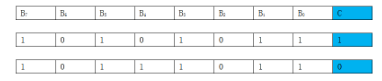

图1 奇偶校验模式可以看到图1,带有Parity Bit的内存在每一个字节(B7~B0)外又额外增加了一个校验位(C)用于对错误进行校验。Parity Bit有着计算简单的优点,只需要对前面字节的位进行异或操作:

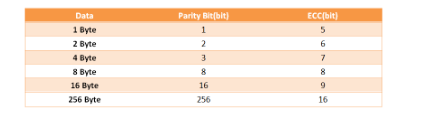

C = B7^ B6^ B5^ B4^ B3^ B2^ B1^ B0Parity Bit在ECC技术之前,是RAM中应用最多的错误检查技术,当然,现在只有在已经很少有CPU用到,因为每1 Byte的数据都需要1 bit的校验位,对于MCU本就很紧张的RAM显然不合适。另外Parity Bit只具备检错能力,并不具备纠错能力。2. ECC通过上面对Parity Bit的分析可以知道,通过在原来的数据1 byte基础上增加1 bit,可以用来检查当前1 byte数据的正确性。如果数据为256 byte就需要256 bit的校验位,而且出错的数据无法纠正。由于上述的缺点,出现了一种新的存储检错纠错机制 – ECC。

图2 检错能力对比ECC(Error-Correcting Code),可以译为检错纠错码。ECC的计算过程比Parity Bit的计算过程复杂一点,这里不进行过多描述。仅针对ECC的两个主要特点进行说明:① ECC有极强的检错能力ECC的计算方式与Parity Bit不同,当数据为1 Byte时,ECC需要5 bit校验位对数据进行校验,之后数据每增加1倍,相应的只需要增加1 bit的ECC 校验位。可以看到图2,ECC的检错能力相比Parity Bit有极大的提升。② ECC具有纠错能力当数据只有单bit 错误时,ECC能够对错误进行修复,但需要注意的是,当数据中有超过 2 bit的错误同时产生时,ECC不一定能检测出来,这一点Parity Bit也是一样。

ROM的检验纠错机制

与复杂的RAM空间相比,ROM空间的操作显然简单的多,因此,对于ROM的校验使用者可以根据不同的需求,选择不同的方式。

常用的有hash,CRC,对于大容量ROM,比如Nand Flash同样也可以使用ECC的方式。基本上,只需要满足ROM内容和生成的校验码存在相对唯一的映射关系即可。

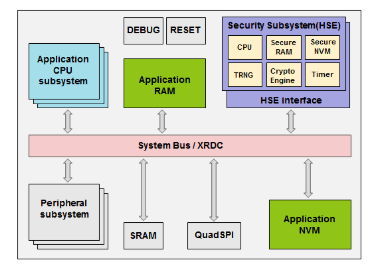

但是用户自己实现的ROM校验机制存在不少缺点:校验失败没有灵活的处理措施,对ROM的校验需要消耗额外MCU资源等。1. HSE随着汽车产业的不断升级,汽车智能化程度也在不断加深,越来越多的汽车会通过OTA的方式实现客户的个性化需求。但OTA在增加汽车升级和维护便利性的同时,也给数据的安全可靠性带来了新的考验。显然,应用开发者自己实现的ROM校验并不足以满足汽车应用的安全需求,汽车应用上,保证MCU程序的正确运行显然需要一套更灵活,更完善的校验机制,并且该校验机制不仅需要保证数据的可靠性,还要保证检验机制本身的可靠性。下面会介绍NXP S32系列芯片是如何利用其HSE安全子系统来为ROM数据的可靠性提供支持,进而保证汽车应用的安全稳定运行的。

图3 HSE框架HSE(Hardware Security Engine)全称为硬件安全引擎,用于给对数据的可靠性和保密性有严格要求的应用提供相应的安全服务。其有以下特点:

独立的内核,固件,存储空间;

可以为加密算法提供安全硬件加速;

支持固件升级。

可以看到图3中,HSE模块最基础也最主要的部分是它的Crypto Engine(加密引擎),其可以通过硬件实现加解密/MAC生成校验/签名验签等功能。因为HSE全面完善的算法和密钥管理机制,可以利用HSE模块可以对用户设定的存储区域进行校验,并根据检验结果执行不同的操作,正是HSE安全可靠,设置灵活的特性,构成了MCU安全稳定运行的基础。当然HSE除了能够为MCU的OTA和安全启动功能提供可靠保证外,HSE通过硬件加速特性和完善的加解密算法库还能够对网络协议进行全面可靠的支持,可以实现TLS offload,IP offload,减少网络协议的通信时延。

结语

上面提到了一些存储器常见的校验方式和NXP S32系列的HSE安全子系统,当然无论通过哪种方式,为了实现OTA和越来越多的网络应用功能,通过MCU实现更加安全可靠的数据存储传输都是现在的趋势。

-

mcu

+关注

关注

147文章

18609浏览量

387081 -

存储器

+关注

关注

39文章

7714浏览量

170854 -

RAM

+关注

关注

8文章

1398浏览量

119824 -

数据存储

+关注

关注

5文章

1014浏览量

52588

发布评论请先 登录

ram ip核的使用

安全芯片的守护神:BIST机制的深度解析

边聊安全 | 安全芯片的守护神:BIST机制的深度解析

LC87F0K08A 8位微控制器8K字节闪存ROM/384字节RAM规格书

【RK3568+PG2L50H开发板实验例程】FPGA部分 | ROM、RAM、FIFO 的使用

k8s集群安全机制说明

Java的SPI机制详解

深控技术的工业网关通过多重安全机制与广泛协议兼容性,确保工业数据从采集到传输的全链路安全与高效互

闪速存储器属于RAM还是ROM,闪速存储器一般用来做什么的

闪速存储器属于RAM还是ROM,闪速存储器有哪些功能和作用

构建安全计算生态 | RISC-V 安全机制的架构设计

RAM、ROM常用安全机制

RAM、ROM常用安全机制

评论