在当今的数字设计世界中,速度通常是决定产品性能的主要因素。许多设计都包含太多高速接口,其信号速度足够高,以至于印刷电路板 (PCB) 的走线和布局在整体系统性能中发挥着重要作用。

因此,信号完整性和电源完整性问题往往是各个产品设计阶段设备故障的主要原因。除了数字部分之外,设计工程师还应谨慎考虑高速 PCB 设计的模拟特性。必须考虑可能增加数字波形时序不确定性的任何物理现象。

当实施明确定义的 PCB 路径时,可以实现信号完整性 (SI)。这些路径允许在正确的时间以干净的边缘将信号从驱动器传送到接收器。SI 较差的设计通常无法满足时序或抖动要求。在某些情况下,较差的 SI 也可能导致高于可接受的辐射发射。在最坏的情况下,设计根本不起作用。

让我们讨论实现高速 SI 的关键设计考虑因素。首先是高频下的传输线行为。在电子产品的早期,由于边缘速率较慢,SI 并不是一个问题。随着时钟速率和信号速度的增加,上升时间因此减少到 PCB 走线长度与通过它们的边沿速率处于相同长度的点。对于具有 2.97-Gbit/s 数据速率的 HDMI 1.4 信号,关键 PCB 长度为 2 mm。因此,必须仔细分析高速 PCB 的传输线及其特性阻抗、延迟和损耗。这些传输线行为是确定连接组件如何交互的关键。最常见的传输线阻抗是 50 Ω。

与 PCB 制造厂的沟通决定了 PCB 材料、叠层以及每层中走线宽度/间隙的识别,以满足所需的阻抗。PCB设计中使用的两种常见传输线类型是带状线和微带线。

带状线的信号迹线夹在两个参考平面之间。微带线的信号线走线在外层,只有一个参考平面。两者之间的选择取决于信号速度要求、设计复杂性以及驱动器 IC 的扇出布置。一般来说,带状线不太容易受到噪声的影响,而微带线提供更快的信号速度路径。

一旦定义了 PCB 材料、叠层和传输线类型,设计人员就需要决定如何路由高速信号。在考虑信号走线时,重要的是选择一条干净且短的走线,其下方有一个未中断的参考平面。这让电流以一致的阻抗传输到接收器,并通过阻抗最小的路径返回到源,该路径是与信号迹线直接相邻的参考平面。常见的返回路径问题包括 (a) 当参考平面中存在不连续性时和 (b) 当路由信号改变层时没有参考平面跟随。上述中断返回路径的后果是信号反射和振铃。

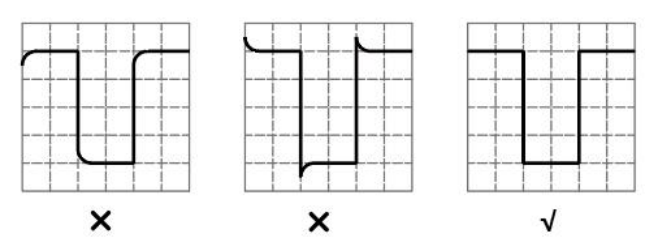

信号反射和振铃是信号完整性设计不佳的直接结果。驱动器、传输线和接收器阻抗都可能导致信号反射。如果信号在向下传播时遇到 PCB 瞬时阻抗的变化,部分信号将反射回其源并导致信号失真。这种瞬时阻抗的变化称为阻抗不连续性。当由于阻抗不连续而出现多次反射时,就会出现振铃。如果驱动器、互连传输线和接收器具有相同的阻抗,则不会出现反射或振铃。因此,在元件和互连之间匹配相同的阻抗是减少振铃的关键。

串扰是由于 PCB 走线的电容和电感特性导致的信号耦合造成的,它可能是由于多个信号相互耦合而造成的,因为它们的布线太近或信号返回路径彼此太近。当布线走线和返回路径与其他信号走线的距离是走线宽度的两倍时,可以最大限度地减少串扰。振铃也会导致串扰的可能性;较少的振铃转化为较少的串扰。

虽然这里没有讨论,但终端拓扑、走线的长度、信号的传播速度和走线的形状都需要考虑。

以下是维护 SI 应遵循的实用设计规则的摘要:

在原理图设计期间识别所有高速信号。

如果可能,在顶层和底层布线最高速度的信号。

每个高速连接都必须被视为传输线对的一部分,以 100 或 90 Ω 差分对和 50 Ω 单端方式布线。

将信号迹线与返回路径保持一层电介质。任何偏离此值的行为都会增加辐射发射、降低信号完整性并降低抗扰度。

始终为高速信号提供良好的接地参考。

避免返回路径不连续,例如参考平面中的空隙。

如果高速信号过渡层和改变接地参考平面,则必须在信号过孔旁边放置一个返回过孔。

对于差分布线,在信号及其返回路径方面尽可能保持正负走线平衡,并满足线对内和线对间长度匹配要求。

保持线对间距大于 2 倍的线宽规则。

与其他接口保持大于 3 倍的线宽间距。

没有直角转弯,因为它们会在迹线上增加电容。

尽量减少高速信号走线的过孔(层转换)数量。

尽量减少沿高速信号走线的任何短截线,包括从通孔引入的短截线。

通过使高速信号远离嘈杂的信号、时钟和开关模式电源来保护它们。

电源完整性

电源完整性 (PI) 是通过在系统内部提供符合处理器和所有其他组件所需电源条件的电源传输网络 (PDN) 来实现的。PDN 是传输平面形式的互连链,通过 PCB、封装和片上路由从稳压器模块 (VRM) 向晶体管本身供电。

PI 比 SI 更难可视化,事实证明,有数十个和数百个节点连接在同一电源平面中,每个节点都会影响 PDN 中的整体阻抗,而 SI 仅处理驱动器和接收器。PI 问题难以重复和排除故障。因此,建议在布局前和布局后 PCB 设计阶段进行完整的 PI 研究。虽然完整的 PI 分析需要高级且通常昂贵的 PI 仿真工具,但我们将在此处坚持设计基础。

高速数字设计中的良好 PI 系统有两个基本目的。首先,它为交换信号提供稳定的电压参考(接地/返回路径)。其次,它以可接受的噪声和容差将电源分配给所有逻辑器件,以保持芯片焊盘上的电压恒定。

听起来很简单,但在高速 PCB 设计中需要实现一些事实。首先,典型的 BGA 处理器通常有数百个电源和接地球,需要数十个电源电压。其次,所有这些电源引脚都消耗许多安培的电流。因此,当器件工作时,所有这些消耗安培电流的电源引脚同时加载所有高频电源电压。

考虑到这一点,PI 研究不再只是单纯的直流分析,而是涉及从 VRM 到 IC 焊盘的每个电源轨中高频瞬态负载的研究。

电源完整性的基本设计考虑从高频传输平面行为开始。与 SI 的传输线类似,PI 分析的关键是将所有电源轨视为传输平面并分析其特性阻抗。为了实现良好的电源完整性,希望 PDN 具有尽可能低的阻抗。可能会产生高频瞬态噪声,如果被忽视,可能会传播到整个电路板。

主要挑战是 PCB 中的 PDN 互连都具有电感特性。元件安装、PCB 走线、电容器和过孔都表现出电感。这表明阻抗随着瞬态频率的增加而增加。由于 VRM、电容器、PCB 叠层、电源/接地层和 IC 在不同频率下都有不同的特性阻抗,因此仔细选择元件和放置位置是降低传输层阻抗的方法。

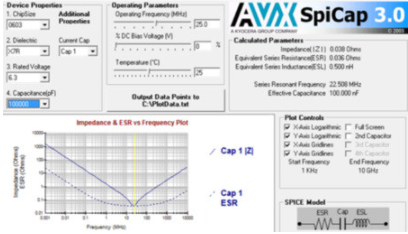

图 1 和图 2 展示了电容器在高频下的电感特性以及典型 PDN 的等效电路。图 1 是使用 AVX 的 SpiCap 仿真工具的 0603、X7R、1-uF 电容器阻抗与频率图的示例。图的左半部分显示电容在 0 到 22.5 MHz 之间的特性阻抗中占主导地位,右半部分显示电感在大于 22.5 MHz 的频率中占主导地位。

1. 0603、X7R、1-uF 电容器的阻抗与频率图示例。

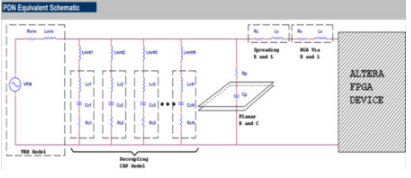

图 2 是一个 PDN 等效电路,说明了同一传输平面的每个互连的电阻、电容和电感特性。所有这些物理现象都需要作为 PI 分析的一部分进行深入研究。

2. 显示的是从 Altera 的 PDN 工具捕获的典型传输平面的 PDN 等效原理图。

理想情况下,我们希望使整个传输平面的阻抗尽可能低。由于许多因素会影响阻抗,因此需要为电路板上所有芯片的每个电压轨单独且独立地计算目标阻抗。在每个电源轨中,由于芯片的特定电流要求,目标阻抗可能随频率而变化。在指定目标阻抗时,应将器件规格表中列出的每个导轨的阻抗和可接受的容差信息用作起始指南。

特定传输平面的 PDN 由不同的互连块组成,从 VRM 到大容量去耦电容器,再到通孔,再到电路板上的走线和平面。然后是额外的去耦帽、封装的焊球或引线、封装中的互连以及芯片上的焊线和互连。每个互连块都有助于传输平面的特性阻抗。在分析 PDN 时,首先要研究每个互连轨道,然后是传输平面,然后是整个 PDN 系统。

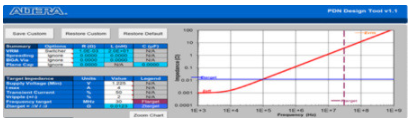

Altera PDN 设计工具可以说明每个 PDN 互连对不同频率带宽中同一传输平面的特性阻抗的影响。该工具可以通过 Altera 的有效 Quartus II 软件许可证下载。通过将目标阻抗设置为 12.3 mΩ 开始设计过程,然后通过每个 PDN 互连。

低频阻抗,范围从直流到 10 kHz,由 VRM 设置。VRM 输出通常为毫欧级,从 DC 到 10 kHz。

3. 显示的是 VRM 特性阻抗。

VRM PCB 布局需要考虑的实用技巧是:

最大化金属厚度。

使用足够宽的电源走线。

使用多个并行的电源和接地过孔。

与 VRM 并联的大容量电容器可将阻抗降低 10 至 100 kHz。

4. 显示的是大容量电容器的特性阻抗。

选择合适的大容量电容器的实用技巧是:

遵循大容量电容器值的参考设计。

遵循设计指南以优化大容量电容器的放置。

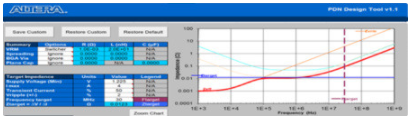

去耦电容可将传输层的阻抗降低 0.1 至 10 MHz。在靠近电源焊盘的入口点添加去耦电容可降低环路电感。选择正确的位置并选择正确数量和值的去耦电容器在这里起着重要作用。

5. 显示的是去耦电容特性阻抗。

选择正确的去耦电容的实用技巧是:

设计电容器值、主体尺寸和放置以满足阻抗规范。

降低电源接地环路面积以减少环路电感。

紧密堆叠的电源和接地可将 PDN 的特性阻抗提高 10 至 100 MHz。

6. 显示的是 PCB 电源/接地层特性阻抗。

设计电源/接地层的实用技巧是:

电源层和接地层应尽可能靠近。

放置多个用于电源和接地的过孔。

通常,对于 25 MHz 以上的频率,特性阻抗主要由 BGA 球、IC 封装和片上电容的通孔决定。为了对此建模,需要更高级的仿真工具。

关于去耦电容和电源/接地层的其他一些注意事项是:

电流总是走阻抗最小的路径。在这些高频下,PDN 环路电感、电容值和连接到电源引脚的电容器的位置决定了阻抗。

本地去耦电容应尽可能靠近处理器电源和接地引脚。使用背面电容器时,每个电容器都应有自己的通孔直接连接到接地层和电源层。

电源和接地过孔和平面应尽可能靠近。

PI 的实用设计规则是:

在相邻层上使用电源层和接地层,并使用尽可能薄的电介质。

在去耦电容焊盘和通向埋入式电源/接地层的通孔之间使用尽可能短且宽的表面走线。

将电容器放置在回路电感最低的地方。

使用 SPICE 模型来帮助选择最佳数量的电容器及其值,以使阻抗曲线低于目标阻抗。

本地去耦电容必须尽可能靠近处理器引脚放置。

定向电容器以最小化环路电感。

在返回路径中放置局部过孔。

由于每个数字设计中的时钟速率和信号速度都更高,因此对 SI 和 PI 的关注对于设计性能良好的产品至关重要。尽管我将 SI 和 PI 解释为单独的主题,但它们密切相关,并且它们的问题可以相互影响。此外,经过仔细考虑 SI 和 PI 设计的高速 PCB 通常具有最小的电磁干扰问题。

审核编辑:郭婷

-

电源

+关注

关注

185文章

18992浏览量

264651 -

处理器

+关注

关注

68文章

20339浏览量

255346 -

pcb

+关注

关注

4418文章

23979浏览量

426381

发布评论请先 登录

IDT信号完整性产品:解决高速信号传输难题

PK6350无源探头在高速数字总线信号完整性测试中的应用案例

高速接口如何选用低电容TVS管?信号完整性与防护性的双重考量

Samtec高速线缆深入解析:高速信号完整性的关键技术

是德DSOX1204A示波器在电源完整性测试中的关键优势

了解信号完整性的基本原理

Samtec虎家大咖说 | 浅谈信号完整性以及电源完整性

高速接口如何选用低电容MDDTVS管?信号完整性与防护性的双重考量

信号和电源完整性基础对于高速PCB至关重要

信号和电源完整性基础对于高速PCB至关重要

评论