电子领域的某些角落几年或几十年都没有重大的技术升级。无源电子元件就是一个很好的例子。然后还有嵌入式可编程逻辑。

电子领域的某些角落几年或几十年都没有重大的技术升级。无源电子元件就是一个很好的例子,因为不能从电阻器等设备中获得更多的性能或成本,至少在没有材料革命的情况下是这样。另一个是电池市场,该市场的产品总体上已根据需求进行了优化。

然后还有嵌入式处理空间。没错,逻辑。具体来说,通用可编程逻辑。

2011 年,Xilinx 和 Altera(现为 Intel)分别发布了 Artix-7 和 Cyclone V GT。这些器件中的每一个都包含少于 100K 的逻辑单元(Xilinx 部件为 50K,Cyclone V 器件高达 77K),但在汽车子系统等应用中提供了 I/O 灵活性、逻辑和低功耗的完美组合从工业自动化设备到通信基础设施。

然后,什么都没有。近十年来,在 FPGA 的低功耗、通用、低于 100K 逻辑单元类中没有引入新器件。

为什么不?好吧,有几个因素在起作用。首先,许多利用这些设备的终端系统都是长生命周期部署的行业,这些行业信奉“如果它没有坏,就不要修复它”的口号。但主要原因是两家主要的 FPGA 供应商战略性地从传统的嵌入式市场转型,以在数据中心等环境中获得更高利润的业务,这些环境需要具有 100 万个或更多逻辑单元的设备来实现工作负载加速。

在没有其他竞争产品的情况下,Artix-7 和 Cyclone V GT 的尺寸、功耗、I/O 速度、I/O 密度和软错误率 (SER) 多年来一直保持现状。

改变 CMOS 是唯一不变的

当然,即使在电子领域最静态的部分,变化也是唯一不变的。Lattice Semiconductor 的 Certus-NX 产品线最近改变了低于 100K 逻辑单元的通用 FPGA 市场。

Certus-NX FPGA 可提供 17K 到 40K 逻辑单元,并且与前面提到的替代方案一样,包括硬化的 5 Gbps PCIe 通道。但是,尽管莱迪思器件在这些参数上具有可比性,甚至包括更少的 RAM 和更少的 DSP 乘法器,但它们的差分 I/O 速度提高了 70%,I/O 密度提高了两倍,功耗降低了 4 倍。

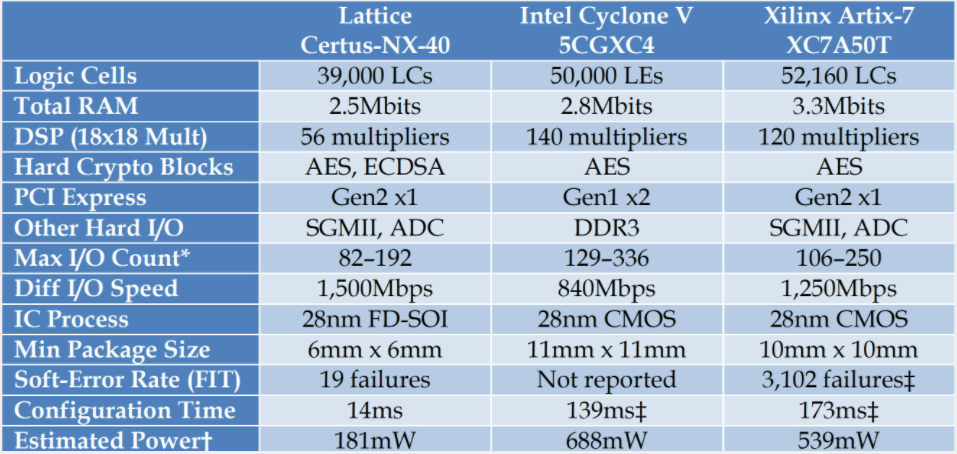

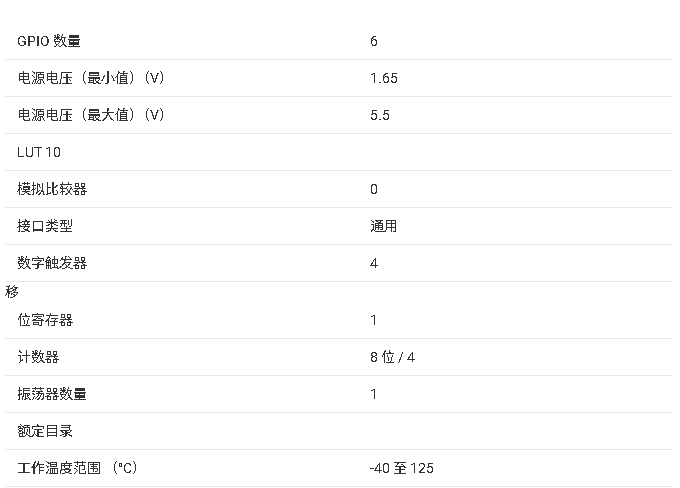

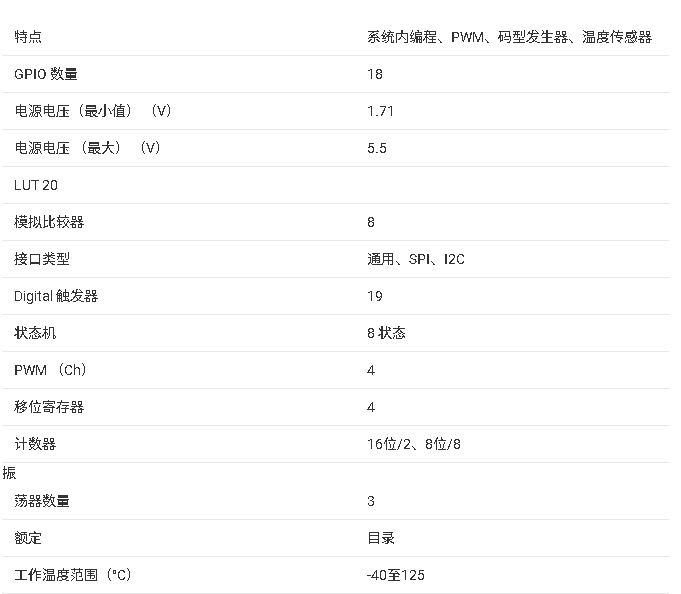

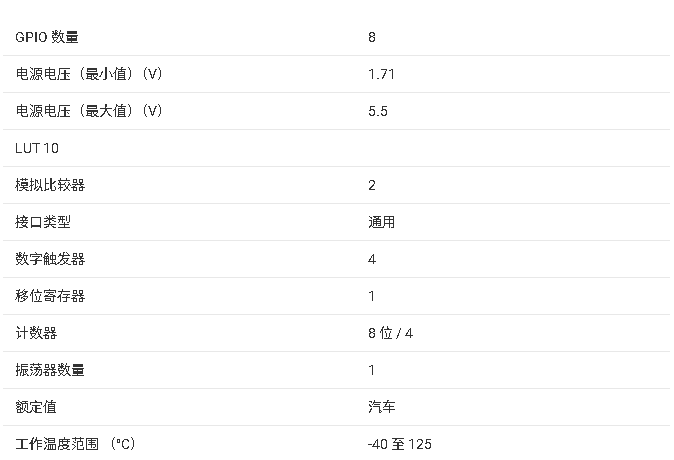

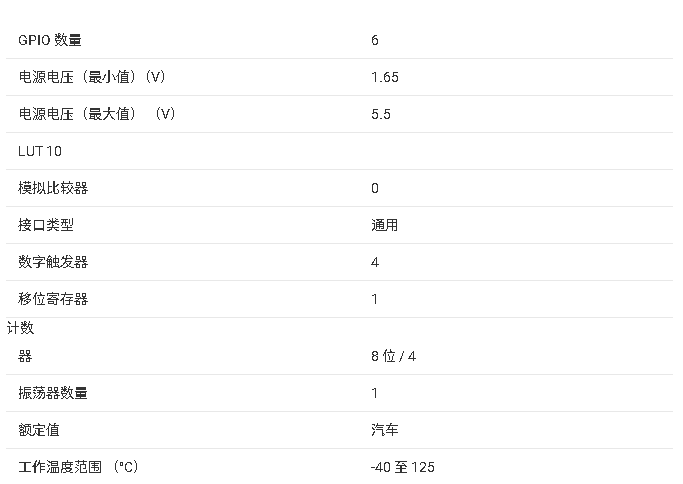

表 1. Certus-NX 产品组合利用 28 nm FD-SOI 工艺技术来降低功耗、提高软错误率 (SER) 和优化性能。

它们的尺寸也大约只有一半,尺寸仅为 6 毫米 x 6 毫米。

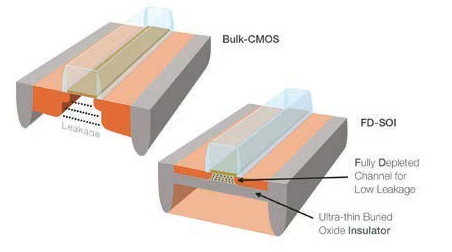

Certus-NX 设备通过摩尔定律的技巧实现了这些性能和效率提升。虽然 Lattice、Intel 和 Xilinx FPGA 均在 28 nm 节点上制造,但 Certus-NX 平台采用完全耗尽的绝缘体上硅 (FD-SOI) 工艺技术,其寄生电容低于体 CMOS(图 1 )。这允许体偏置,或者通过在晶体管下方的氧化物绝缘层上传递可编程电压来提高晶体管的性能或功率效率。

图 1. FD-SOI 工艺技术通过体偏置等技术提高了功耗和性能。

尽管 FD-SOI 使用了成熟的制造技术,但它可以生产更小的芯片尺寸,并且比标准 CMOS 具有更高的可靠性。该技术几乎消除了 SRAM 中的 SER,这有助于 Certus-NX 设备的平均故障间隔时间 (MTBF) 是竞争对手的 150 倍以上。

为了进步而进步

Certus-NX 的其他现代化包括对 ECDSA 加密算法的支持,以及 3 ms I/O 配置和 14 ms 设备配置,所有这些都与上述节能相结合,为连接和电池供电的设备提供了坚实的基础。

但同样重要的是,尺寸、性能、可靠性和功耗的改进也代表了传统嵌入式应用程序向前迈出的重要一步,无论是传统部署还是新安装。让我们不要忘记这些系统的全球足迹,为了进步而进步,给我们留下一个没有创新的十年。

审核编辑:郭婷

-

CMOS

+关注

关注

58文章

6241浏览量

243484 -

嵌入式

+关注

关注

5210文章

20692浏览量

337606 -

电池

+关注

关注

85文章

11625浏览量

144681

发布评论请先 登录

XR77103:通用3输出可编程降压调节器的卓越之选

PSoC 4200L:可编程系统芯片的卓越之选

探索UPSD3212A/C/CV:集成8032 MCU、USB与可编程逻辑的闪存可编程系统设备

SDRAM工业动态随机存储器在可编程逻辑控制器(PLC)的应用

MAX262微处理器可编程通用有源滤波器:设计与应用指南

Zynq全可编程片上系统详解

京微齐力亮相2025国际现场可编程技术大会

思尔芯邀您共聚 FPT 2025,赋能可编程技术新未来

TPLD2001-Q1 汽车级可编程逻辑器件技术文档摘要

通用可编程逻辑的重大技术升级

通用可编程逻辑的重大技术升级

评论