RISC-V 被称为开放标准指令集架构 (ISA),其基本指令已被冻结以最小化复杂性。但最近它添加了广泛的自定义扩展和增强功能,使其在构建特定应用系统的 SoC 设计人员中越来越受欢迎。

这些架构中采用的定制功能通常通过硬件/软件协同设计策略得到增强,该策略优化软件以最大限度地发挥 RISC-V 处理器 IP 的专业能力。

但无论系统是否在软硬件协同设计环境中开发,构建稳定的 SoC 设计和验证流程的过程仍然涉及大量设置和耗时的手动更改。研究估计 SoC 验证占用了 SoC 总设计时间和成本的 50-80%,而且使用 RISC-V 处理器的验证工程师的工作量比 Arm SoC 还要多,因为 CPU 本身以及任何定制都必须经过验证。

RISC-硬件设计验证提供商 Imperas 最近的一份声明称:“开源 IP 的日益普及也促进了将验证作为进货质量检查作为 SoC 项目初始阶段的一部分的团队的增长。” V 处理器模型和用于软件仿真的虚拟原型,读取。“此外,修改或扩展基本核心功能的设计选项从一开始就取决于一个有效的设计验证框架。”

围绕可定制的 RISC-V IP 规范化验证

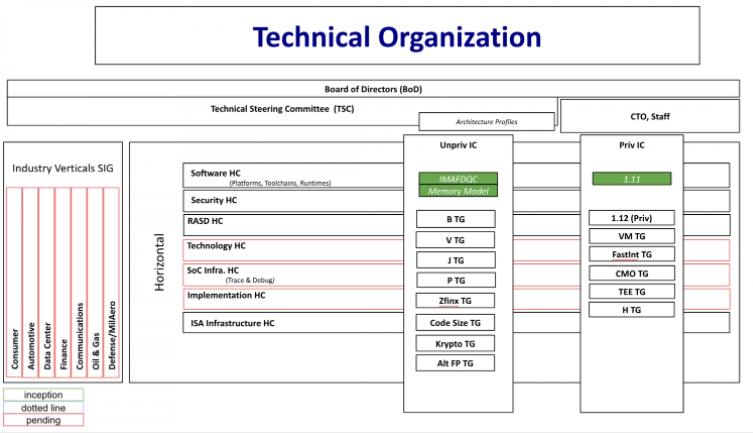

事实上,随着 RISC-V 的成熟,越来越多的设计团队选择“修改或扩展基本核心功能”,以至于 RISC-V 基金会已经组织了特殊兴趣小组来规范目标用例的扩展功能集。这些工作组可以在下图的左侧看到,自春季发布该表以来,其中许多已经从待处理转变为活动。

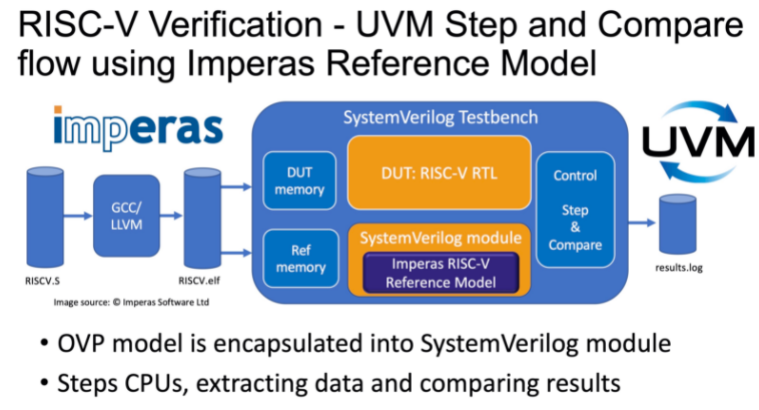

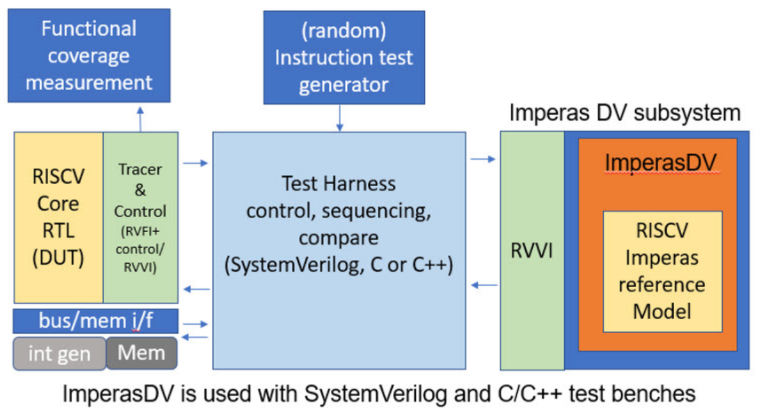

作为回应,ImperasDV 工具正在寻求通过与当前 UVM SystemVerilog 技术兼容的“黄金参考模型”来简化 RISC-V SoC 设计验证过程。它的环境采用锁步比较设计验证方法,允许在 Verilog 或 SystemVerilog 中编程的被测设备 (DUT) 运行和构建装配级程序。这有助于解决异步事件,从而在发现错误时减少调试分析时间。

该工具的主要组成部分是:

指令测试生成器

RTL DUT 子系统

功能覆盖测量

测试台/线束

Imperas DV 子系统

该工具的外壳可容纳整个 RISC-V ISA,包括特权操作模式,并与最新的 Vector、DSP/SIMD、Bitmanip 和 Crypto (Scalar) 扩展兼容。从架构的角度来看,ImperasDV 提供了一个支持 RISC-V 验证接口 (RVVI) 标准的验证环境。这简化了客户 RTL、参考模型和测试平台之间的集成。

如前所述,该集成有助于复杂超标量流水线的锁步和比较验证,并且该平台可以容纳多个硬件线程并完成无序指令。Imperas 的黄金参考模型确保平台评估的操作数据正确执行,即使跨不同版本,这要归功于对特定修订的可配置版本控制支持。

开源协同设计现在开始

ImperasDV RISC-V 验证工具链已被许多半导体行业领先的 RISC-V 供应商采用,其中一些供应商已经拥有可工作的硅原型,目前正致力于第二代设计。其中包括 Codasip、EM Microelectronics (Swatch)、NSITEXE (Denso)、Nvidia Networking (Mellanox)、OpenHW Group、MIPS Technology、Seagate Technology、Silicon Labs 和 Valtrix Systems,以及其他尚未公开的公司。

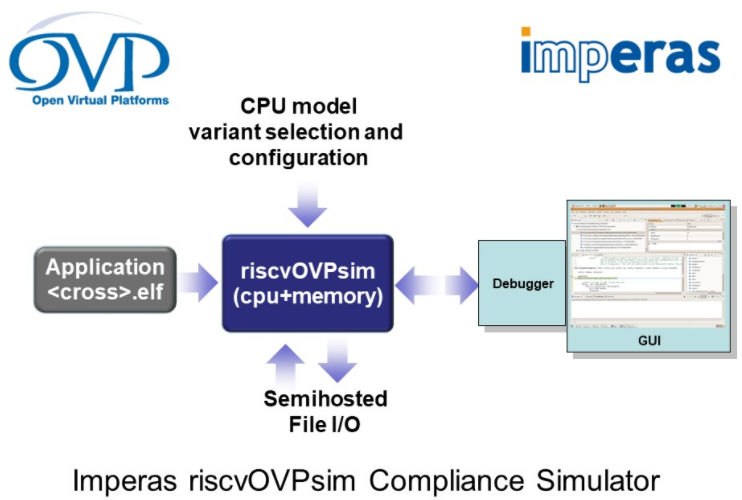

当然,我们还没有解决硬件/软件协同设计等式的另一面:嵌入式软件开发。在这里,Imperas 还通过建模和仿真解决方案加快设计周期,只是这些解决方案基于开源开放虚拟平台 (OVP) 模型。

该公司的riscvOVPsim 指令集模拟器 (ISS)允许以高达 1,000 MIPS 的速度开发和调试针对 RISC-V 处理器目标的代码。它利用 Imperas 的 OVP 快速处理器模型库来提供指令精确的单核 RISC-V 配置和变体,甚至被 RISC-V 基金会的合规性框架和测试套件使用。

最重要的是,可以从 GitHub 免费下载riscvOVPsim,并且可以在www.ovpworld.org/riscvOVPsimPlus找到包含新 RISC-V 矢量扩展的增强测试套件。

riscvOVPsim 的可用升级包括虚拟平台开发和仿真、多核软件开发、可扩展平台套件和多处理器主机 (MPonMP) 加速软件上的 QuantumLeap 多处理器目标。

Imperas 产品组合以及来自快速发展的 RISC-V 生态系统的其他工具,为您今天开始自己的开放式处理器设计提供了足够的资源。

作者:Brandon Lewis,Saumitra Jagdale

审核编辑:郭婷

-

处理器

+关注

关注

68文章

20325浏览量

254692 -

嵌入式

+关注

关注

5209文章

20624浏览量

336756 -

RISC-V

+关注

关注

49文章

2941浏览量

53519

发布评论请先 登录

新思科技ImperasDV解决方案让RISC-V处理器验证效率翻倍

新思科技VC Formal解决方案在RISC-V验证中的应用

重磅合作!Quintauris 联手 SiFive,加速 RISC-V 在嵌入式与 AI 领域落地

Andes晶心科技推出全新32位RISC-V处理器D23-SE

直播预约 |开源芯片系列讲座第30期:“一生一芯”计划——从零开始设计自己的RISC-V处理器芯片

为什么RISC-V是嵌入式应用的最佳选择

基于E203 RISC-V的音频信号处理系统 -协处理器的乘累加过程

提高RISC-V在Drystone测试中得分的方法

明晚开播 |开源芯片系列讲座第28期:高性能RISC-V微处理器芯片

直播预约 |开源芯片系列讲座第28期:高性能RISC-V微处理器芯片

RISC-V和ARM有何区别?

定制RISC-V处理器简化设计验证

定制RISC-V处理器简化设计验证

评论