高速的数据转换在设计中有很多和一般数据转换设计中相似的问题,需要可靠的设计和稳定的结构。从基础上来说,两者并无二致,但受限于芯片的限制,高速数据转换系统中更能窥见前沿的动态性能发展。在一个高速数据转换系统中,放大器、DAC、ADC这些都是必不可少的。市面上,现在有两种常见的ADC出现在此类应用中,分别是全并行ADC和逐次逼近ADC。

这两种常见的高速ADC结构,每一种都有自己独特的特点,每一种结构在精确度、动态性能、成本等出多方面都有不小的差异。在实际的设计中如何选择合适结构的ADC是实现系统最佳性能的关键。

最快速的转换选择

我们是在高速这个条件下来看这些ADC,在所有高速转换器件中,最简单最快的就是全并行ADC。这么判断的很重要的一点原因在于全并行ADC进行的转换只进行在单一方向上,这也是为什么将其命名为全并行。全并行ADC对于高接受度接收器性能来说,速度快而且稳定性好,但它可能具有高输入电容,并且需要设计到系统的数字部分的高速接口。

全并行ADC的分辨率每高一位,其设计复杂程度以及成本都会大大增加。首先,全并行ADC内部的比较器数量需要加倍,这意味着全并行ADC中的大部分面积都需要翻倍,而且功耗也随着比较器增多而增大也是必然的。这还没算上解码器、驱动的相关考量,总的来看,分辨率每增加一位,尺寸、功耗、输入电容均为大幅增长,这一点在全并行ADC上尤为明显。

有一些技术可以在全并行ADC设计上减少尺寸和功耗。折叠技术允许在ADC的动态范围内重复使用一组比较器两次,减少了比较器的数量从而节省系统面积降低功耗。而插值技术是采用相邻比较器之间的平均值来减少前置放大器的数量,降低ADC的输入电容。但不论哪一种减小尺寸需求降低功耗的技术,都有一定的缺点,即便是CMOS双极技术也会存在补偿偏高的问题。

动态性能影响全并行ADC能否获得准确的数字化高频信号,窗口延迟变形和输入带宽形象甚大。全并行ADC的输入带宽是由一个小信号和大信号构成(有些情况大信号带宽由输入回转率决定)。当全并行ADC输入电容很高时,为了达到高带宽需要驱动的译码器阻抗要尽可能低,低阻源可以通过运放或缓冲器来提供。另一个限制全并行ADC动态高频性能的是窗口时间,这个是由比较器来决定的。

在全并行ADC位数和性能之间寻找平衡点,对实现全并行ADC最小尺寸和功耗起着关键作用。

逐次逼近ADC的全面发展

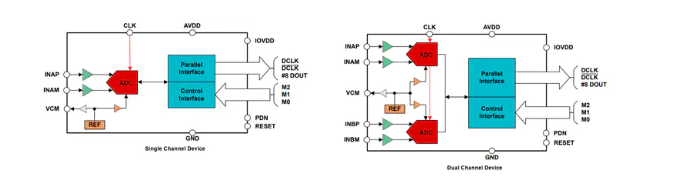

逐次逼近ADC之所以这么流行,性价比高肯定是其中一个原因。其结构很直观,能实现的性能变化很大,分辨率可以从8位变化到16位,转换速率可以从400ns变化到25µs,其简洁的结构设计有很广泛的应用。

现在厂商会将数字校正添加到传统的逐次逼近算法中,前八位只转换至8位的精度,然后转换器进入保持状态将转换校正至12位精度。这种有校正功能的转换器相比于传统的逐次逼近型ADC会前八位工作于高采样率。

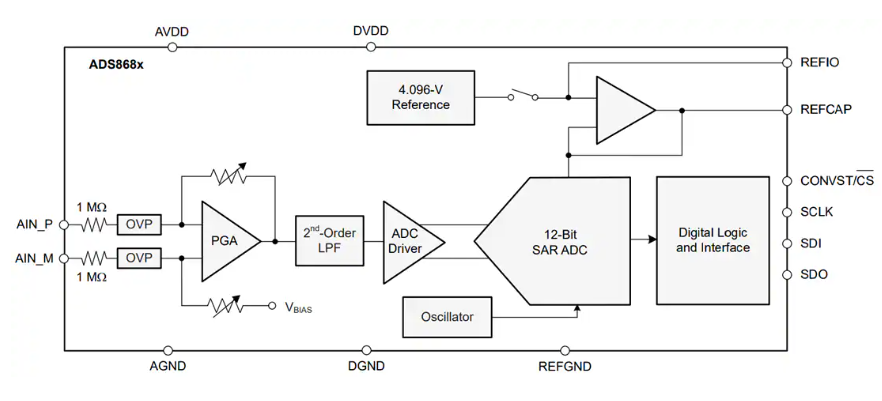

(逐次逼近ADC,TI)

逐次逼近ADC的结构有一个不同于其他ADC结构的特点,其ADC的线性度依赖于数模转化器的线性度。精密DAC的发展相当程度上给逐次逼近ADC带来了不少好处,较为明显的就是逐次逼近ADC相对于其他结构更宽的温度范围。而且转化器产生连续的转换输出能减小系统模拟和数字之间影响。对于一个理想的DAC来讲,每个与数据位相对应的电容应该精确到下一个较小电容的两倍。比较器则需要具有足够的速度和精度,尽管比较器的失调电压不影响整体的线性度,它会给系统传输特性曲线带来一个偏差。

与全并行ADC相比,逐次逼近的速度肯定是没法和其相比较,但如果是需要提高分辨率的应用,逐次逼近型只需要更精确的元件即可,而且其分辨率提高的同时设计复杂度不会像全并行ADC那样几何增长。逐次逼近结构的主要局限还是在于对于高速转换来说采样速率较低,并且其中的各个单元(DAC和比较器)需要达到与整体系统相当的精度。

小结

在高速转换应用中,如何选择合适的ADC是至关重要的,通常需要折中考虑全并行ADC的速度以及逐次逼近型DAC的低功耗和小尺寸特性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电源管理

+关注

关注

117文章

8633浏览量

148248 -

adc

+关注

关注

100文章

7946浏览量

556899 -

数据转换

+关注

关注

0文章

105浏览量

18560

发布评论请先 登录

相关推荐

热点推荐

探索MAXIM ADC0820:高速8位A/D转换器的卓越性能与应用

探索MAXIM ADC0820:高速8位A/D转换器的卓越性能与应用 在电子设计领域,高速、精准的模拟 - 数字转换是许多系统的核心需求。M

12位高速IF采样ADC——AD9433的技术解析与应用指南

12位高速IF采样ADC——AD9433的技术解析与应用指南 在电子设计领域,模数转换器(ADC)是连接模拟世界和数字世界的关键桥梁。今天,我们要深入探讨一款高性能的12位

12 位高速 ADC AD9432:性能剖析与应用指南

12 位高速 ADC AD9432:性能剖析与应用指南 在电子设计领域,高速、高精度的模数转换器(ADC)是实现信号处理和

18位2MSPS SAR ADC AD7641:高性能数据转换的理想之选

18位2MSPS SAR ADC AD7641:高性能数据转换的理想之选 在电子设计领域,高精度、高速的数据采集是许多应用的核心需求。今天,

AD4087:高速低噪SAR ADC的卓越之选

AD4087:高速低噪SAR ADC的卓越之选 在电子设计领域,一款高性能的模数转换器(ADC)对于实现精准的数据采集至关重要。AD4087

AD4084:高速低噪SAR ADC的卓越之选

AD4084:高速低噪SAR ADC的卓越之选 在当今高速发展的电子科技领域,数据采集系统对模拟 - 数字转换器(

ADC34RF55:高速高精度RF采样数据转换器的深度剖析

ADC34RF55:高速高精度RF采样数据转换器的深度剖析 在当今电子技术飞速发展的时代,高速高精度的模拟 - 数字

ADC1175:低功耗高速A/D转换器的卓越选择

ADC1175:低功耗高速A/D转换器的卓越选择 在如今的电子设计领域,A/D转换器的性能和功耗一直是工程师们关注的重点。德州仪器(TI)推出的AD

高速低功耗ADC在流量计中的应用

在工业自动化系统中,流量计是实现精确过程控制与稳定信号采集的关键设备。它负责将传感器采集的模拟流量信号转化为高精度的数字数据,供后续处理与分析。英尚微电子提供的流量计解决方案,包括高速低功耗的

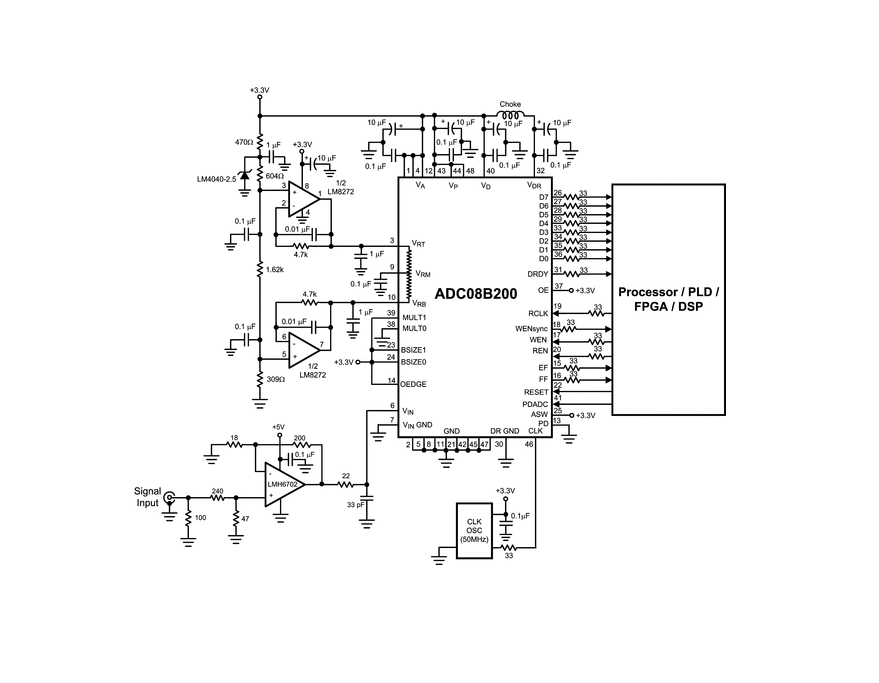

ADC08B200:高速8位A/D转换器的设计与应用指南

在电子设计领域,高速、高效的模拟 - 数字转换器(ADC)至关重要。TI的ADC08B200就是这样一款高性能的8位、200 MSPS A/D转

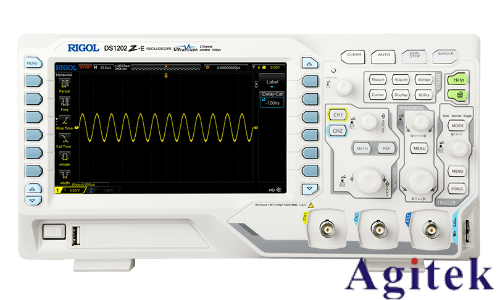

普源DS1102示波器ADC在高速测试中的技术优势解析

在现代电子测试领域,高速信号采集与分析对测试设备的性能提出了严苛要求。普源DS1102系列示波器凭借其先进的ADC(模数转换器)技术,在高速测试场景

Texas Instruments ADC3908Dx/ADC3908Sx 8位高速ADC数据手册

Texas Instruments ADC3908Dx/ADC3908Sx 8位高速模数转换器(ADC)是一系列超低功耗8位125MSPS

Texas Instruments ADS8661W 12位高速SAR ADC数据手册

Texas Instruments ADS8661W 12位高速SAR模数转换器 (ADC) 是一款基于逐次逼近 (SAR) 模数转换器 (ADC

高速数据转换中的ADC差异

高速数据转换中的ADC差异

评论