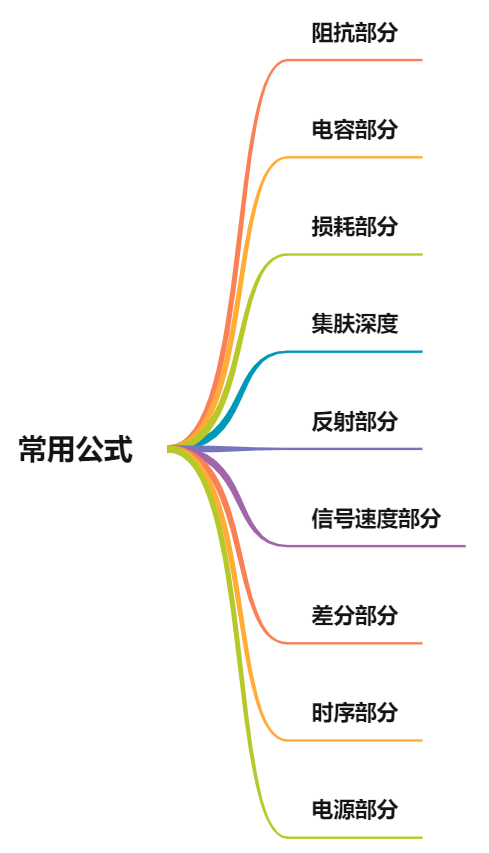

信号完整性的方向,很多时候会应用各种公式估算风险,分类别进行整理,算是抛砖引玉。

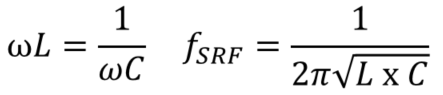

本文思维导图如下:

01

阻抗部分

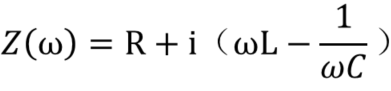

RLC 串联电路模型的阻抗为:

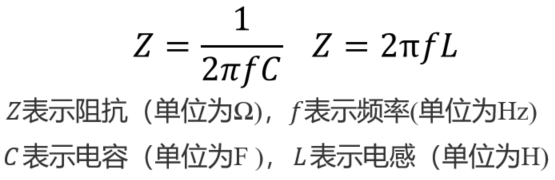

由阻抗公式, 可以推出RLC 电路阻抗最低的频率称为自谐振频率(SRF):

其实这里面还有个并联谐振(反谐振)的概念,这里不做展开。

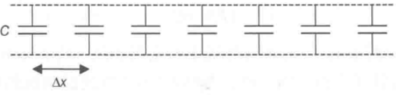

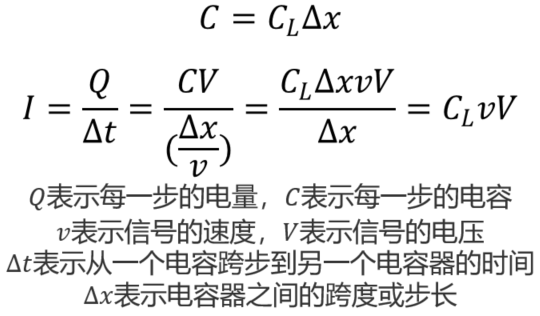

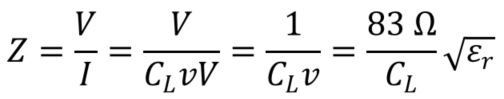

传输线的零阶模型状态下:

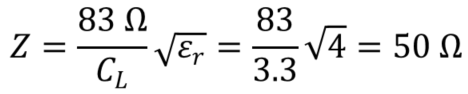

在这个阻抗计算公式里,单位长度电容取值为3.3 pF/in(后面会估算出3.5 pF/in),介电常数为4,计算出传输线的瞬时阻抗:

均匀传输线情况下,特性阻抗和瞬时阻抗相同。

这也是从侧面验证50Ω阻抗,当然传输线默认值选择50Ω还有损耗最优值等其他原因。

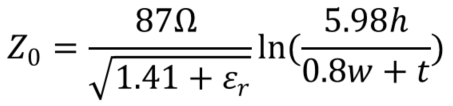

实际工作中,50欧姆的这个公式应用的比较少,可以了解下IPC推荐的近似公式。这个公式可以看出阻抗和哪些因素有关。

微带线,IPC 推荐的通用近似公式为:

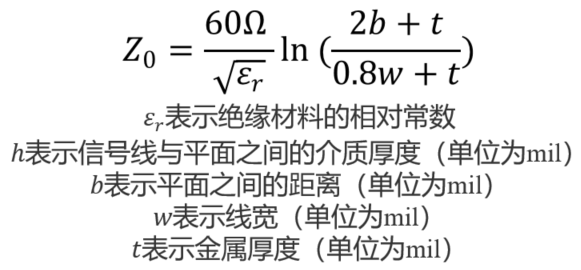

带状线,推荐的通用近似公式为:

02

电容部分

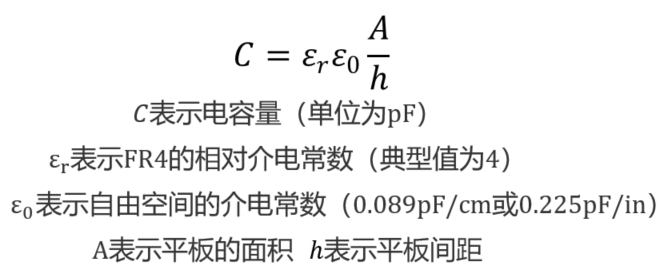

在实际PCB版图设计中,电源平面和地平面一般是相邻的,以此估算出两个平面之间每平方英寸面积的电容:

以此公式推算,电源与地平面之间的电介质厚度为10mil的话,平面之间的电容大约为100 pF/in^2。

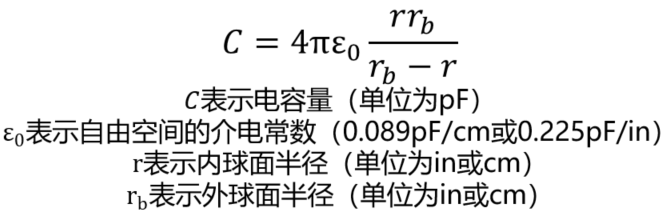

球面电容,连接器多个引脚之间的电容可以用下列公式估算:

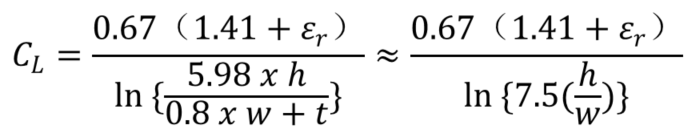

关于单位长度电容,这里分微带线和带状线情况:

微带线的单位长度电容近似为:

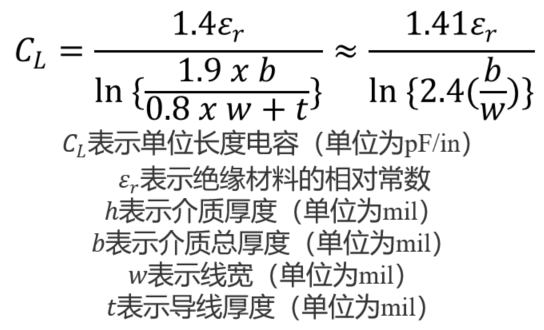

带状线的单位长度电容近似为:

经验值:FR4板上50Ω传输线的单位长度电容约为3.5pF/in。

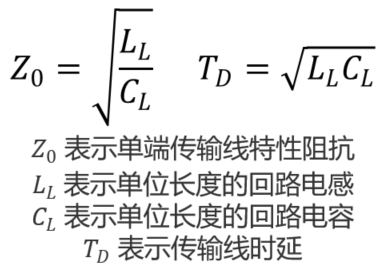

讲到单位长度电容,想到单端传输线的特性阻抗和时延由下式给出:

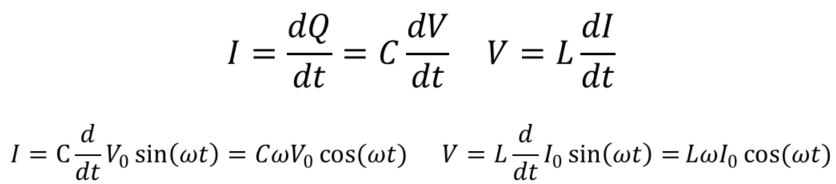

时域&频域电容电感公式:

电容器是否有电流通过,取决于两端电压的改变。

电感器两端的电压与流经电流的变化快慢有关。

注意时域与频域公式的区别。

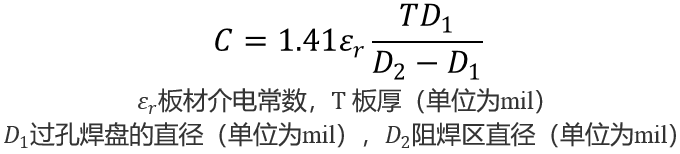

过孔寄生电容的近似公式:

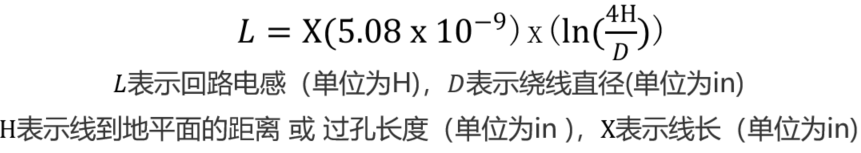

过孔或信号线回路电感近似公式:

过孔除了寄生电容和电感的影响,还要考虑残桩。有个比较严格的公式可以参考300/BR(BR代表的是比特率,这个需要注意)。

03

损耗部分

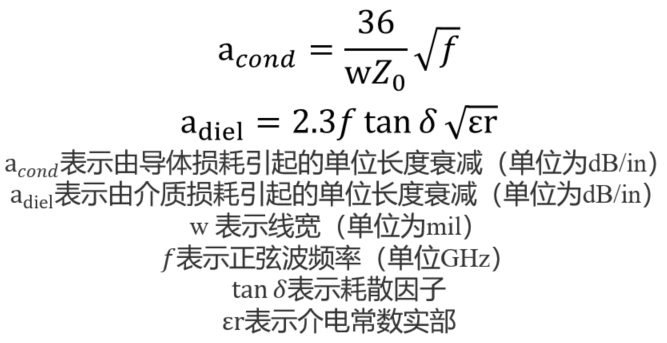

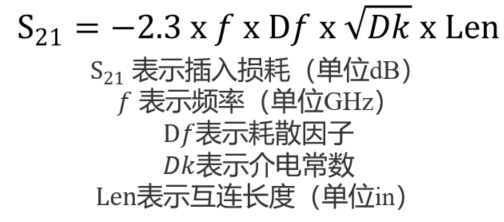

一般版图设计,高速差分线一般会布局于内层,带状线引起的单位衰减估算公式&介质引起的单位长度衰减的估算公式:

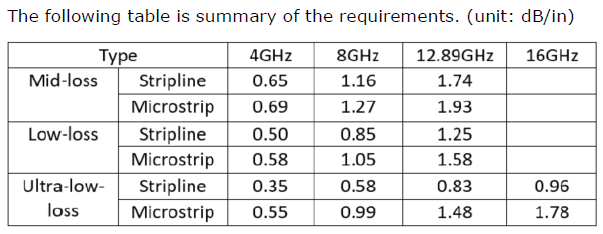

以上衰减的估算公式要和产品要求的损耗标准相区别:

高频情况下,导体损耗占得比重较小,插入损耗可以用来评估和度量链路情况:

04

集肤深度

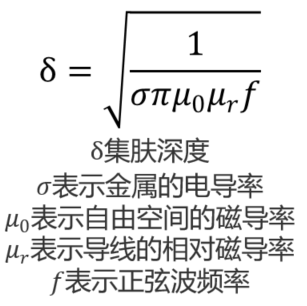

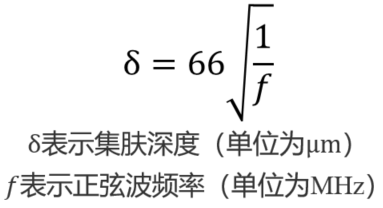

集肤深度公式:

铜的电导率为5.6 x 10^7 S/m,相对磁导率为1,集肤深度为:

05

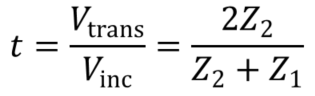

反射部分

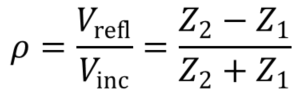

反射系数:

入射系数:

06

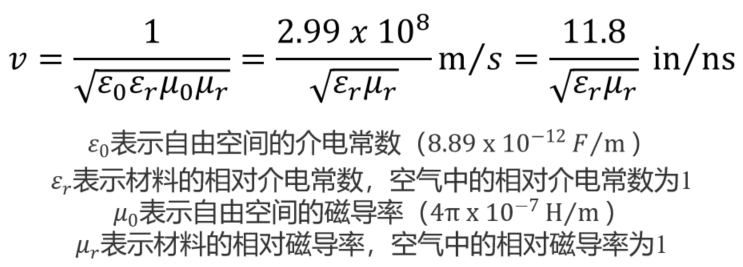

信号速度部分

信号的传播速度公式:

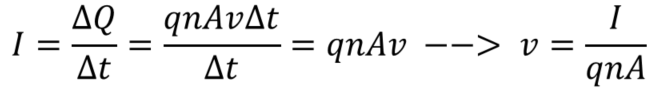

Note:信号传播速度和电子速度(1cm/s)的不同。

信号传播速度取决于周围包裹的材料和电磁转换的变化速度。这个信号速度可以反推延时,实际工作中实用性比较强。

07

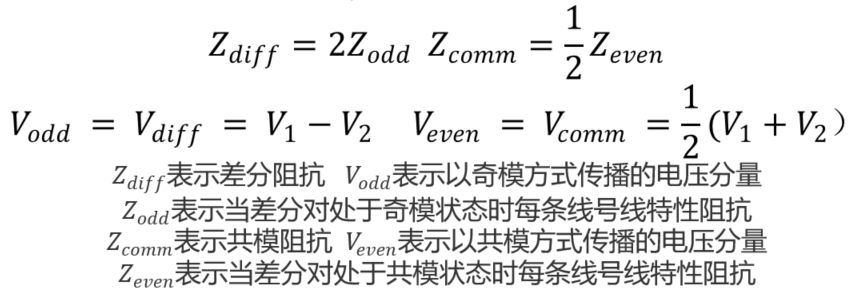

差分部分

单端转差分公式:

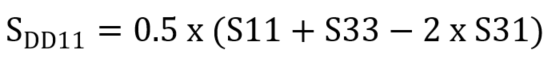

SDD11元素可以通过下式得到:

SDD21元素可以通过下式得到:

Sigrity可以直接仿差分信号线,ADS的S参数查看器可以直接查看。

08

时序部分

晶体管沟道的长短,影响电子与空穴移动的长短,进而影响开关速度的快慢,影响时钟周期的长短。

时钟频率和数据率是有关系的,这取决于编码方式。PCIe,SATA和千兆以太网采用的是NRZ(Non-Return-to-Zero)。NRZ信令方案,该方案在每个时钟周期编码2比特,基频是数据率的一半,这个基频时钟称为奈奎斯特频率。

需要注意的是,PAM-4信号, 1个符号传输2bit数据。

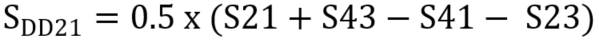

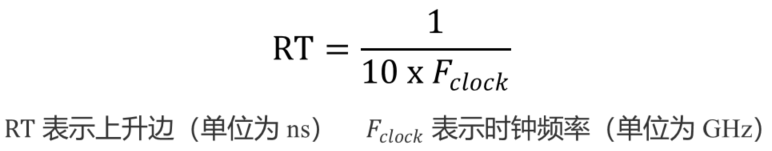

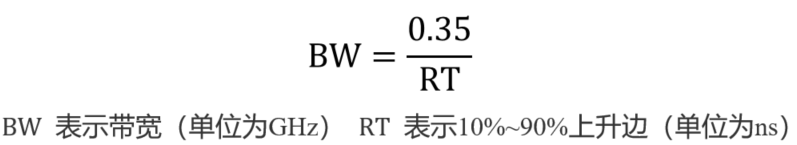

当上升边的单位为ns时,带宽的单位为GHz。ns对应GHz,MHz对应us,可以试着记一下这种对应关系,方便实际工作中对信号带宽的估算。

1/10,0.35或者是0.5之类的情况只是估算,工作中需要根据实际情况来衡量。

09

电源部分

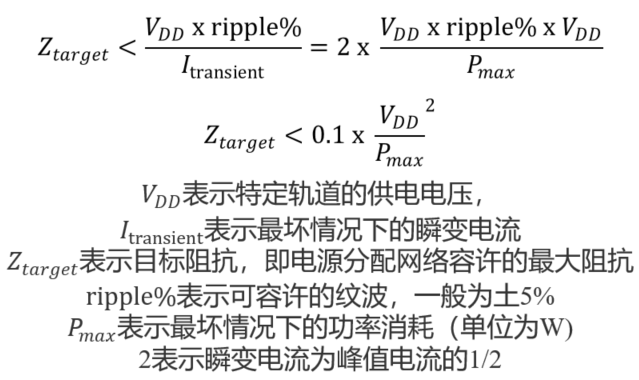

电源完整性中一个最重要的概念就是PDN阻抗。在电源路径设计过程中,就是让电源分配网络阻抗低于目标阻抗。

目标阻抗的估算公式:

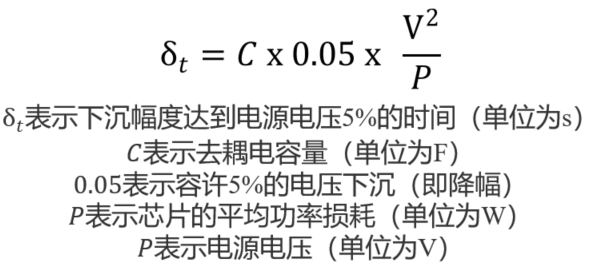

电源完整性部分,除了PDN,很大一部分就是关于去耦电容。去耦电容至少可以提供微秒级别的时间,直到电源稳压器提供足够的电流。这个地方需要了解的是,实际版图设计中,多层电路板,电源和地层相邻,存在平面电容,但是这个电容不足以对电源起到明显的作用,更多是提供低电感路径(减小自感,增大互感)。

其实,关于电感部分,公式很多,这里了解两个值,一个是85 nH ,还有一个是25 nH。

85nH代表一个圆回路电感。既然是圆,85nH/3.14 in=25 nH/in,代表单位长度的回路电感约为25nH/in。

讲到电感,提一句:为什么很多焊盘周围打了多个过孔?重要的作用就是减小电感。过孔间距和过孔长度的关系不做延伸。

九九归一,其实公式只是应用的部分,也是信号完整性不可缺少的部分。需要注意的是,公式中应用的场景和原理搞清楚,不能乱用。

审核编辑 :李倩

-

电感

+关注

关注

54文章

6290浏览量

106633 -

信号完整性

+关注

关注

68文章

1497浏览量

98237 -

串联电路

+关注

关注

6文章

162浏览量

27639

原文标题:信号完整性常用九类公式

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

IDT信号完整性产品:解决高速信号传输难题

Samtec高速线缆深入解析:高速信号完整性的关键技术

了解信号完整性的基本原理

Samtec虎家大咖说 | 浅谈信号完整性以及电源完整性

受控阻抗布线技术确保信号完整性

信号完整性测试基础知识

信号完整性常用公式解析

信号完整性常用公式解析

评论