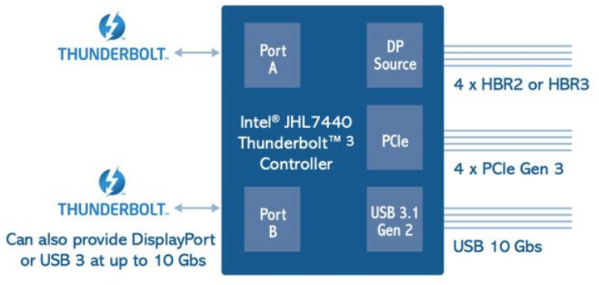

USB4.0是2019年发布的规范文档,是基于 Thunderbolt 3 协议,使用Type C接口,支持USB、DP、PCIe功能。USB4和DisPlayPort 2.0融合在一起,USB Type-C接口可以转换为DP2.0模式,用来传输音视频信号。

图片来源于网络

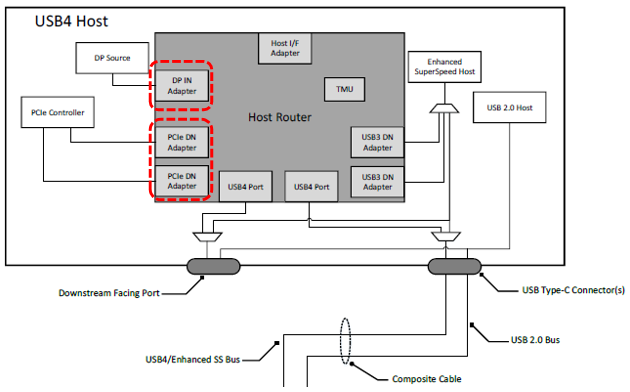

如何支持USB、DP、PCIe三种信号协议?在三种之间进行切换?文档给出的是Tunnel 技术,这样就可以最大限度发挥物理带宽性能。

外部设备收到来自USB4接口的数据,USB 2.0数据传输给USB 2.0功能模块,USB3上行端口适配器分离出USB 3.2数据传递给增强型超速功能模块,PCIe上行端口适配器分离出PCIe数据传递给PCIe功能模块,DisplayPort输出适配器分离出视频信号给DisplayPort显示模块。这样USB4主机就可以和外部设备(比如固态硬盘,移动硬盘,显示器等)之间进行传递文件和显示视频等功能。

这个技术让我想起Type C支持的拓展模式Alternate Mode。

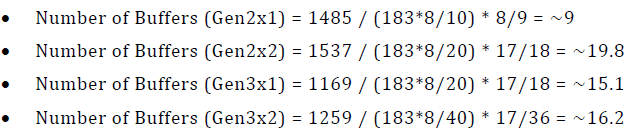

规范文档文末,给出使用Tunnel 技术,USB链路的带宽:

对前面的1485/1537/1169/1259 ns延迟时间的计算,理解得不够,这边做个记录,后面等其他串行信号学习总结后,再做比较和理解。

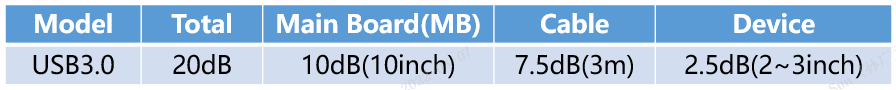

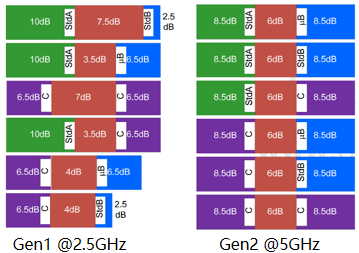

USB3.0链路给出的损耗指标:

需要注意的,Device部分的2~3inch PCB 走线,之所以给出的是一个范围,是因为2.5dB包含芯片封装和寄生效应。

这个是2008年提的一个标准。等到2012年,为了增加设备端的损耗裕量,将总损耗提高了4dB,用以终端设备损耗裕量提高。

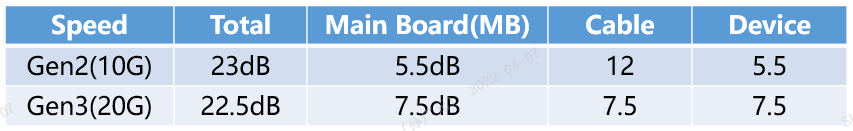

针对Gen1和Gen2不同速率链路,各部分损耗标准做了细分,同时针对不同的接口形式也给出细化指标:

以上这些是在USB3.1版本的文档给出的相关量化数据。

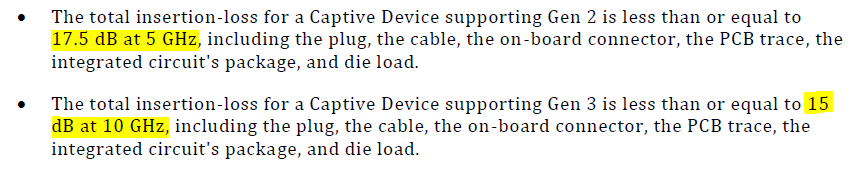

2021 DesignCon 关于USB部分的技术文档,也给出了相关量化指标:

有消费类产品就是使用的上面的标准。

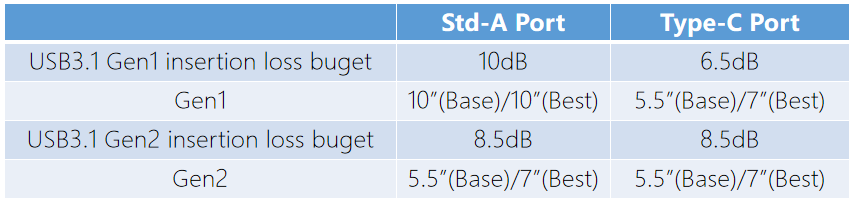

等到USB4规范文档,这里面的协和USB4有一些不同:

前文也给出过,针对Repeater中继器给出的相关标准:

会发现,相关的指标比较多,针对各种应用选择有的不同细化指标,这取决于你设计的产品和应用。

串行信号的测试,都会使用测试夹具(Fixture)。USB4规范文档这里面针对测试夹具的指标:5GHz时为0.5dB ± 0.25 dB,在10 GHz 时为1dB ± 0.25 dB。

夹具的目标单端阻抗应为42.5 Ω,也就是85Ω的差分阻抗。

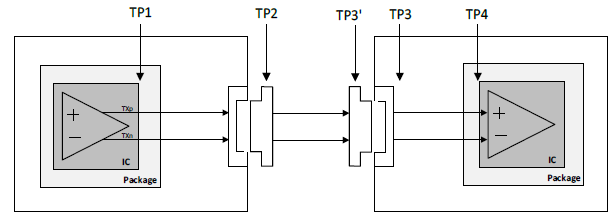

针对Gen 2 和Gen 3 测试的标准和测试点的选择都是不同的,做了细分。

链路测试点示意图:

测试指标也做了细分,即使是Gen2速率下,测试指标也有所不同:

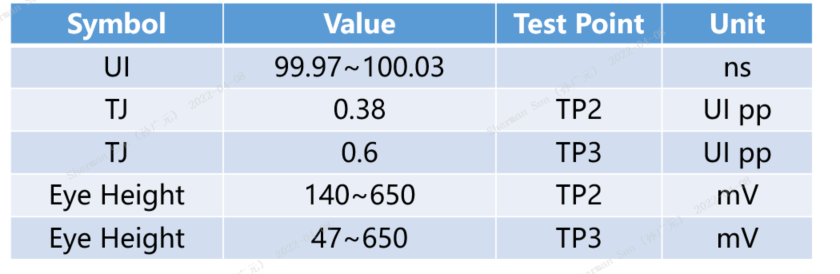

针对链路,满足相关的测试指标,给出均衡参数配置,以此来找到最优的值:

USB4设计没有做过,也没有看到最新的设计方面的文档。关于USB4设计方面的管控,可以参考USB3.2设计方面的相关指标:

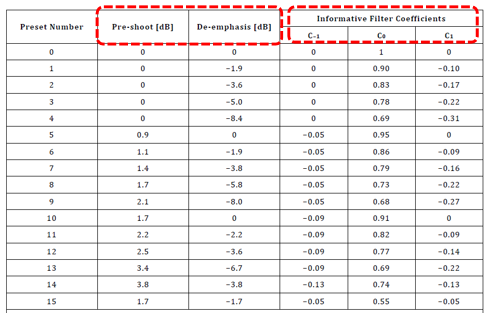

Stub Gen 2 <381um;

USB3.2针对AC 耦合电容100nF(75~265nF),USB4这里给出的范围是135~265 nF;

反焊盘的处理:

审核编辑 :李倩

-

usb

+关注

关注

60文章

8476浏览量

285847 -

适配器

+关注

关注

9文章

2138浏览量

71468 -

type-c

+关注

关注

557文章

2055浏览量

278382

原文标题:USB4.0知识指南

文章出处:【微信号:CloudBrain-TT,微信公众号:云脑智库】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

AS7173+VL171设计TypeC转DP双向8K60/4K240转接线方案电路图

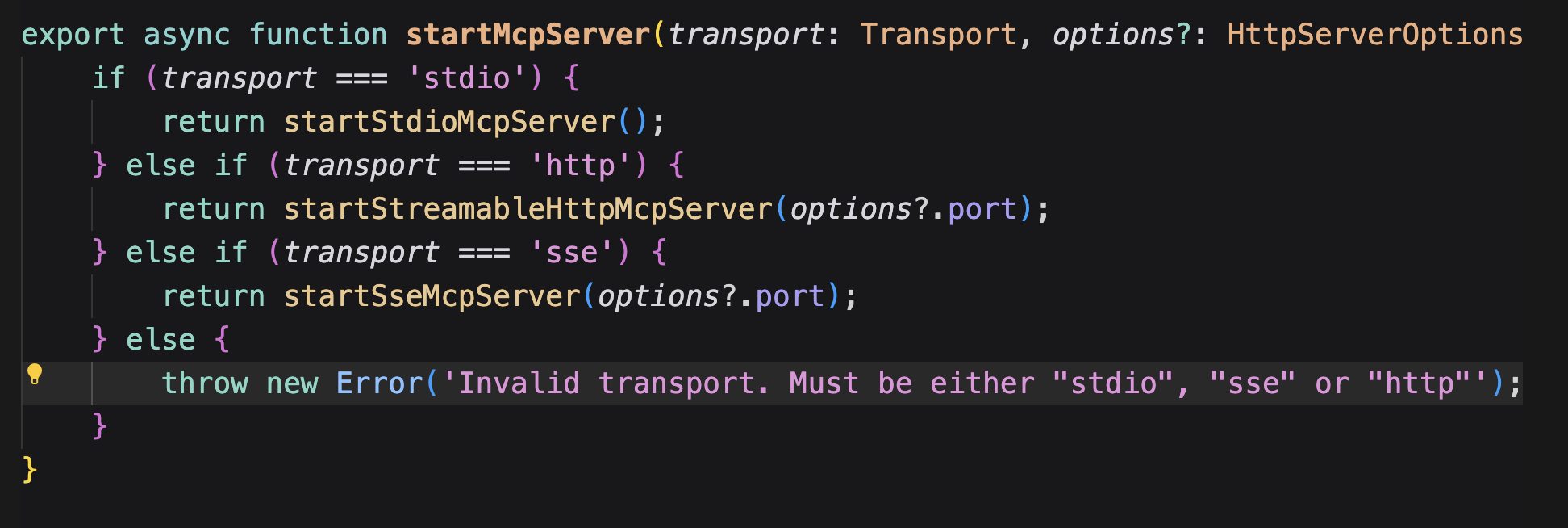

【MCP】同时支持stdio,streamableHttpless和sse三种协议的MCP服务框架

【干货】一文带你了解CAN、Modbus与LoRa三种通信协议的区别

PCIe协议分析仪能测试哪些设备?

协议分析仪需要支持哪些常见协议?

MEMS中的三种测温方式

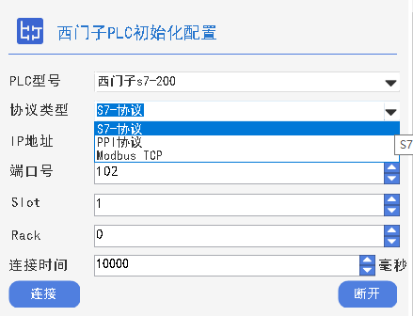

GraniStudio零代码平台支持哪些品牌PLC和协议?

IP2727_Q1至为芯用于车载USB充电输出的车规级快充协议芯片

开关电源三种控制模式:PWM/PFM/PSM

GL850G(创惟) USB2.0HUB国产替代方案-GM8220(振芯) P2P

介绍三种常见的MySQL高可用方案

nvme IP开发之PCIe上

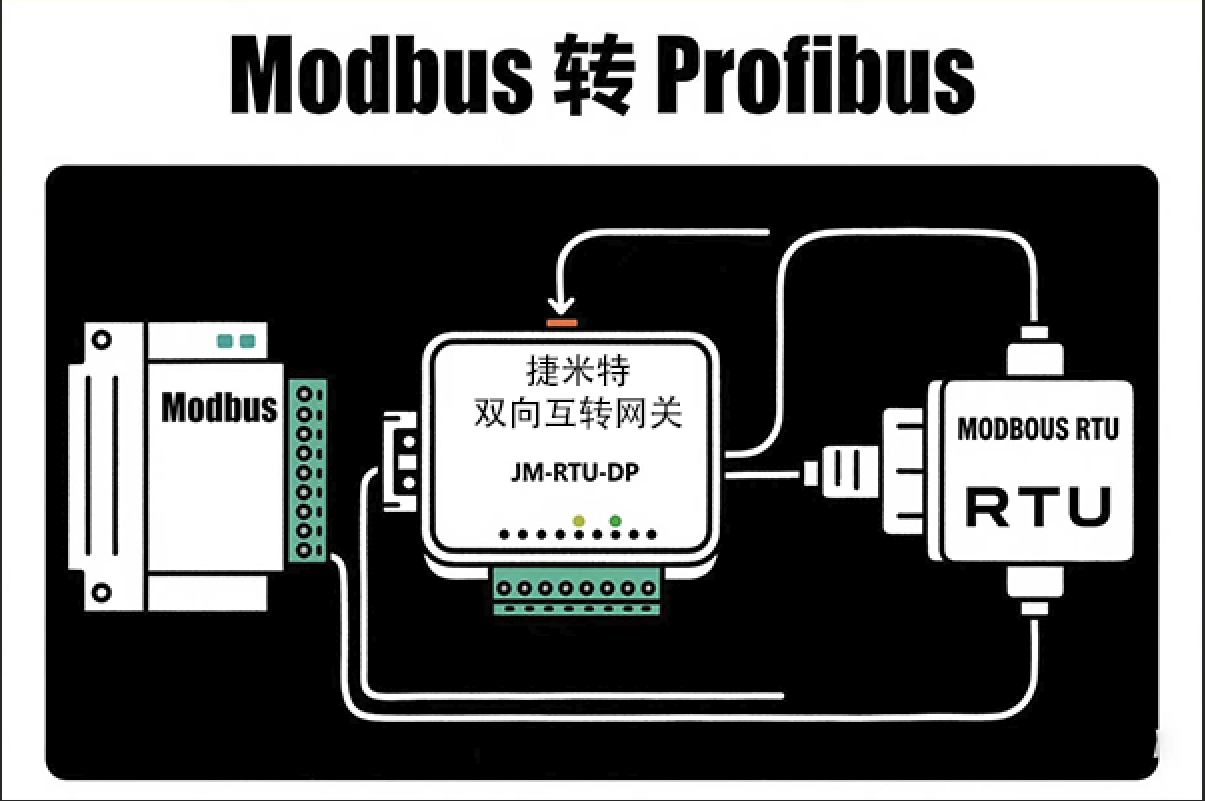

Modbus转Profibus-DP:快速上手协议转换模块的配置技巧

如何支持USB、DP、PCIe三种信号协议?

如何支持USB、DP、PCIe三种信号协议?

评论