上月初,英特尔携手日月光半导体(ASE)、AMD、Arm、谷歌云、Meta、微软、高通、三星和台积电等厂商发起UCIe产业联盟(通用芯粒高速互连),意欲推行开放的晶片间互连标准。可以说UCIe的出现,代表着全球半导体产业已经进入到成熟的产业阶段,但因为标准体系涉及到产业各环节间的协调和产业推广,UCIe真正被行业认可和开始实施预计还需要比较长的时间。

目前大陆已经有第一批企业率先加入了该组织,与UCIe产业联盟其他成员共同致力于UCIe 1.0版本规范和新一代UCIe技术标准的研究与应用,这是值得高兴的。但就是在该联盟热度持续不下的时候,我们也应该沉下心来思考这对技术研发与生态发展的影响。打铁还需自身硬,在联盟标准热度之下,除了加入标准获得话语权,芯片研发企业还应该冷静打磨自身,潜心研发攻克核心技术,为国内自主可控技术突破作出切实的贡献。

从产业角度来看,Chiplet目前主要以英特尔为代表等具有强大设计能力的公司可以做,UCIe产业联盟成员包括日月光、超威(AMD)、Google Cloud(谷歌)、脸书母公司Meta、微软、高通、三星和台积电等多家业者,包括半导体、封装、IP供应商、晶圆代工厂和云端服务提供厂商,基本可以形成一个小的产业生态闭环,这将进一步提高各产业环节的集中度,进一步巩固了龙头优势,是否会真正利好半导体产业的发展也是存疑的。

尤其需要注意到英特尔在美国半导体产业中扮演的敏感角色,在此特定背景下,我们不希望看到UCIe会成为政治化的工具。国内方面,我们要继续走好自己的路,加速国产化的同时,我们要做好应对一切冲击的准备。一方面,UCIe提供了一种可参考的产业平台机制,我们亦可以通过组建内部产业联盟的方式来优化产业分工,进一步加快国内产业发展,提高国内半导体产业对于冲击的耐受力。

就这一点,早在2020年国内举办的全球硬科技创新大会上,中国科学院院士/图灵奖得主姚期智、西安市副市长马鲜萍、芯动科技CEO敖海、紫光存储总裁任奇伟就共同启动了中国Chiplet产业联盟。并提出该联盟将致力于集聚人工智能、集成电路等领域产、学、研、金各类资源,搭建开放创新平台,缩短芯片设计周期、降低芯片设计成本,解决我国高质量发展进程中相关“卡脖子”技术难题。

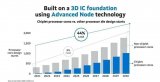

另一方面,我们可以尽早开发出标准化的自主Chiplet技术,为高性能CPU/GPU/NPU芯片的异构实现提供保障。就我所知,目前国内真正推出自主Chiplet技术的有芯动科技,我们来看看它推出的国内第一款自主Chiplet技术——Innolink™ Chiplet。据悉,Innolink™ Chiplet是第一款国产自主研发物理层兼容UCIe标准的IP解决方案。

据公开资料介绍,芯动在Chiplet技术领域积累了大量的客户应用需求经验,并且和台积电、intel、三星、美光等业界领军企业有密切的技术沟通和合作探索,在近几年各大巨头推行自己的Chiplet互联标准时,芯动科技也奋起直追紧随其后,两年前就开始了Innolink™ 的研发工作,率先明确Innolink B/C基于DDR的技术路线,并于2020年的Design Reuse全球会议上首次向业界公开Innolink A/B/C技术,率先推出自主研发的Innolink™ Chiplet标准并实现授权量产。

Innolink™ Chiplet具有自主知识产权,填补了国内的异构集成技术空白,打破了国外核心技术垄断,成功应用于国产GPU及其他高性能计算芯片,为国产高性能芯片的发展提供了一条新的道路。得益于正确的技术方向和超前的布局规划,Innolink™ 的物理层与UCIe的标准保持一致,成为国内首发、世界领先的自主UCIe Chiplet解决方案。

Innolink A/B/C实现方法

看到Innolink™ Chiplet实实在在的硬数据,我们确实惊讶于国内已在Chiplet领先技术领域实现了领先超越。尽管芯动科技在消费者领域并不为人熟知,但在很多B端企业中已颇具盛名,服务了数百家知名企业,拥有超过200次的流片记录、逾60亿颗授权量产芯片。Innolink™ Chiplet让我们看到了市场热度之下国内半导体耕耘者们默默无闻、脚踏实地的努力,也看到了国产半导体技术的更多未来。

总的来说,Chiplet发展需要整个半导体产业链的协同分工,从芯片设计、EDA工具、晶圆制造到封装测试,需要统一的标准和工艺升级,这需要时间探索和协作,不断地迭代前进。在当前的国际市场背景下,国产自主可控、可以持续迭代和发展的Chiplet技术显得尤为重要。芯动科技推出的自主Chiplet技术已成功运用于国产第一款高性能GPU“风华1号”,提升了产品性能和带宽,成为国产芯片里走在最前列的异构集成设计的实践者,期待更多本土企业和技术的突破,加快实现国产芯片自主可控。

审核编辑:符乾江

-

chiplet

+关注

关注

6文章

499浏览量

13650 -

UCIe

+关注

关注

0文章

53浏览量

2035

发布评论请先 登录

2026值得关注的存储技术

多Chiplet异构集成的先进互连技术

如何突破AI存储墙?深度解析ONFI 6.0高速接口与Chiplet解耦架构

西门子EDA如何推动Chiplet技术商业化落地

兆芯受邀出席中国电信信创产业联盟成立仪式

得一微电子受邀出席第四届HiPi Chiplet论坛

UCIe协议代际跃迁驱动开放芯粒生态构建

解构Chiplet,区分炒作与现实

CMOS 2.0与Chiplet两种创新技术的区别

新思科技UCIe IP解决方案实现片上网络互连

技术资讯 I 完整的 UCIe 信号完整性分析流程和异构集成合规性检查

锂电池热失控原理及安全检测技术解析

当我问DeepSeek国内芯片封测有哪些值得关注的企业,它这样回我

UCIe联盟热之下的思考,Chiplet技术本身更值得关注

UCIe联盟热之下的思考,Chiplet技术本身更值得关注

评论