二、输出(并-转-串)逻辑资源

7系列设备中的OSERDESE2是专用的 并-转-串 转换器,使用特定的时钟和逻辑资源设计来使得高速源同步接口实现变得容易。每个OSERDESE2模块都包含一个特定的串化器(serializer)用于数据和三态(3-state)控制。数据和3态(3-state)串化器都可以配置成SDR和DDR模式。数据串行化的位宽可以达到8:1(如果使用原语模块级联,则可以到10:1和14:1)。3态的串行化最高可达14:1,有一个专用的DDR3模式可用于支持高速内存应用程序。

The OSERDESE2 in 7 series devices is a dedicated parallel-to-serial converter with specific

clocking and logic resources designed to facilitate the implementation of high-speed

source-synchronous interfaces. Every OSERDESE2 module includes a dedicated serializer

for data and 3-state control. Both data and 3-state serializers can be configured in SDR and

DDR mode. Data serialization can be up to 8:1 (10:1 and 14:1 if using OSERDESE2 Width

Expansion). 3-state serialization can be up to 14:1. There is a dedicated DDR3 mode to

support high-speed memory applications.

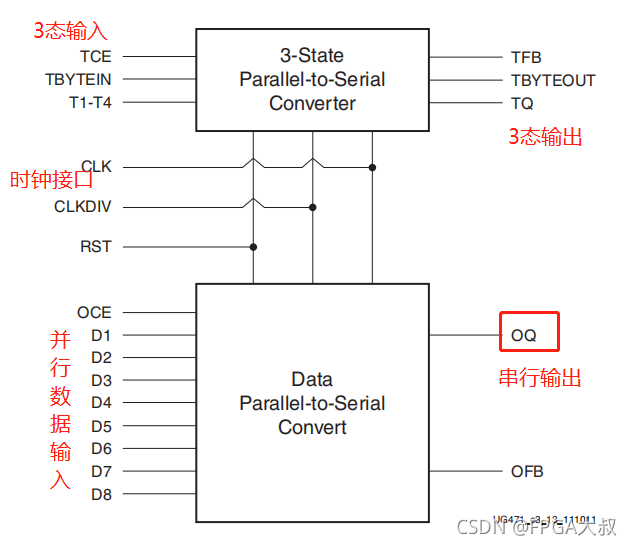

Figure 3-13 shows a block diagram of the OSERDESE2, highlighting all the major

components and features of the block.

下图是 OSERDESE2的模块图,显示了主要的组成部件和特性:

2.1数据(并-转-串)转换器

在一个OSERDESE2块中,数据(并-转-串)转换器接收2-8位的并行数据 (14位:使用OSERDESE2 位宽扩展),将数据串行化,然后通过OQ输出接口传递给IOB。并行数据串行化是从从最低位开始。也就是说:从D1管脚输入的数据最先传输到OQ输出管脚。数据并串转换器支持两种模式:SDR和DDR。

OSERDESE2数据比率转换使用两个时钟:CLK 和 CLKDIV。CLK是高度的串行时钟,CLKDIV是分频并行时钟。CLK和CLKDIV必须相位对齐。

在使用之前,必须对OSERDESE2进行复位操作。OSERDESE2包含一个内部计数器用来控制数据流。如果没有成功对复位同步(CLKDIV时钟域)释放,则会引起非预期的输出。

The data parallel-to-serial converter in one OSERDESE2 blocks receives two to eight bits of

parallel data from the fabric (14 bits if using OSERDESE2 Width Expansion), serializes the

data, and presents it to the IOB via the OQ outputs. Parallel data is serialized from lowest

order data input pin to highest (i.e., data on the D1 input pin is the first bit transmitted at

the OQ pins). The data parallel-to-serial converter is available in two modes: single-data

rate (SDR) and double-data rate (DDR).

The OSERDESE2 uses two clocks, CLK and CLKDIV, for data rate conversion. CLK is the

high-speed serial clock, CLKDIV is the divided parallel clock. CLK and CLKDIV must be

phase aligned. See OSERDESE2 Clocking Methods.

Prior to use, a reset must be applied to the OSERDESE2. The OSERDESE2 contains an

internal counter that controls dataflow. Failure to synchronize the reset deassertion with

the CLKDIV will produce an unexpected output

2.2 3-State Parallel-to-Serial Conversion

除了数据的并串转换之外,一个OSERDESE2模块还包含了一个3态并串转换器。与数据的并串转换不同,3态转换器串行化最高只能支持4位的并行3态信号。3态转换器不能进行级联。

In addition to parallel-to-serial conversion of data, an OSERDESE2 module also contains a

parallel-to-serial converter for 3-state control of the IOB. Unlike data conversion, the

3-state converter can only serialize up to four bits of parallel 3-state signals. The 3-state

converter cannot be cascaded.

三、OSERDESE2原语介绍

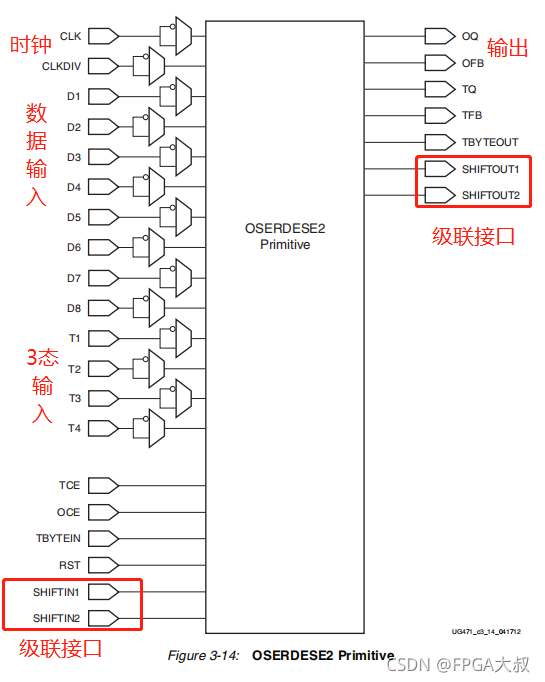

3.1 OSERDESE2框图

3.2 OSERDESE2例化

扫一眼,直接看3.3

OSERDESE2 #(

.DATA_RATE_OQ("DDR"), // DDR, SDR

.DATA_RATE_TQ("DDR"), // DDR, BUF, SDR

.DATA_WIDTH(4), // Parallel data width (2-8,10,14)

.INIT_OQ(1'b0), // Initial value of OQ output (1'b0,1'b1)

.INIT_TQ(1'b0), // Initial value of TQ output (1'b0,1'b1)

.SERDES_MODE("MASTER"), // MASTER, SLAVE

.SRVAL_OQ(1'b0), // OQ output value when SR is used (1'b0,1'b1)

.SRVAL_TQ(1'b0), // TQ output value when SR is used (1'b0,1'b1)

.TBYTE_CTL("FALSE"), // Enable tristate byte operation (FALSE, TRUE)

.TBYTE_SRC("FALSE"), // Tristate byte source (FALSE, TRUE)

.TRISTATE_WIDTH(4) // 3-state converter width (1,4)

)

OSERDESE2_inst (

.OFB(OFB), // 1-bit output: Feedback path for data

.OQ(OQ), // 1-bit output: Data path output

// SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each)

.SHIFTOUT1(SHIFTOUT1),

.SHIFTOUT2(SHIFTOUT2),

.TBYTEOUT(TBYTEOUT), // 1-bit output: Byte group tristate

.TFB(TFB), // 1-bit output: 3-state control

.TQ(TQ), // 1-bit output: 3-state control

.CLK(CLK), // 1-bit input: High speed clock

.CLKDIV(CLKDIV), // 1-bit input: Divided clock

// D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each)

.D1(D1),

.D2(D2),

.D3(D3),

.D4(D4),

.D5(D5),

.D6(D6),

.D7(D7),

.D8(D8),

.OCE(OCE), // 1-bit input: Output data clock enable

.RST(RST), // 1-bit input: Reset

// SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each)

.SHIFTIN1(SHIFTIN1),

.SHIFTIN2(SHIFTIN2),

// T1 - T4: 1-bit (each) input: Parallel 3-state inputs

.T1(T1),

.T2(T2),

.T3(T3),

.T4(T4),

.TBYTEIN(TBYTEIN), // 1-bit input: Byte group tristate

.TCE(TCE) // 1-bit input: 3-state clock enable

);

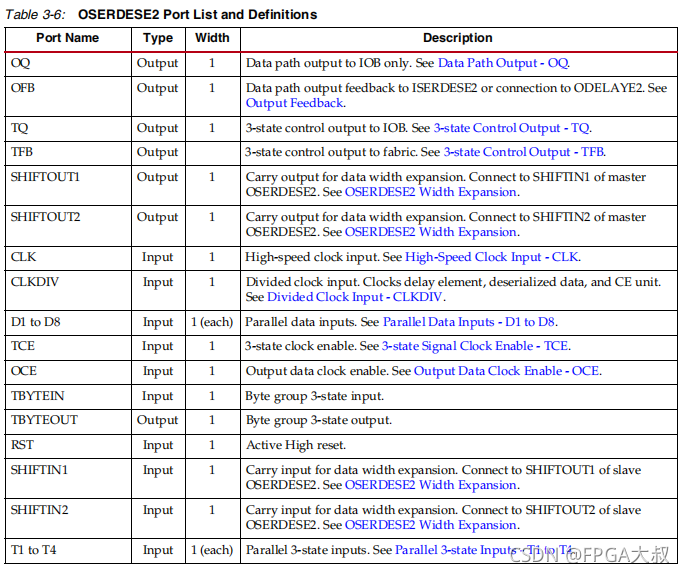

3.3 OSERDESE2端口

为了便于查看,后文对端口的进一步介绍一并写到表格。

下图为原文:

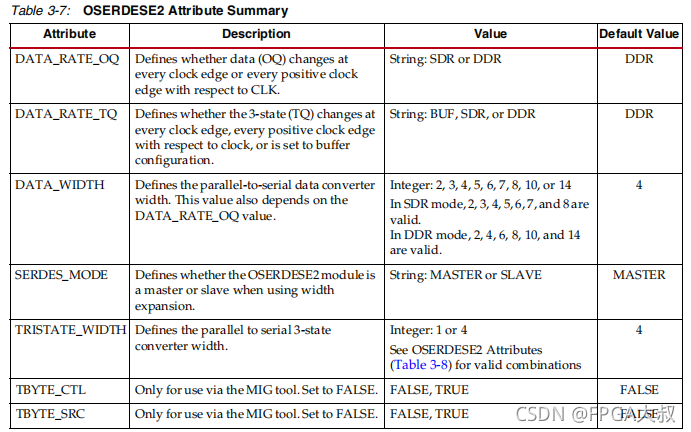

3.4 OSERDESE2属性

下图为原文:

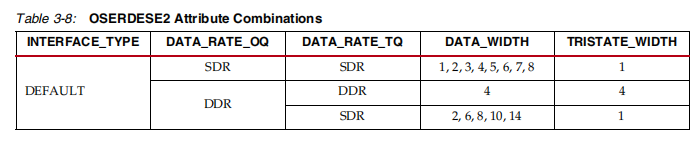

下图为OSERDESE2属性组合:

3.5 OSERDESE2时钟

在并转串过程中,CLK和 CLKDIV的相位关系是非常重要的。理想情况下,CLK和 CLKDIV是相位对齐的。在FPGA中有好几种时钟设置方式来帮助设计满足CLK和 CLKDIV的相位关系要求。对于OSERDESE2来说,只有一种是有效的:

- CLK由BUFIO驱动,CLKDIV由BUFR驱动

- CLK和CLKDIV由同一个MMCM或PLL驱动 (常用)

当使用一个MMCM来驱动OSERDESE2的CLK 和CLKDIV时,buffer类型不能混用。举个栗子:如果CLK由BUFG驱动,CLKDIV也必须由BUFG驱动。

The phase relationship of CLK and CLKDIV is important in the parallel-to-serial

conversion process. CLK and CLKDIV are (ideally) phase-aligned within a tolerance.

There are several clocking arrangements within the FPGA to help the design meet the

phase relationship requirements of CLK and CLKDIV. The only valid clocking

arrangements for the OSERDESE2 are:

• CLK driven by BUFIO, CLKDIV driven by BUFR

• CLK and CLKDIV driven by CLKOUT[0:6] of the same MMCM or PLL

When using a MMCM to drive the CLK and CLKDIV of the OSERDESE2 the buffer types

suppling the OSERDESE2 can not be mixed. For example, if CLK is driven by a BUFG,

CLKDIV must be driven by a BUFG as well.

3.6 OSERDESE2级联

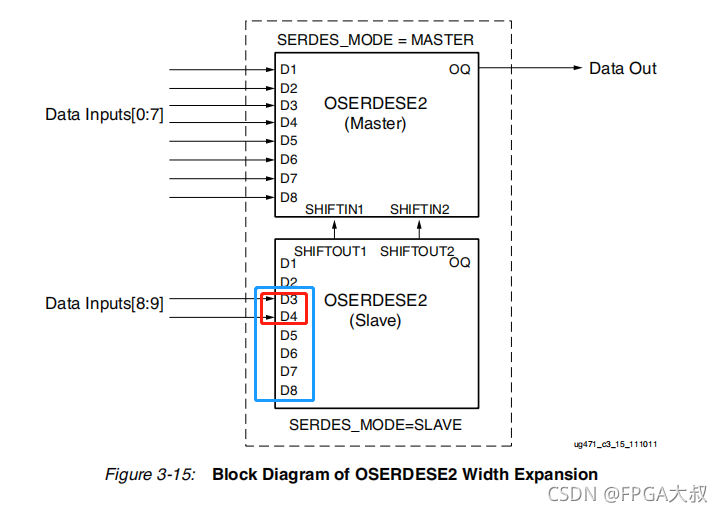

用两个OSERDESE2模块级联来构造一个超过8:1的并-串转换器。通过连接主OSERDESE2的SHIFTIN端口和从OSERDESE2的SHIFTOUT端口,转换器可以扩展为10:1和14:1(仅DDR模式)。(注:笔者感觉有点懵,曾在项目用主的SHIFTOUT端口接到从的SHIFTIN端口 = =||)。对于差分输出,连接_P管脚。当输出不是差分信号时,从OSERDESE2的输出buffer是不允许的,位宽扩展无法使用。

当使用补充的signal-ended标准时(也就是说DIFF_HSTL和DIFF_SSTL),位宽扩展可能不能使用。这是因为在I/O块的OLOGICE2/3块全部用作补充的signal-ended标准来传输这两个补充的信号,没有多余的OLOOGICE2/3资源可用来位宽扩展。

The OSERDESE2 modules be used to build a parallel-to-serial converter larger than 8:1. In

every I/O tile there are two OSERDESE2 modules; one master and one slave. By

connecting the SHIFTIN ports of the master OSERDESE2 to the SHIFTOUT ports of the

slave OSERDESE2, the parallel-to-serial converter can be expanded to up to 10:1 and 14:1

(DDR mode only). For a differential output, the master OSERDESE2 must be on the

positive (_P pin) side of the differential output pair. When the output is not differential, the

output buffer associated with the slave OSERDESE2 is not available and width expansion

cannot be used.

When using complementary single-ended standards (e.g., DIFF_HSTL and DIFF_SSTL),

width expansion might not be used. This is because both OLOGICE2/3 blocks in an I/O

tile are used by the complementary single-ended standards to transmit the two

complementary signals, leaving no OLOGICE2/3 blocks available for width expansion

purposes.

下图是10:1DDR模式并-串转换器,使用一主一从两个OSERDESE2模块。在这个例子中中从OSERDES端口D3-D4被用作并行数据接口的最后两位。

注:位宽扩展时,从OSERDESE2模块使用端口D3-D8; D1-D2不用。

3.7 OSERDESE2潜伏期

之前文章也介绍过:

Delay:延迟,延迟时间后才发生

Latency:潜伏,潜伏时间后信号才稳定

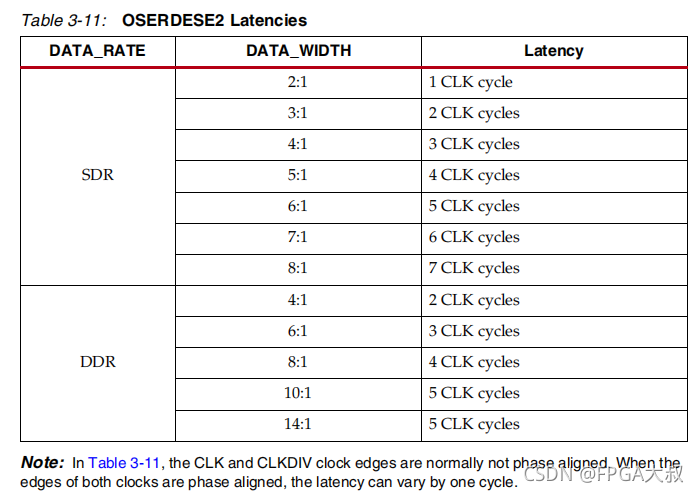

OSERDESE2块输入到输出的潜伏期由DATA_RATE和DATA_WIDTH属性决定。潜伏期被定义为事件a到事件b的一段时间:(a)当CLKDIV的上升沿,D1-D8的数据输入到OSERDESE2,(b)当串行数据流的第一位出现在OQ。简单解释下:就是输入到输出的时间。下图整理了不同OSERDESE2潜伏期的值。

The input to output latencies of OSERDESE2 blocks depend on the DATA_RATE and

DATA_WIDTH attributes. Latency is defined as a period of time between the following

two events: (a) when the rising edge of CLKDIV clocks the data at inputs D1–D8 into the

OSERDESE2, and (b) when the first bit of the serial stream appears at OQ. Table 3-11

summarizes the various OSERDESE2 latency values.

四、图解OSERDES串行化数据流

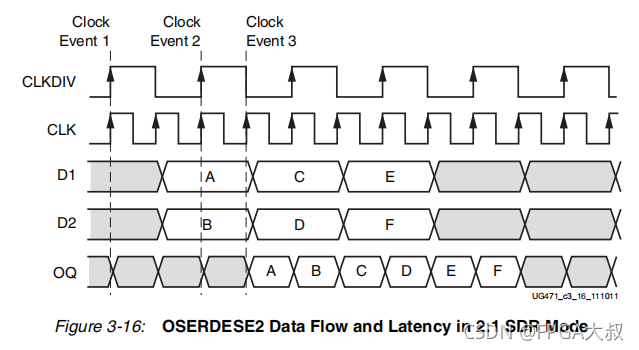

4.1 案例①SDR模式

2:1 SDR 数据串行化的时序图:

Clock Event 1:

在CLKDIV的上升沿,由FPGA逻辑驱动的字AB给到OSERDESE2的输入端D1和D2(经过一些传播延迟)

Clock Event 2 :

在CLKDIV的上升沿,由D1和D2输入的字AB被采样到OSERDES。

Clock Event 3

在AB被采样进入OSERDESE2后,数据A在OQ输出一个CLK时钟周期。这个潜伏期由3.7章节的表格查询可知。

4.2 案例②DDR模式

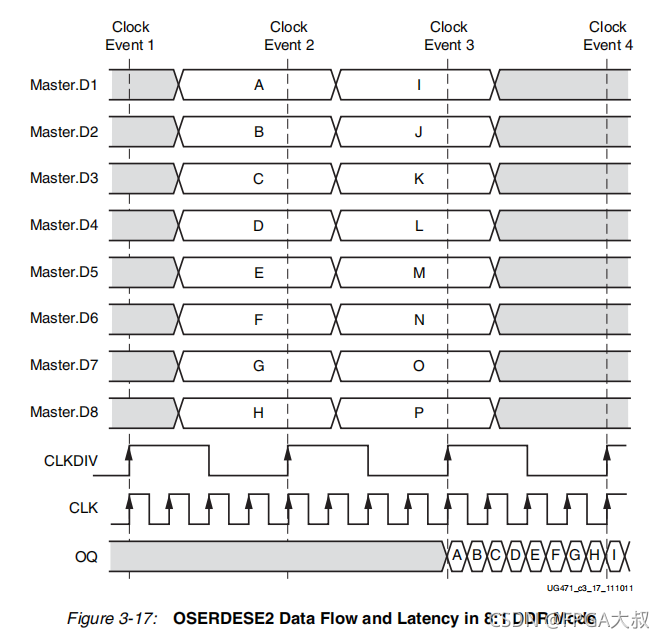

8:1 DDR数据串行化时序图:

Clock Event 1:

在CLKDIV的时钟上升沿,由FPGA逻辑驱动的字ABCDEFGH给到OSERDESE2的输入管脚D1-D8。

Clock Event 2:

在CLKDIV的时钟上升沿,D1-D8输入的ABCDEFGH被采样进OSERDESE2。

Clock Event 3:

在ABCDEFGH被采样进OSERDESE2后,数据位A首先在OQ输出4个CLK周期。这个潜伏期由3.7章节的表格查询可知。

D1-D8输入的第二个字 IJKLMNOP 被采样进入 OSERDESE2 。

Clock Event 4

在Clock Events 3和4之间, ABCDEFGH整个字被连续的传输到OQ,,一个完整的8位传输在一个CLKDIV周期内完成。

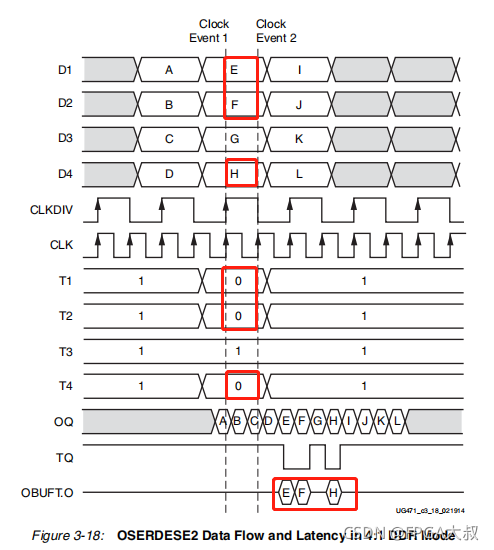

4.3 案例③3-state

The operation of a 3-state controller:

Clock Event 1

T1,T2,T4被驱动位低电平来释放3-态条件。OSERDESE2的T1-T4和D1-D4串行化路径是完全相同的(包括潜伏期),所以EFGH和0010在Clock Event 1是始终对齐的。

Clock Event 2

在EFGH被采样进入OSERDESE2后,数据位E出现在OQ一个CLK周期,潜伏期可看3.7。

在0010被采样进入OSERDESE2 3态块后,三态输入的0在TQ输出一个CLK周期,潜伏期可看3.7。

看图得知:OBUFT的输出端O输出EFH,对应三态输入0释放掉三态条件时候的D1-D4输入,并且输出在TQ为低时有效。(这是笔者根据上图猜测的结论,实际上笔者还没使用过 = =)

五、后记

最后的I/O FIFO先略过。

加上前两篇,《UG471-SelectIO》(1-3) 基本翻译完成。

算是小小的成就,给自己打Call~

如有错误,欢迎拍砖~

但是,本系列UG471文章还停留在翻译介绍阶段,下一步我会将其整理到LVDS接口的使用中进行介绍。未完待续。

审核编辑:符乾江

-

FPGA

+关注

关注

1664文章

22502浏览量

639210 -

Xilinx

+关注

关注

73文章

2206浏览量

131894

发布评论请先 登录

安森美NVTFS5C471NL单通道N沟道功率MOSFET深度解析

Xilinx FPGA输入延迟原语介绍

RDMA设计46:RoCE v2原语功能:单边语义

Xilinx FPGA中IDELAYCTRL参考时钟控制模块的使用

RDMA设计45:RoCE v2 原语功能验证与分析2

探索OP471:高性能四通道运算放大器的卓越之选

DLP471TP 0.47 4K 超高清 DMD 的技术解析与设计要点

DLP471NE 0.47 英寸全高清数字微镜器件:技术解析与应用指南

Xilinx FPGA串行通信协议介绍

贴片压敏电阻SMD3225K471的全面解析

《Xilinx—UG471中文翻译》(3)OSERDESE2原语介绍

《Xilinx—UG471中文翻译》(3)OSERDESE2原语介绍

评论