未来已来,只是尚未流行。

EDA,三个简单字母却代表着解决芯片设计重重障碍的底层技术,一端连接着创新严谨的芯片开发者,另一端则连接着日新月异的数字世界。

当我们在谈论EDA时,我们在谈论什么

在EDA出现之前,开发者必须手工完成集成电路的设计、布线等工作,而后工业界开始使用几何学方法来制造用于电路光绘的胶带。从20世纪60年代中期开始,业界先后出现包括通过几何软件生成单色曝光图像图形化工具,第一个自动化的电路布局和布线工具,这些工具奏响了EDA发展的序曲。1970年代中期起,开发人员尝试将整个设计过程自动化,而不仅仅满足于自动完成掩膜草图。而从80年代开始,随着VHDL、Verilog、以及仿真器的出现,芯片设计仿真和可执行的设计有了其规范化的硬件描述语言和标准。

1986年,Aart de Geus博士发明了自己的逻辑综合技术,以取代手动化设计过程。利用这种新工具,可以在几分钟或几小时内完成以前需要数周才能完成的设计工作,而且成果更佳,这“彻底改变了数字设计的概念”。

EDA工具让芯片功能开发与具体物理实现逐渐剥离开,芯片架构师与数字电路设计工程师不再需要关注晶体管在物理实现时的很多细节。单元库、硬件描述语言和硅IP的出现,让工程师可以用抽象化的高级语言设计芯片,通过逻辑综合工具把抽象化设计转换成实际的逻辑电路连接组合。这直接加速了芯片开发的进程,使大规模芯片开发变为可能,让人类有机会设计出包含数百亿个晶体管的复杂芯片。

逻辑综合:划时代的EDA工具

逻辑综合对于EDA设计领域来说是一个伟大的成就,能够把描述RTL级的HDL语言翻译成GTECH,然后再优化和映射成工艺相关的门级网表,作为输入给自动布局布线工具生成GDSII文件用于芯片制造。例如,1986年推出的逻辑综合工具Design Compiler,得到全球几乎所有的芯片供应商、IP供应商和库供应商的支持和应用,到九十年代中期,Design Compiler已经成为RTL逻辑综合的事实标准,让开发者的生产力提高至10倍。

Design Compiler作为业界历史最悠久的设计实现工具,经过30年的不断发展和技术积累,该逻辑综合工具提供最可靠设计实现优化和性能结果,是目前业界使用最为广泛的ASIC设计实现工具,为当今极度复杂的前沿设计提供了有力支持,能够满足了诸如人工智能(AI)、云计算、5G和自动驾驶等半导体市场对更小体积、更高性能、更低功耗的芯片需求,以及对研发周期越来越高的要求。

EDA公司并未止步于一时的技术领先,而是前瞻性地预判到行业未来的发展趋势和市场需求,持续对逻辑综合工具进行研发投资,带来一次次突破性的创新综合技术。例如加入物理综合,即在综合前加入版图的布局规划信息,然后调用库信息和约束条件,生成带有布局信息的门级设计结果,进一步提高了综合与布局布线结果的相关一致性,不仅可以更精准地估算连线延时,还可以预测布线拥堵情况并进行相应优化。

摩尔定律放缓,EDA的“破局之道”

随着摩尔定律放缓,半导体产业开始采用新架构,硬件层面出现一些根本的变化。单个巨大芯片的设计方法开始由多个芯片取代,其中每个芯片都有特定的作用,并使用非常密集的全新集成技术封装到一起。

在这个半导体设计的新时代,摩尔定律推动规模复杂性不断提高,而且各种技术全面融合在单个包装内提高了系统复杂性。Aart de Geus博士将半导体增长的这个新阶段定义为SysMoore时代。SysMoore融合了摩尔定律的持续优势和系统性集成的新优势。面对新时代的复杂挑战,EDA工具从硅片层面、器件层面、芯片层面、系统层面、软件层面都开展关键创新,旨在实现更高的设计效率,提供更有竞争力的产品。

当下, EDA工具进入2.0时代,其未来的发展着重在两个大的方向,一是应用目前丰富的算力,提高并行和分布式处理能力,提升设计效率;二是更多的应用AI技术,促进设计的探索自动化,减少可替代的人工努力,解放工程师资源到更具创造性的工作。

“易用”与“强大”的拉锯战

数字时代,瞬息万变。人工智能、汽车电子、5G等全新技术与应用对高质量芯片需求激增,不断推动集成电路产业的创新与壮大。同时,汽车、超大规模数据中心等领域的大型系统级公司正纷纷将芯片研发纳入公司整体业务和差异化战略,试图在时代的浪潮中分得一杯羹。

芯片应用范围随之不断扩展,不同设计需求将长期共存。对此,新思科技全球资深副总裁葛群兼中国董事长提出,要为开发者提供像“美图秀秀”和“Photoshop”一样不同类型的集成电路设计工具,以满足更多元化的工程需求。家电等终端产品所使用的芯片功能简单,性能要求也不高,相对简单的“美图秀秀”便可满足其设计需求;而像CPU、GPU等追求极致功能SoC,集成度要求则越来越高,需要最先进的工艺,则需要更为专业的“Photoshop”。

同时,由于数字社会中芯片的需求量激增,未来使用“美图秀秀”类EDA工具进行芯片设计的场景会更多,市场潜力也会更大。因此,使芯片设计变得像用“美图秀秀”做图一样简单,而不是维持在原来只有少数人才能掌握的专业“Photoshop”是半导体技术发展的前景,亦是新思一直以来的期待。

未来不是一场零和博弈

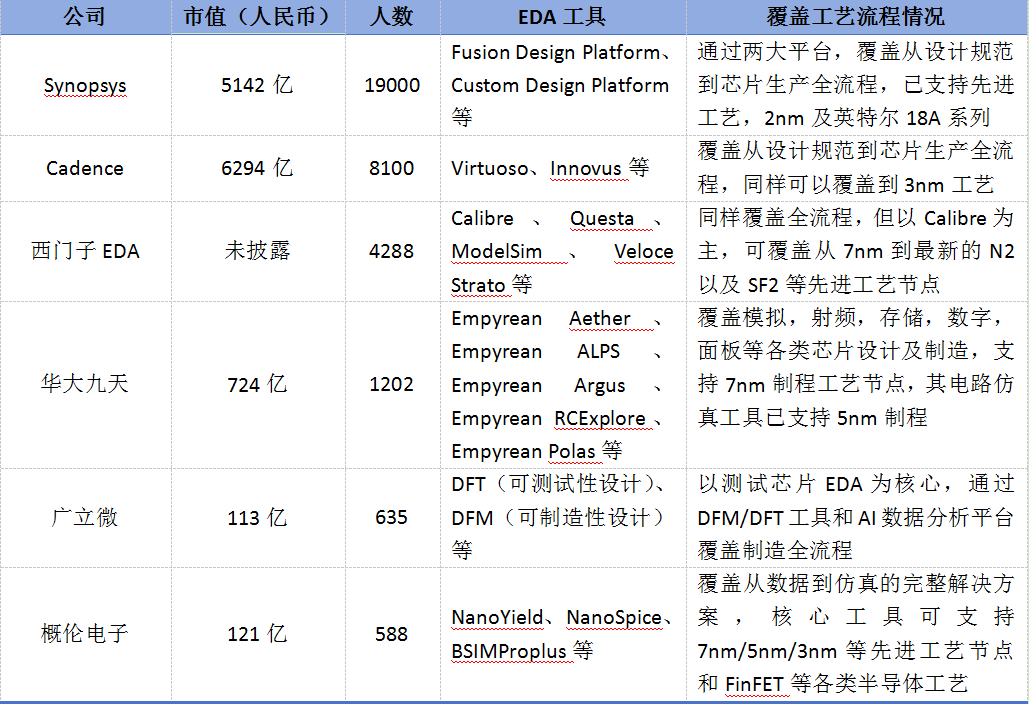

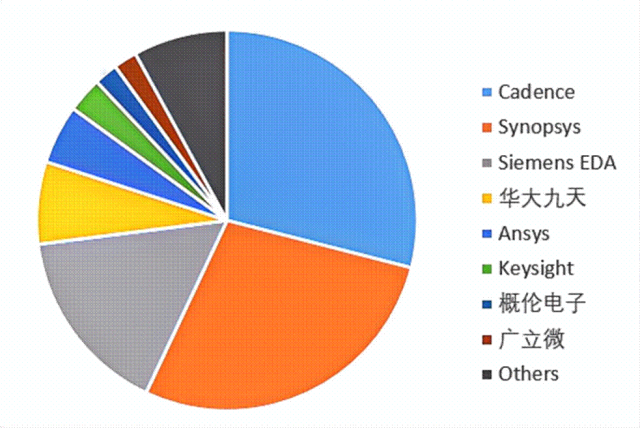

一般一款芯片的设计周期是一至两年,而一个EDA点工具的开发周期就需要3年,平台型工具更至少需要5年的开发时间。国际领先EDA公司的发展历程无不例外,都是从点工具入场,通过长期研发投入和不断并购,历时30多年新思才构建起了如今阵列完整的EDA工具库。这对于我们中国EDA的本土化发展颇具借鉴意义——先从单个点工具切入,再循序渐进到整个套件和平台。这不可能一蹴而就,必然是一个渐进的过程。

在当前国内国际双循环相互促进的新发展格局下,国际领先EDA公司在多数场景中都将是本土EDA厂商的合作伙伴,而非竞争对手。在本土公司尚不能构建起完整芯片开发环境前,本土供应链更可行的方式是与国际化头部企业加强合作,利用新兴的人工智能和云计算的技术,结合当前EDA头部企业的优势产品,发挥本土公司特色,为中国芯片行业发展铺平道路。

作为数字经济的“底座科技”,EDA从最初作为输入与仿真的工具确保芯片的正确设计、到通过优化与映射确保芯片设计的最佳性能、再到如今不断提升自主化和智能化来引领芯片设计,正通过自身的不断演进和迭代升级,为数字经济时代提供源源不断的动力。

原文标题:当我们在谈论数字经济,我们在谈论EDA

文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

-

芯片

+关注

关注

463文章

54475浏览量

469798 -

仿真器

+关注

关注

14文章

1053浏览量

88218 -

eda

+关注

关注

72文章

3148浏览量

183870

原文标题:当我们在谈论数字经济,我们在谈论EDA

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】跟着本书来看EDA的奥秘和EDA发展

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】--中国EDA的发展

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】+ 芯片“卡脖子”引发对EDA的重视

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】+ 全书概览

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】--EDA了解与发展概况

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】--全书概览

【书籍评测活动NO.69】解码中国”芯“基石,洞见EDA突围路《芯片设计基石——EDA产业全景与未来展望》

EDA行业的AI智能体来了!正重构芯片设计

西门子EDA AI System驱动芯片设计新纪元

华大九天物理验证EDA工具Empyrean Argus助力芯片设计

EDA工具进行芯片设计的场景有哪些

EDA工具进行芯片设计的场景有哪些

评论