接上一篇。。。。。。

5.

GDDR6技术细节以及Clamshell模式

GDDR6它是采用16n Prefetch结构,一次写操作或者读操作的数据是16n。每个GDDR6颗粒有两个独立的通道,每个独立的通道访问独立的内存空间。对于每个通道,读或者写的位宽是256bit或者32Byte。P-to-S converter是一个并变串的转换器,把每个256bit位宽的数据转换成16位总线,每位总线上传输16bit的数据。这样GDDR6每个通道最小的访问粒度是256bit或者32Byte。

根据GDDR6这样16n 预取结构,内部存储阵列如果访问周期是1ns,则I/O上的数据率则是16Gbps。

一个GDDR6控制器支持两个独立通道,一个GDDR6颗粒也是两个独立的通道,所以在通常模式下,一个GDDR6控制器对应一个GDDR6的颗粒,用x16模式,实现最高512Gb/s的带宽。

因为目前市面上GDDR6颗粒的最大容量是16Gb,在有些应用中如果对容量有一定的要求,可以使用一种叫Clamshell的连接方式,如图7[5]所示,每个GDDR6控制器连接两个GDDR6颗粒,每个GDDR6的颗粒用x8模式,这样在这种Clamshell模式下,带宽不变,但是支持的GDDR6的容量翻倍了。

6.

GDDR6在7t1500上的读写效率

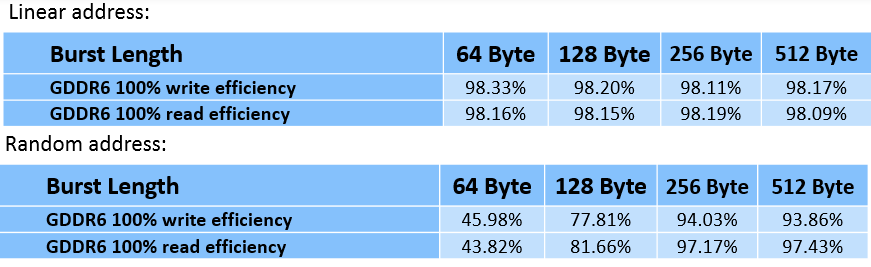

最后,我们测试一下7t1500上GDDR6控制器的读写效率,所有的测试结果基于仿真数据。因为7t1500包含了片上网络(NoC),并且NoC已经实现了仲裁,时钟域转换的逻辑,我们用三个用户逻辑通过NoC去访问同一个GDDR6 Channel,得到的综合读写效率更能反映用户实际运用中的场景。

在不同的突发长度和不同的地址访问方式下的测试结果如图所示。

图9 GDDR6读写效率

后面我们会继续深入了解Speedster 7t FPGA芯片上的一些特性,以及这些特性如何运用在数据加速和网络加速中,敬请期待。如需更多信息或者有任何疑问您可以通过Achronix公众号里的联系方式联系我们,也可访问Achronix公司官方网站http://www.achronix.com

如果需要进一步联络Achronix中国区技术和产品应用团队,请发送邮件到:dawson.guo@achronix.com。

编辑:jq

-

数据

+关注

关注

8文章

7350浏览量

95063 -

仿真

+关注

关注

55文章

4541浏览量

138707 -

FPGA芯片

+关注

关注

4文章

250浏览量

41130

原文标题:GDDR6给FPGA带来的大带宽存储优势以及性能测试(下)

文章出处:【微信号:Achronix,微信公众号:Achronix】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相变存储器 (PCM) 技术介绍

探索Arria V系列FPGA:高性能与低功耗的完美结合

AMD 推出第二代 Kintex UltraScale+ 中端FPGA,助力智能高性能系统

高性能网络存储设计:NVMe-oF IP的实现探讨

HBM量价齐飞,UFS加速普及:存储狂飙下的“最后质检”攻坚战

昆仑芯R200 AI加速卡技术规格解析

如何利用Verilog HDL在FPGA上实现SRAM的读写测试

FPGA测试DDR带宽跑不满的常见原因及分析方法

【上海晶珩睿莓1开发板试用体验】5、网络性能测试

AI狂飙, FPGA会掉队吗? (下)

探究GDDR6给FPGA带来的大带宽存储优势以及性能测试(下)

探究GDDR6给FPGA带来的大带宽存储优势以及性能测试(下)

评论