答:第一步,双击需要匹配的元器件,编辑改元器件的属性;

第二步,在弹出的元器件的属性中,点击Pivot菜单,可以对属性框进行横向的或者是竖向的显示;

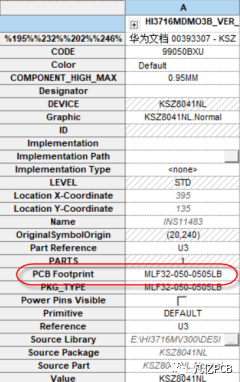

第三步,找到PCB Footprint那一栏,填入该元器件需要匹配的PCB封装名称,即可完成对改器件的PCB封装匹配,如图3-46所示;

图3-46元器件单个PCB封装匹配示意图

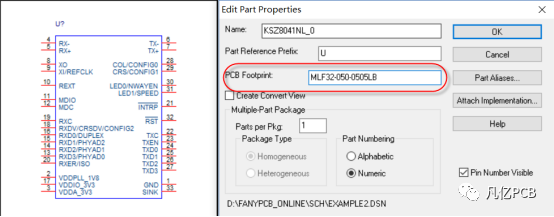

第四步,对于IC类的器件,由于它的封装是固定的,我们再创建原理图库封装的时候,就把该元器件PCB封装名称填上,这样后期就不用再匹配PCB封装了, 如图3-47所示。

图3-47元器件封装库封装名称匹配示意图

编辑:jq

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pcb

+关注

关注

4418文章

23979浏览量

426458 -

元器件

+关注

关注

113文章

5055浏览量

100463 -

IC

+关注

关注

36文章

6485浏览量

186462 -

封装

+关注

关注

128文章

9341浏览量

149090

原文标题:【知识分享】26. orcad中单个器件的PCB封装应该怎么处理呢?

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

stm32cubeide 编译报错如何处理?

报错如何处理

\"make -j8 all\" terminated with exit code -1073741819. Build might be incomplete.

发表于 04-28 07:47

S32G399A将PL_03引脚用作EIRQ中断时,应如何配置器件树?如何处理中断?

您好,我正在使用S32G399A芯片。当我将PL_03引脚用作EIRQ中断时,应如何配置器件树?如何处理中断。

S32G3

发表于 04-16 06:59

PCB设计与工艺规范 PCB Layout工程师一次讲透

设计和后期处理三部分。 一、前期准备 1、明确设计的目标,对选用的器件类型进行甄选,对整体方案进行确认,拿出书面设计方案来; 2、准备器件的原理图封装库和

大语言模型如何处理上下文窗口中的输入

本博客介绍了五个基本概念,阐述了大语言模型如何处理上下文窗口中的输入。通过明确的例子和实践中获得的见解,本文介绍了多个与上下文窗口有关的基本概念,如词元化、序列长度和注意力等。

Stduio使用wifi模块出错如何处理?

外设为潘多拉IOT开发板,使用Stduio配置了wifi框架,但是代码里在配置wifi模式时,没有找到wlan0这个设备,wifi整个功能也用不了,请问应该如何处理。使用正点原子资料包里的rtthread测试demo,wifi工作正常,wifi模块硬件没有问题。

发表于 10-10 08:18

在rt-thread studio环境中之前编译成功的项目(1234)重命名(test)后出现大批量的错误是什么原因造成?如何处理?

在rt-thread studio环境中之前编译成功的项目(1234)重命名(test)后出现大批量的错误是什么原因造成?该如何处理?这很困扰,为啥重命名就能出现这样的情况?

发表于 09-17 06:58

静力水准仪在测量过程中遇到误差如何处理?

静力水准仪在测量过程中遇到误差如何处理?静力水准仪在工程沉降监测中出现数据偏差时,需采取系统性处理措施。根据实际工况,误差主要源于环境干扰、设备状态、安装缺陷及操作不当四类因素,需针对性解决。静力

固定式测斜仪在测量过程中遇到误差如何处理?

在岩土工程与结构物安全监测中,固定式测斜仪是捕捉位移变化的核心设备。然而,实际应用中可能因环境、操作或设备因素导致测量误差。很多人想要了解固定式测斜仪在测量过程中遇到误差如何处理?下面

Cadence SPB OrCAD Allegro24.1安装包

包括电路设计、仿真分析、PCB布线以及封装技术等多种应用,Cadence 已于2024年9月份发布了最新的Cadence SPB OrCAD X and Allegro X v24.10版本,带来了若干的新特性,涵盖了

发表于 05-22 16:45

•49次下载

orcad中单个器件的PCB封装如何处理

orcad中单个器件的PCB封装如何处理

评论