使晶体管工作会产生电气负载和热负载。对晶体管来讲,负载太大寿命会缩短,最坏的情况下会导致晶体管被破坏。

为防止这种情况,需要检查实际使用状态,并确认在使用上是否有问题。这里说明一下具体的判定方法。为安全使用晶体管,请务必作为参考。

判定前:晶体管的选定~贴装的流程

1. 晶体管的选定

从Web、Shortform产品目录上选定满足规格要求的晶体管。

晶体管产品页

2. 规格∙样品的获取

部分样品可从网上申请。

3. 向实际电路(评估电路)上贴装晶体管

请确认

选定的晶体管是否在实际电路上安全工作?

在工作的情况下,是否长期(可靠)稳定地工作?

等等,还需要考虑电气裕量。

晶体管可否使用的判定方法

可否使用的判定按照以下流程进行。

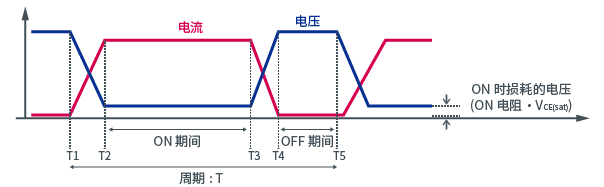

1. 测定实际的电流、电压波形

确认电流、电压

用示波器确认晶体管上的电压、电流。

需要全部满足规格书上记载的额定值,特别应该确认下列项目。

特别应该确认的项目

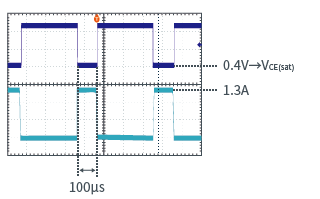

例:开关双极晶体管2SD2673时的波形(100µs/div)

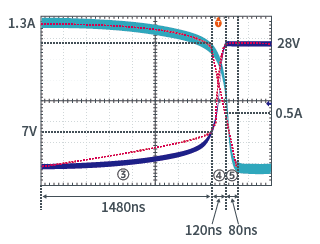

由于随后要计算开关时的功率损耗,所以要确认OFF→ON时和ON→OFF时的扩大波形。

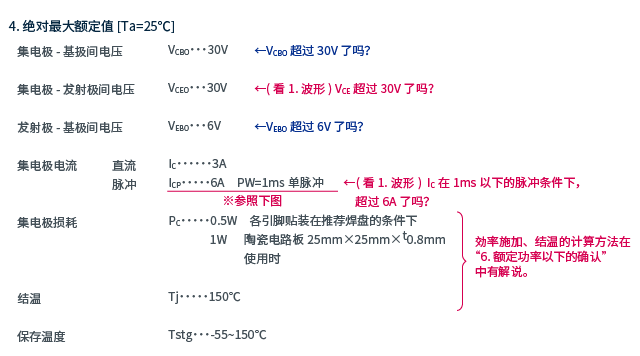

2. 是否一直满足绝对最大额定值?

确认绝对最大额定值

确认"1. 确认电流、电压"中确认的电流、电压是否超过了规格书中记载的绝对最大额定值。

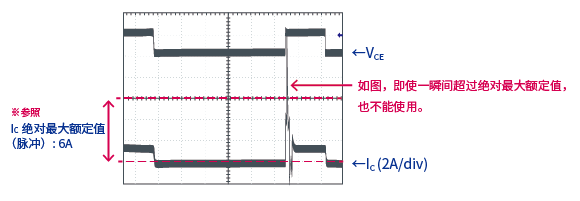

例1. 中未确认的项目,全部都需要在绝对最大额定值以下。即使浪涌电流和浪涌电压只在一瞬间超过了绝对最大额定值也不可使用。如果超过绝对最大额定值有可能造成破坏和劣化。

例 : 2SD2673的规格书(记载了绝对最大额定值)

例:瞬间超过绝对最大额定值的例子(不可使用)

3. 是否在SOA范围内?

确认安全工作区域 (SOA*1) 1

安全工作区域(SOA)表示晶体管可安全工作的区域。

不过,SOA只是关于1脉冲的数据,在脉冲反复混入时,需要所有脉冲都进入SOA范围内,并且通过 "4. 确认安全工作区域(SOA)2" 计算的平均施加功率在额定功率以下。

*1SOA・・・安全工作区域 (Safety Operating Area) 的简称。有时也称ASO (Area of Safe Operating)。

SOA确认方法

确认"1. 确认电流、电压"中确认的波形是否在安全工作区域 (SOA) 的范围内。即使浪涌电流和浪涌电压只在一瞬间超过了绝对最大额定值也不可使用。

另外,请注意,即使在"2. 确认绝对最大额定值"中确认的绝对最大额定值的范围内,有时也会超出SOA的范围。(参照下例)

例:2SD2673 ・安全工作区域

此波形在严格意义上电流并非方形波,但考虑到余量,

IC=5.8A, VCE=10V, Pw=1ms视为方形波。

虽然处于绝对最大额定值以下,

但因为超过了安全工作区域,所以不可使用。

4. 在使用环境温度*1下是否在下降的SOA范围内?

*1按照使用环境温度或因晶体管发热温度上升时的元件温度来考虑。

确认安全工作区域 (SOA) 2

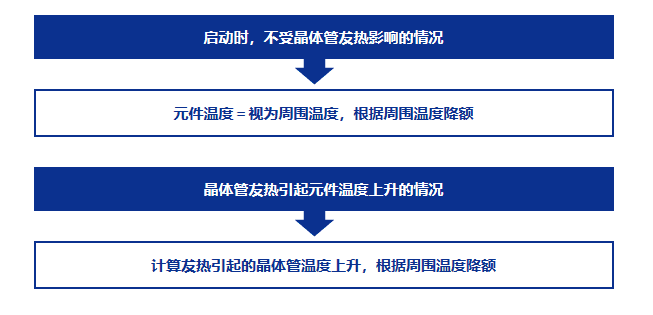

由于通常的安全工作区域 (SOA) 是在常温 (25ºC) 下的数据,所以周围温度在25ºC以上时,或者因晶体管自身发热元件温度上升时,需要降低SOA的温度。

SOA的温度降低方法

双极晶体管篇 MOSFET篇

※降低的温度基本是元件的温度。

关于元件温度的详细计算方法,请参照 "元件温度的计算方法" 。

附属 SOA(安全工作区域)的温度降低方法

1. SOA(安全工作区域)

周围温度在25ºC以上时,或者因晶体管自身发热元件温度上升时,需要降低温度。前者降低周围温度,后者降低元件温度。具体方法就是将SOA线平行移向低电流方向。如图1所示,下降率根据区域不同而不同。

1-1. 热限制区域

在该区域,SOA线具有45º 的倾斜度(功率固定线)。

在该区域,下降率是0.8%/ºC。

1-2. 2次下降区域

晶体管存在热失控引起的2次下降区域。

在2次下降区域,SOA线具有45º 以上的倾斜度。

在该区域,下降率是0.5%/ºC。

图1: SOA的温度降额

例 Ta=100°C

2-1. 热限制区域的降额

例如,周围温度100ºC时,降额如下。

降额=⊿t×(降额率)

=(100°C-25°C) × 0.8% / °C

=60%

因此,该区域的SOA线向低电流方向平行移动60%。

2-2. 2次下降区域的降额

同理,2次下降区域的降额如下。

降额=⊿t×(降额率)

=(100°C-25°C) × 0.5% / °C

=37.5%

因此,该区域的SOA线向低电流方向平行移动37.5%。

图2: SOA的温度降额

5. 连续脉冲?单脉冲?

功率・发热确认

单脉冲

如同上电和掉电时的浪涌电流一样,只发生一次脉冲的情形(无反复脉冲时)称为单脉冲,

此时,

确认处于SOA范围时

可以使用→ 请使用

连续脉冲

将脉冲反复发生的情形称为连续脉冲,此时,

周围温度条件下,处于额定功率以下吗?

需要确认确认额定功率以下

6. 平均功耗是否在周围温度的额定功率以下?

额定功率以下的确认

周围温度的额定功率以下=元件温度在绝对最大额定值150ºC以下。使元件温度升到150ºC的功率定为额定功率。

详细内容请参照"元件温度的计算方法"。

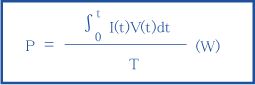

功率计算方法

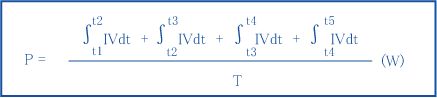

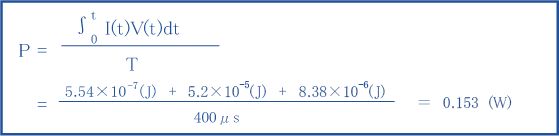

基本上,平均功率是以时间对电流和电压的积进行积分的值除以时间所得的值。

这种情况下,将1周期分为4个区间计算。

实际的积分计算采用积分公式。

下面,对"1.确认电流、电压"确认的波形的例子进行实际计算。

(1) OFF→ON时

根据积分公式,①的区间

∫ IVdt =(1/6)×100ns×(2・0A・5V+0A・2V+1.3A・5V+2・1.3A・2V)

=1.95×10-7(J)

②的区间

∫ IVdt =(1/6)×230ns×(2・1.3A・2V+1.3A・0.4V+1.3A・2V+2・1.3A・0.4V)

=3.59 × 10-7(J)

OFF→ON时

合计: 5.54×10-7(J)

(2) ON期间中

∫IVdt=100µs×0.4V×1.3A

=5.2×10-5(J)

(3) ON→OFF时

③的区间

∫IVdt =(1/6)×1480ns×(2・1.3A・0V+1.3A・7V+1.15A・0V+2・1.15A・7V)

=6.22×10-6(J)

④的区间

∫IVdt =(1/6)×120ns×(2・1.15A・7V+1.15A・28V+0.5A・7V+2・0.5A・28V)

=1.6×10-6(J)

⑤的区间

∫IVdt =(1/6)×80ns×(2・0.5A・28V+0.5A・28V+0A・28V+2・0A・28V)

=0.56×10-6(J)

OFF→ON时

合计: 8.38×10-6(J)

(4) OFF时,认为电流几乎为零(实际上有数nA~数10nA的漏电流),并认为OFF期间的功耗为零。

合计以上各区间计算的积分值,除以1周期的长度400µs,为平均功耗,即

而且,这里对双极晶体管2SD2673例子的集电极电流IC和集电极-发射极间电压VCE进行积分计算。如果对数字晶体管的输出电流IO和输出电压VO,MOSFET的漏极电流Id和漏极-源极间电压VDS进行同样的积分计算,即可算出平均功耗。

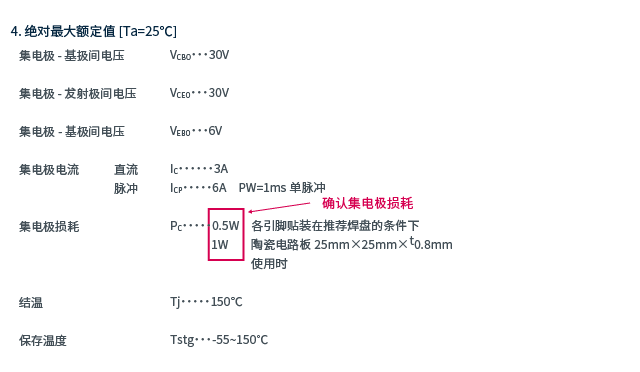

通过求得平均功耗,确认规格书的集电极损耗(MOSFET是漏极损耗)。

例:2SD2673的规格书

在这种情况下,平均施加功率是0.153W,集电极容许损耗是0.5W(推荐接地层:玻璃环氧树脂电路板贴装时),所以在周围温度25ºC时可以使用。(准确地说,集电极容许损耗根据贴装电路板和land面积等决定的散热条件而不同,但以推荐接地层贴装时的值为基准)

周围温度25ºC以上时,确认功率降低曲线并进行温度降低。

元件温度的详细计算方法请参照"元件温度的计算方法"。

责任编辑:haq

-

电路

+关注

关注

173文章

6064浏览量

177547 -

晶体管

+关注

关注

78文章

10286浏览量

146494

原文标题:安全使用晶体管的选定方法

文章出处:【微信号:大联大,微信公众号:大联大】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

MUN5136数字晶体管技术解析与应用指南

电压选择晶体管应用电路第二期

0.45-6.0 GHz 低噪声晶体管 skyworksinc

多值电场型电压选择晶体管结构

晶体管光耦的工作原理

下一代高速芯片晶体管解制造问题解决了!

无结场效应晶体管详解

如何才能安全使用晶体管

如何才能安全使用晶体管

评论