74LS193芯片是同步四位二进制可逆计数器,它具有双时钟输入,并具有异步清零和异步置数等功能。

74ls193计数器工作原理:

193为可预置的十进制同步加/减计数器,共有54193/74193,54LS193/74LS193两种线路结构形式。其主要电特性的典型值如下:

193的清除端是异步的。当清除端(CLEAR)为高电平时,不管时钟端(CDOWN、CUP)状态如何,即可完成清除功能。

193的预置是异步的。当置入控制端(LOAD)为低电平时,不管时钟(CDOWN、CUP)的状态如何,输出端(QA-QD)即可预置成与数据输入端(A-D)相一致的状态。

193的计数是同步的,靠CDOWN、CUP同时加在4个触发器上而实现。在CDOWN、CUP上升沿作用下QA-QD同时变化,从而消除了异步计数器中出现的计数尖峰。当进行加计数或减计数时可分别利用CDOWN或CUP,此时另一个时钟应为高电平。

当计数上溢出时,进位输出端(CARRY)输出一个低电平脉冲,其宽度为CUP低电平部分的低电平脉冲;当计数下溢出时,错位输出端(BORROW)输出一个低电平脉冲,其宽度为CDOWN低电平部分的低电平脉冲。

当把BORROW和CARRY分别连接后一级的CDOWN、CUP,即可进行级联。

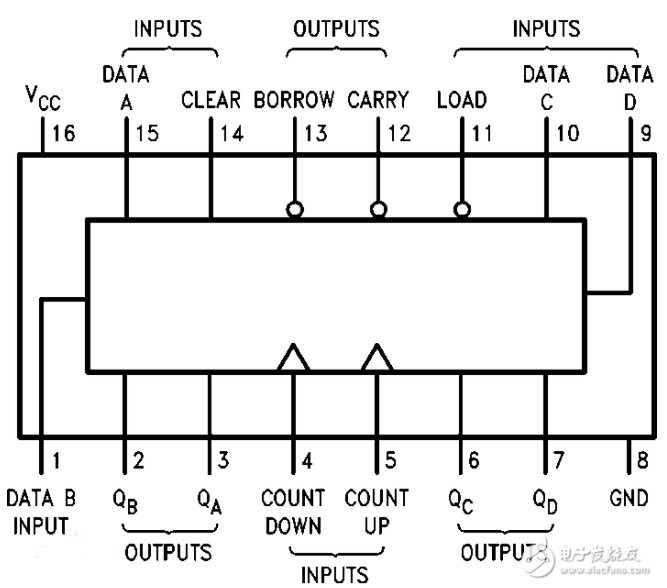

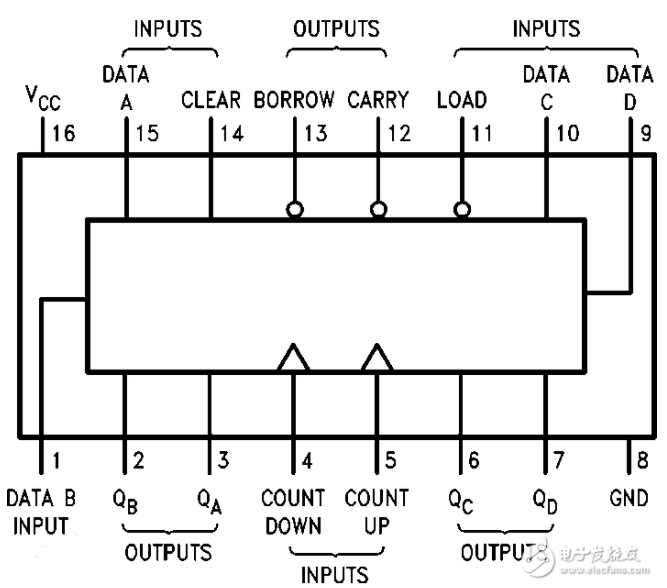

74ls193引脚图:

74LS193引脚图

74ls193引脚说明:

-

BORROW错位输出端(低电平有效)

-

CARRY进位输出端(低电平有效)

-

CDOWN减计数时钟输入端(上升沿有效)

-

CUP加计数时钟输入端(上升沿有效)

-

CLEAR异步清除端

-

A-D并行数据输入端

-

LOAD异步并行置入控制端(低电平有效)

-

QA-QD输出端

74ls193功能表:

74LS193功能表

文章综合来源:360doc

编辑:ymf

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

二进制

+关注

关注

2文章

809浏览量

43170 -

双时钟模式

+关注

关注

0文章

3浏览量

5844 -

异步清零法

+关注

关注

4文章

3浏览量

6913

发布评论请先 登录

相关推荐

热点推荐

MAX5304:8引脚µMAX封装的10位电压输出DAC

MAX5304:8引脚µMAX封装的10位电压输出DAC 在电子设计领域,数模转换器(DAC)是连接数字世界和模拟世界的关键桥梁。今天我们要深入探讨的是MAXIM公司的MAX5304,一款采用8引脚

MAX522:8引脚封装的双8位电压输出串行DAC

MAX522:8引脚封装的双8位电压输出串行DAC 在电子设计领域,数字模拟转换器(DAC)是连接数字世界和模拟世界的重要桥梁。今天要给大家介绍的是MAXIM公司的MAX522,一款采用8引脚SO

探索C8051F531:高性能20引脚汽车MCU的卓越表现

探索C8051F531:高性能20引脚汽车MCU的卓越表现 在电子设计领域,选择一款合适的微控制器(MCU)至关重要,它直接影响到产品的性能、功能和成本。今天,我们就来深入了解一下Silicon

20位引脚可编程低功耗Σ-Δ ADC AD7781:特性、应用与设计要点

就来深入探讨一款由ADI公司推出的20位引脚可编程低功耗Σ-Δ ADC——AD7781,了解它的特性、应用场景以及设计过程中的注意事项。 文件下载: AD7781.pdf 一、AD7781的特性亮点 1. 引脚可编程功能 AD7

开尔文连接使用合科泰RMS系列4引脚合金电阻实现高精度

开尔文连接通过将功率回路与测量回路物理分离,从原理上切断了上述干扰路径。本文以合科泰RMS系列4引脚合金电阻为例,分析开尔文连接在大电流采样中的精度保障机制,并通过实测数据与工程案例,说明高精度采样对系统性能的量化提升。

SN54LS422、SN54LS423、SN74LS422、SN74LS423可重触发单稳态多谐振荡器的特性与应用

SN54LS422、SN54LS423、SN74LS422、SN74LS423可重触发单稳态多谐振荡器的特性与应用 在电子设计领域,单稳态多谐振荡器是一种常用的电路元件,它能够产生精确

探索MAX823/MAX824/MAX825:5引脚微处理器监控电路的卓越性能

的MAX823/MAX824/MAX825系列5引脚微处理器监控电路,它集成了复位输出、看门狗和手动复位输入功能,为各类应用提供了强大的支持。 文件下载: MAX823REUK+T.pdf 产品概述

SN54LS422、SN54LS423、SN74LS422 和 SN74LS423 可重触发单稳态多谐振荡器详解

SN54LS422、SN54LS423、SN74LS422 和 SN74LS423 可重触发单稳态多谐振荡器详解 在电子设计领域,单稳态多谐振荡器是一种常用的电路元件,能够产生特定宽度

SN54LS422、SN54LS423、SN74LS422、SN74LS423可重触发单稳态多谐振荡器解析

SN54LS422、SN54LS423、SN74LS422、SN74LS423可重触发单稳态多谐振荡器解析 作为电子工程师,在设计中常常会用到单稳态多谐振荡器,今天就来详细介绍一下SN

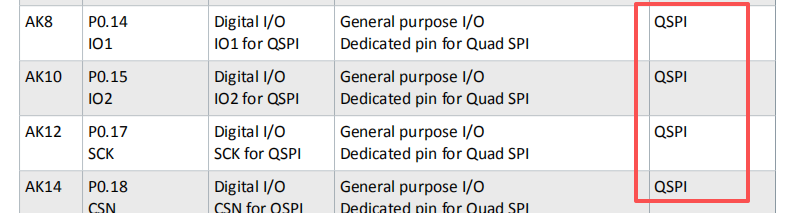

【Nordic随笔】nRF5340引脚分配问题

【Nordic随笔】nRF5340引脚问题 本文章主要说明一下nRF5340引脚问题,因为nRF5340是双核架构,所以有部分引脚是被分配到网络核的,以及有部分特殊引脚的分配 为什么发

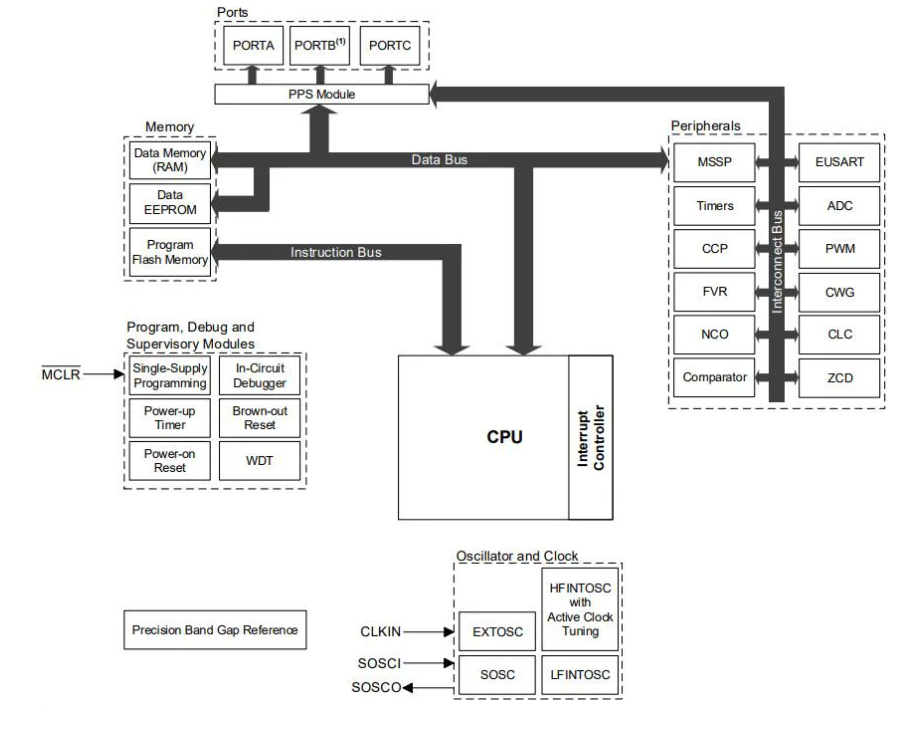

PIC16F18026/46:功能丰富的14/20引脚微控制器深度解析

Microchip Technology PIC16F18026/46 14/20引脚微控制器具有数字和模拟外设,用于成本敏感的传感器和实时控制应用。这些微控制器采用8至44引脚封装,内存范围为

新品 | CoolSiC™ MOSFET 1200V分立器件TO247-4引脚IMZA封装

新品CoolSiCMOSFET1200V分立器件TO247-4引脚IMZA封装第二代CoolSiCMOSFETG21200V/53mΩ,TO247-4引脚IMZA封装,确保安装兼容性并可轻松替换现有

请问为什么M0519引脚的某些部分在配置为GPIO功能后无法将输出控制到高电平或低电平状态?

为什么M0519引脚的某些部分在配置为GPIO功能后无法将输出控制到高电平或低电平状态?

发表于 08-27 15:00

光耦817引脚图及参数详解:电子设计中的“隔离神器”

,当LED发光时,光电晶体管会感应到光信号并导通,从而实现信号的传递。

光耦817广泛应用于电源、通信、工业控制等领域,是电子设计中不可或缺的元器件之一。

二、光耦817引脚图

光耦817通常采用4引脚

发表于 06-06 08:50

74ls193引脚图及功能表

74ls193引脚图及功能表

评论