一、Flash基本原理及分类

1.1、基本存储单元

存储数据基本的元件:浮栅场效应管

存储时,信息存放在浮置栅极中,浮置栅极有无电荷或电荷量来表明当前存储的数据:

1.2、存储颗粒分类

当前存储颗粒主要分类:SLC、MLC、TLC、QLC

单位存储单元下数据存储密度:(一个存储单元要表示的数据类型)

SLC (Single-Level Cell) 单个存储单元存储1bit数据,即表示2种(2^1)数据状态:0和1

MLC (Multi-Level Cell) 单个存储单元存储2bit数据,即表示4种(2^2)数据状态:00,01,10,11

TLC (Trinary-Level Cell) 单个存储单元存储3bit数据,即表示8种(2^3)数据状态:000,……,111

QLC (Quad-Level Cell) 单个存储单元存储4bit数据,即表示16种(2^4)数据状态:0000,……,1111

注:单个存储单元:指一个浮栅场效应管

对于一个存储单元存储多个bit的情况,识别和写入通常是通过控制阈值电压来实现,阈值电压可以通过调整浮置栅极的电荷量(电荷量越多导通性越好,分压越小)实现。

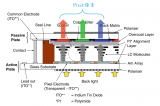

颗粒配合制作工艺实现:2D和3D Flash技术,2D最早在SLC阶段应用广泛,3D在TLC阶段应用广发,具体结构区分:

2D内部结构:

3D内部构造:

3D芯片内部结构:

1.3、Flash存储分类

存储技术分类:NandFlash、NorFlash

存储芯片分类:目前市面上常见的集成存储芯片类型:eMMC、UFS、SPI-Flash、QSPI-Flash、各尺寸的SD卡等。

NandFlash存储阵列:

NorFlash存储阵列:

写入数据:

NorFlash:热电子注入效应(高压沟道雪崩击穿注入电子流)

NandFlash:F-N隧道效应(P/N结半导体导电特性)

读取时控制栅极的控制电压不会过大影响浮置栅极的电荷,因此可以依据有无电荷读取存储的数据,当浮置栅极有电荷时,源极和漏极可以导通,读取到的bit是0;擦除后浮置栅极无电荷,源极和漏极不能导通,读取的bit是1(控制栅极的电平);

读取数据:

NorFlash一次最小可以读取1bit数据,NandFlash一次最小可以读取1byte数据;

擦除数据:

NorFlash和NandFlash都是通过F-N隧道效应擦除数据(消耗浮置栅极的电荷)

1.4、NandFlash和NorFlash异同

NandFlash:

存储容量:适用于大容量的场景,不可运行程序;

擦写次数:擦写次数相对NorFlash较高;

擦写方式:按块、页擦写,可擦写次数较多,读写速率相对较高;

硬件接口:I/O口是数据线和地址线复用,通过CS等控制引脚控制时序完成地址传输和数据传输;

缺陷:需要管理坏块,NandFlash存在随机坏块问题,需要算法探测坏块并本分数据,EDC/ECC等一般在文件系统下实现,时序操作负责容易引起错误,只能以块为单位擦写,整体寿命相对短;

应用:当前市场的NandFlash用于大容量产品,如SSD的Flash、EMMC的Flash、UFS的Flash等都是NandFlash,不同的是SSD、EMMC、UFS等芯片集成的控制器和对外接口类型不同。

常见产品:市场常见产品均是串行接口,集成了控制器,控制器中集成坏块替换、均衡等管理;

SSD(solid state disk)可以向外提供SATA或PCIe接口(代表产品有M.2 SSD,兼容SATA和PCIe接口);

EMMC(embeded MultiMedia Card)集成的控制器对外提供的接口类似于NandFlash的接口,统称SDIO(适用于SD卡的数据总线类型),以I/O地址数据线复用形式提供,CMD等实现指令操作;

UFS(Universal Flash Storage)对外提供的接口MIPI(Mobile Industry Processor Interface:该接口由ARM组织发起,目的是将摄像头、LCD显示屏、存储设备等统一为一个总线规范),处理器也需要支持MIPI接口,目前较新智能手机的SOC(ARM核)一般都支持该接口;

NorFlash:

存储容量:适用于存储容量小的场景,可运行程序;

擦写次数:擦写次数相对NandFlash较低;

擦写方式:按bit擦写,极少出现坏块,可靠性高,写入速率相对低,读取速率和NandFlash相差不大;

硬件接口:地址总线和数据总线是分开的,读写速率相对较高;

缺陷:写入速度低,可擦写次数相对NandFlash低;

应用:当前市场的NorFlash主要有串行和并行两种接口形式,并行的NorFlash芯片提供类似SRAM的接口,即有地址总线和数据总线,串行的NorFlash一般提供SPI等串行协议的接口实现数据读写;

二、Flash的硬件电气特性

2.1、芯片封装类型

芯片封装依据厂商的设计和应用场景而不同,目前主要有SOP类、BGA类,相关封装对应的引脚定义参见以下描述;数据通道依据不同芯片也有不同的设计,当前有8bit数据通道和16bit数据通道。

以下是NandFlash的常见芯片封装和引脚定义:

SOP类芯片封装

8根数据线的存储芯片:

16根数据线的存储芯片:

BGA类芯片封装

8根数据线的存储芯片:

16根数据线的存储芯片:

LGA-52封装尺寸:

其他封装具体参见开源文档《Open Nand Flash Interface》描述。

以下是NorFlash的常见芯片封装和引脚定义:

2.2、芯片和处理器接口

飞思卡尔(现属于NXP)处理器下,存储芯片等的硬件接口统称为IFC(Integrated flash controller),该总线在嵌入式系统中比较常见。IFC总线可以连接NandFlash、NorFlash、SRAM/DDR、EEPROM以及ASIC类,处理器的IFC总线一般带有NandFlash和NorFlash的控制器,以硬件的形式完成NandFlash或NorFlash的访问和控制;

以LS1021A处理器(ARM核)为例:

The IFC contains one NAND controller, one NOR flash controller, and one GPCM/generic-ASIC controller.

即IFC总线包含了NorFlash/NandFlash/GPCM/ASIC等控制器,帮助处理器完成对外围存储、器件的访问。

由上一节的芯片硬件接口可以看出,NandFlash没有数据线和地址线,只有I/O总线,其余引脚用于时序控制完成对应功能;

RK系列ARM处理器(瑞芯微),处理器对外的存储器接口,均以集成的方式展现,如MIPI、EMMC PHY等,这种情况下,就需要EMMC、UFS等芯片去连接,而不能直接用NandFlash连接到处理器上。

全志A、H系列ARM处理器,可以通过本地数据总线连接NandFlash,但名称不叫IFC,其中RK系列处理器的外置存储控制器,更适用于安卓系统的驱动,对于嵌入式系统也是一个新的发展趋势。

2.3、Flash读写

NorFlash需要热电子注入,因此需要升压,电压要高于当前芯片的逻辑电压,因此NorFlash的写入速度较低,同样电压低的器件速度快,CPU从最初的5V电源系统更新到3.3V,乃至最新的1.8V和1.2V,都是为了提高元件的运行速度(频率),减少因逻辑切换引起的电压变换时延。

NandFlash由于借助半导体的P/N结特性,不存在电压超过芯片自身工作电压的工作情况,因此写入速度要大于NorFlash。

NorFlash和NandFlash的擦除速度相当,擦除原理均基于P/N结特性(F-N隧道效应),因此擦除速率几乎相等。

NandFlash的读写命令字规定(来自ONFI标准):

注:此规定是ONFI规定的,并非某厂商芯片的使用说明,某型号的芯片需要参照相关数据手册。

Flash的读、写、擦以及回写操作应为原子操作,执行原子操作时不应切换逻辑分区选择!

读取(包含回读)

o 《CMD: 00h》 《ADDR: Column & Row》 《CMD: 30h》

o 《CMD: 00h》 《ADDR: Column & Row》 《CMD: 31h》

o 《CMD: 00h》 《ADDR: Column & Row》 《CMD: 32h》

o 《CMD: 00h》 《ADDR: Column & Row》 《CMD: 35h》

•编程注意事项(包括回写编程):The Volume Select command may be issued prior to the 10h, 11h, or 15h command if the next command to this Volume is Change Row Address. After Volume Select command is issued to resume data input, the host shall wait tCCS before issuing Change Row Address command. o 《CMD: 80h》 《ADDR: Column & Row》 《DIN: Data Input》 《CMD: 10h》

o 《CMD: 80h》 《ADDR: Column & Row》 《DIN: Data Input》 《CMD: 11h》

o 《CMD: 80h》 《ADDR: Column & Row》 《DIN: Data Input》 《CMD: 15h》

o 《CMD: 81h》 《ADDR: Column & Row》 《DIN: Data Input》 《CMD: 10h》

o 《CMD: 81h》 《ADDR: Column & Row》 《DIN: Data Input》 《CMD: 11h》

o 《CMD: 81h》 《ADDR: Column & Row》 《DIN: Data Input》 《CMD: 15h》

o 《CMD: 85h》 《ADDR: Column & Row》 《DIN: Data Input》 《CMD: 10h》

o 《CMD: 85h》 《ADDR: Column & Row》 《DIN: Data Input》 《CMD: 11h》

o 《CMD: 85h》 《ADDR: Column & Row》 《DIN: Data Input》 《CMD: 15h》

• 擦除Flash命令:

o 《CMD: 60h》 《ADDR: Row》 《CMD: D0h》

o 《CMD: 60h》 《ADDR: Row》 《CMD: D1h》

o 《CMD: 60h》 《ADDR: Row》 《CMD: 60h》 《ADDR: Row》 《CMD: D1h》

2.4、制造工艺

制程相对CPU的小,一般在28nm左右

三、软件适配和文件系统

3.1、文件系统

此处以Linux为例。

Linux操作系统本身支持很多文件系统:ext系列(2~4)、cramfs、ubifs、jffs2、yaffs、yaffs2、等。

如果是发行版的linux,可以查看:/lib/modules/3.10.0-327.el7.x86_64/build/fs 目录下的文件夹,即可知道当前的linux支持的文件系统,同时该发行版支持的文件系统工具可以查看:ls /usr/sbin/ | grep mkfs。

如果是自行开发的linux内核,则在linux内核编译时,已由开发人员指定了内核支持的文件系统类型,(处理器架构非x86时)开启UBIFS选项如下图:

Linux下使用MTD工具管理Flash,其中支持在Flash上运行的文件系统有:cramfs、jffs、、ubifs等

Linux下文件系统的目录:

3.2、软件适配

Linux下适配NandFlash、NorFlash的分区信息时,通常是在设备树中配置mtd信息,以供linux启动后,用户层软件可以通过linux的ioctl实现对NandFlash或者NorFlash进行读写操作,来完成底层flash的数据替换等操作。

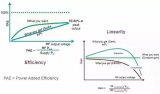

四、性能对比

各类型颗粒性能对比。

Nand和Nor特性参数对比。

责任编辑:lq6

-

FlaSh

+关注

关注

10文章

1759浏览量

155900

原文标题:Flash(NandFlash&NorFlash)基本原理

文章出处:【微信号:gh_9d9a609c9302,微信公众号:SoC芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

NOR FLASH和NAND FLASH的对比

自适应滤波算法介绍之维纳滤波器的基本原理和应用示例

初识马达基本原理及组成部分

X-ray检查机的基本原理、主要类型和区别

FPGA实现基于SPI协议的Flash驱动控制芯片擦除

基于级联分类器的人脸检测基本原理

简述冲击电压发生器的基本原理?

主流显示技术的基本原理与分类

NAND Flash的基本原理和结构

单相调压器和三相调压器的基本原理与主要结构

射频功率放大器的基本原理和组成部分

微加工激光蚀刻技术的基本原理及特点

POE供电的基本原理,网络变压器的作用 网变的POE供电

了解信号完整性的基本原理

Flash的基本原理及分类是什么?

Flash的基本原理及分类是什么?

评论