本讲使用matlab产生待滤波信号,并编写testbench进行仿真分析,在Vivado中调用FIR滤波器的IP核进行滤波测试,下一讲使用两个DDS产生待滤波的信号,第五讲或第六讲开始编写verilog代码设计FIR滤波器,不再调用IP核。

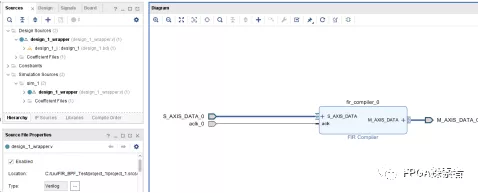

本例使用上一讲的FIR滤波器IP核工程。

matlab与FPGA数字滤波器设计(2)——Vivado调用IP核设计FIR滤波器

matlab与FPGA数字滤波器设计(1)——通过matlab的fdatool工具箱设计FIR数字滤波器

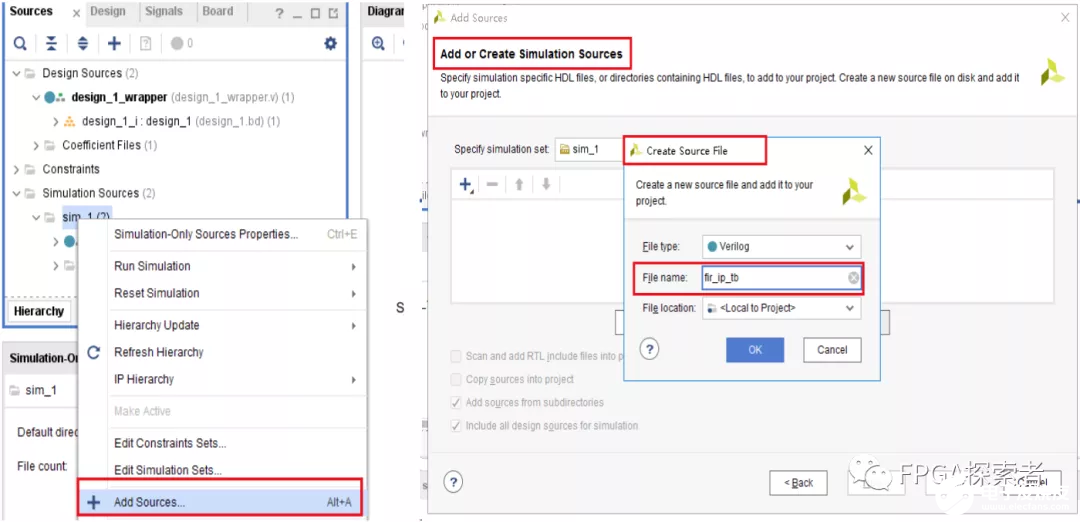

1. 新建仿真文件

(1) Simulation Sources -》 sim_1 -》右键 Add Sources;

(2) Add or Create Simulation Sources,新建仿真文件 fir_ip_tb;

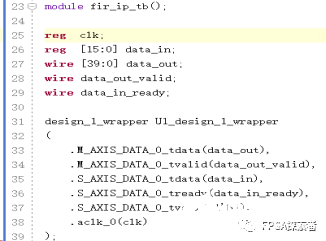

2. 编写testbench

(1) 例化加入的IP核,其中:

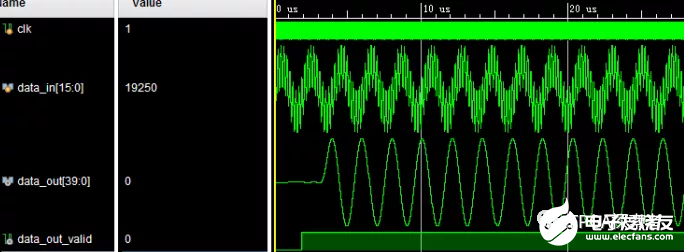

输入时钟引脚为 clk,设置为32MHz(此处暂时还未设定频率);

输入数据引脚为data_in,位宽16-bit,表示待滤波数据;

输出数据引脚为data_out,位宽40-bit,表示滤波后的数据;

输出数据有效信号引脚data_out_valid,位宽1-bit,输出状态,为高电平时表示输出的data_out有效;

输入数据准备好信号引脚data_in_ready,位宽1-bit,输出状态,为高电平时表示准备好接收输入数据;

输入有效信号S_AXIS_DATA_0_tvalid,为1时表示输入信号有效,为0时即使有输入信号data_in到 fir 的 ip 核 ,ip 核也不做处理,此处直接让其恒为1,输入数据恒有效;

总结,需要给ip核输入的数据目前只有两个,一个是时钟,一个是待滤波数据。

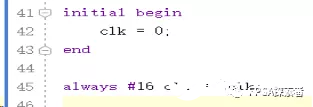

(2) 产生32MHz时钟信号;

初始 initial 时设置时钟信号clk为低电平0,always 表示一直执行,#16表示每隔16 ns(单位是在仿真文件开头自动有定义ns)时钟取反一次,即每隔 16ns 时钟 0/1间隔变化,相当于32ns一个时钟周期,约等于32MHz;

3. 产生待滤波数据data_in

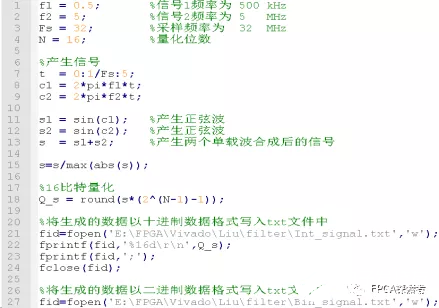

(1) 编写matlab程序,产生两个信号0.5MHz和5MHz,采样频率32MHz,采样5个周期,进行16-bit量化,并把量化后的数据写到 .txt 文件中;

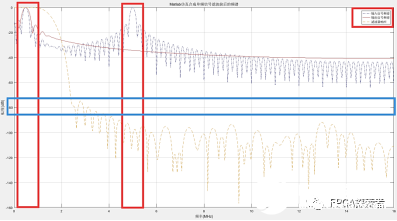

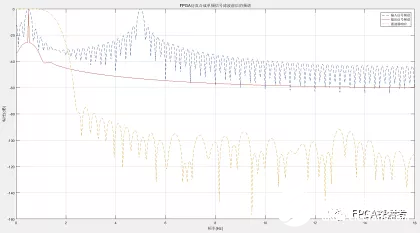

可以看到,在 0.5MHz 和 5MHz处有两个峰,表示抽样后的两个信号,经过滤波器之后,5MHz 信号被滤除,只剩下 0.5MHz 信号,蓝色框内可以看到,在 3MHz 以后滤波器的响应已经低于 -80dB,相当于滤波后的幅度是滤波前的1/10000,滤波效果很好。

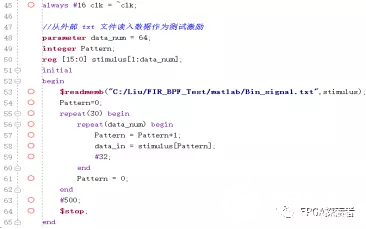

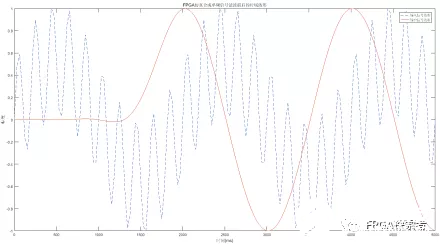

使用 32MHz 的采样时钟采样 0.5MHz 待滤波信号(相当于0.5MHz信号叠加了5MHz噪声),每个周期采样 64 个点,在testbench中读取一个周期的64个点,重复30个周期得到30个周期的输入待滤波信号给FIR滤波器;

4. 仿真结果分析

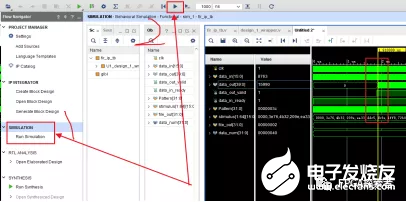

点击1处开始仿真,Vivado中一般默认只会仿真1us,这时候只看到了初始化的一部分,是看不到后续结果的,点击2处进行仿真,会将所有的仿真步骤完成,执行到上图中第64行的 $stop 语句停止仿真;

5. 仿真结果分析

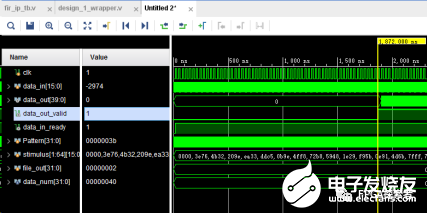

(1) data_out_valid:初始为0,在1.872 ns跳变为1,输出数据开始有效,在为0的那段时间输出数据data_out无效,这段时间内是FIR的IP核进行一些内部的配置和初始化;

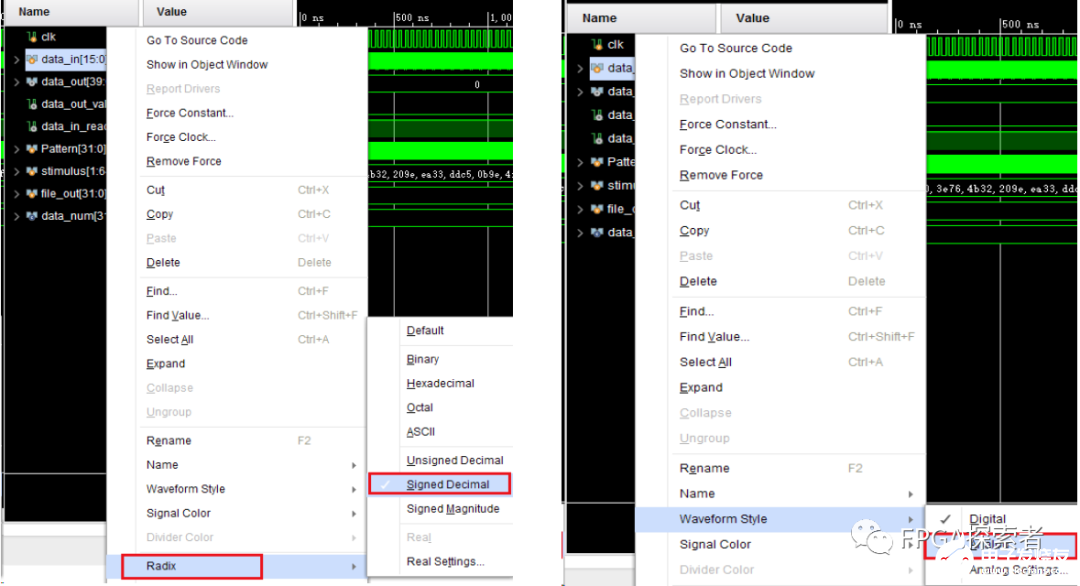

(2) 更改数据表示模式

对data_in,右键设置其数据格式Radix为有符号的十进制数(Signed Decimal),设置其波形为模拟波形(Analog);

对 data_out 同样设置;

对 Pattern 设置 无符号十进制,不需要设置波形。

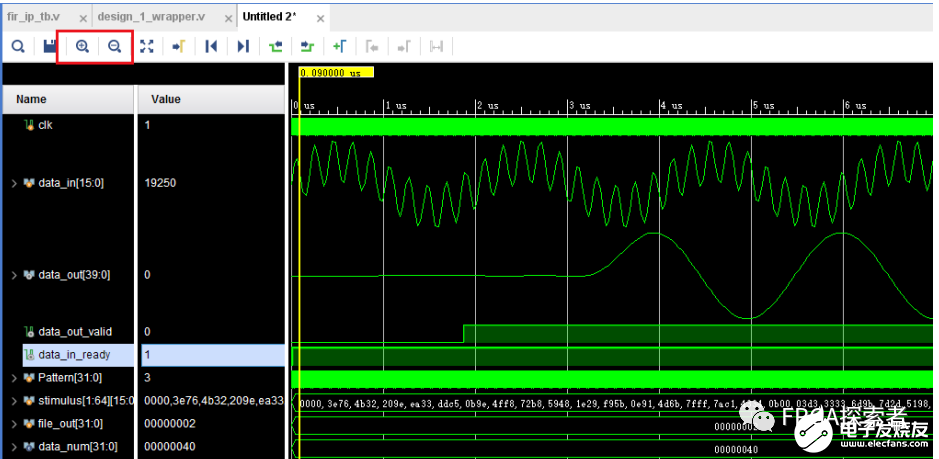

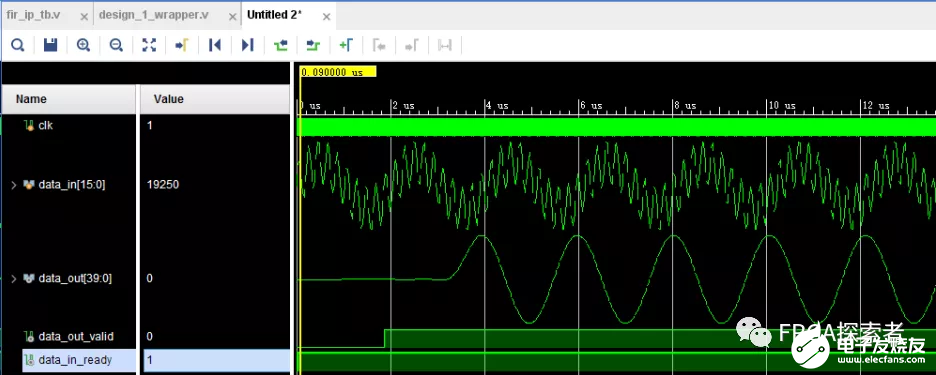

(3) 点击放大缩小可以查看整个仿真的效果

通过下面几图,可以看到仿真效果很好,5MHz高频噪声滤除干净,肉眼观察不出来。

(4) Matlab数据分析

肉眼观察时域的仿真图无法得知高频噪声具体被滤掉了多少,是否还混有噪声,此时需要将滤波后的数据按照前文读取仿真数据的方式,将仿真得到的滤波后的数据写入.txt文件,再通过 matlab 读取 FPGA 滤波后的数据并进行FFT 频谱分析,通过频域的波形来观察滤波效果,通过 matlab 仿真,可以看到高频信号的确被滤除。

下一讲使用两个 DDS 产生待滤波的信号,结合FIR滤波器搭建一个信号产生及滤波的系统,并编写testbench进行仿真分析。

编辑:lyn

-

matlab

+关注

关注

189文章

3018浏览量

237601 -

仿真

+关注

关注

53文章

4407浏览量

137671 -

fir滤波器

+关注

关注

1文章

97浏览量

19627 -

Vivado

+关注

关注

19文章

846浏览量

70475

发布评论请先 登录

求助,关于testbench仿真的问题求解

语法纠错和testbench的自动生成

基于Matlab与FPGA的双边滤波算法实现

无刷直流电机控制系统的建模仿真分析

利用MATLAB对交流电机调速系统进行建模和仿真

在testbench中如何使用阻塞赋值和非阻塞赋值

使用matlab产生待滤波信号并编写testbench进行仿真分析

使用matlab产生待滤波信号并编写testbench进行仿真分析

评论