0引言

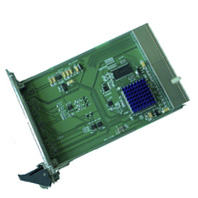

CPCI总线[1]是由PCI总线发展而来的一种紧凑型32/64 bit局部总线,最高带宽可达512 MB/s。因其具有高开放性、高可靠性、可热插拔等优点,被广泛应用于航空航天、信息通信、工业控制、数据采集等领域。相对于传统的以单片机、MCU为核心的数据处理系统,现场可编程门阵列(Field Programmable Gate Array,FPGA)以其高速、灵活、高集成度、高性能、抗干扰、现场可编程等优点,在上述领域中得到了广泛应用[2]。本设计将CPCI总线技术与FPGA技术巧妙结合,以Altera公司的高性能芯片EP3C40F324I7为核心处理器,根据应用需求,研制开发了一款实时性强、可靠性高的多功能通信卡。

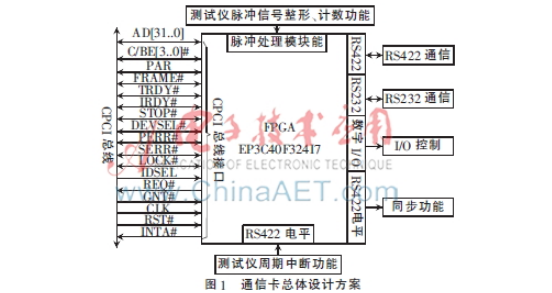

1 多功能通信卡总体方案

FPGA核心处理器EP3C40F324I7通过CPCI总线与主机进行信息交互,主要实现各模块信号采集、处理、传输等功能。主机通过CPCI总线发送命令、数据,FPGA微处理器接到指令后,对相关信号进行处理,将处理结果通过CPCI总线反馈给主机,并通过标准的通信接口外接引出,从而进行分析、计算。该多功能通信卡总体方案如图1所示。

2 硬件设计

2.1 FPGA芯片选型与设计

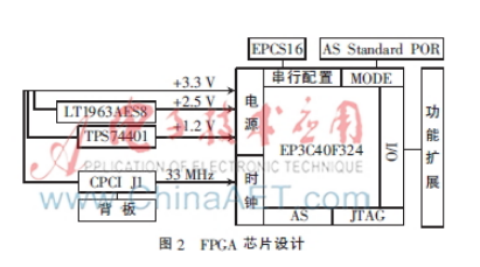

本设计中FPGA微处理器通过CPCI总线实现RS232串行通信、RS422串行通信、脉冲计数、数字输出等多种功能,综合考虑FPGA内部存储单元数量、I/O引脚数量等因素,选择Altera公司的EP3C40F324用于功能模块开发。EP3C40F324为FPGA封装,内部LE 39 600个,M9K 126个,RAM总量为1 161 216 bit,18×18的乘法器126个,锁相环4个,全局时钟网络20个,可用I/O口195个,可用差分通道61个,可以满足系统开发需求。

EP3C40F324需3种供电电压,I/O供电电压为+3.3 V,PLL的模拟供电电压为+2.5 V,内核及PLL的数字供电电压均为+1.2 V。其中,+3.3 V由背板经CPCI J1直接供给,+2.5 V通过电源芯片LT1963AES8由+3.3 V转换而得,+1.2 V通过电源芯片TPS74401由+3.3 V转换而得。设计中,充分考虑到芯片功耗问题,内核及PLL的数字供电特采用TI公司的TPS74401电源芯片将+3.3 V转换为+1.2 V,其输出电流为3 A,保证了电源功率。

FPGA的输入时钟由背板经CPCI J1提供,使CPCI总线频率稳定在33 MHz。FPGA的上电复位模式选择AS Standard POR。采用增强型配置芯片EPCS16对FPGA进行了主动串行(AS)配置,同时利用微处理器本身进行了基于JTAG的配置。两种配置方案,保证了FPGA程序烧录的可靠性、稳定性。FPGA芯片设计如图2所示。

2.2 总线接口设计

本设计中采用32 bit/33 MHz CPCI总线接口,其传输率可达133 MB/s,实现了设备之间的高速通信。通过CPCI连接器,CPCI总线信号与FPGA的I/O口互连。

FPGA微处理器通过地址和数据信号AD[31..00]、总线命令和字节使能信号C/BE[3..0]#与主机进行I/O地址的选择,以及数据、命令的传输。FRAME#、TRDY#、IRDY#、STOP#、DEVSEL#、IDSEL等接口控制信号用于设备选择、读写控制。FPGA微处理器如需占用总线,则需向主机发出总线占用请求信号REQ#,主机收到总线占用请求信号后,通过仲裁向FPGA微处理器发送总线占用允许信号GNT#。由于总线上没有挂接其他设备,故总线的使用由FPGA微处理器独占。INTA#用于向总线进行中断请求,以实现中断功能。通信过程中如有错误发生,则FPGA微处理器通过PERR#、SERR#与主机进行错误报告,以保证数据传输可靠、完整[3]。

2.3 脉冲信号处理电路设计

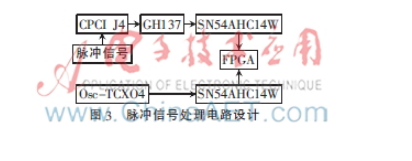

被测设备的脉冲信号通过CPCI J4连接器进入板卡。利用光电耦合器GH137对脉冲进行光电隔离,以减少板上其他信号的干扰,提高脉冲数字信号的抗干扰能力。经过光耦隔离的脉冲数字信号,由TI公司的SN54AHC14W进行波形整形。SN54AHC14W是带有施密特触发的6路反相器。施密特触发器是脉冲波形变换中经常使用的一种电路,不仅能将边沿变化缓慢的信号波形整形为边沿陡峭的矩形波,而且可以将叠加在矩形脉冲高、低电平上的噪声有效地清除。故经过SN54AHC14W整形的脉冲数字信号波形更加理想,易于FPGA微处理器进行处理、计数。

高稳定度温度补偿晶体振荡器Osc-TCXO4产生的1 024 kHz时钟脉冲,经SN54AHC14W整形后送入FPGA,供脉冲计数使用。由于本板卡应用于军工、国防领域,需要非常稳定的晶振,故采用温度补偿晶体振荡器。TCXO温度补偿通过改变振荡回路中负载电容,使其随温度变化来补偿由于环境温度变化产生的频率漂移,从而产生精度非常高的时钟,提高脉冲计数精度。脉冲信号处理电路如图3所示。

2.4 差分接口设计

本设计中有2路RS232串口,4路RS422串口,最高传输率分别为115.2 kb/s、921.6 kb/s。由于应用条件严苛,设计中选用了电磁隔离器件,大大提高了通信的可靠性。RS232收发器选用AD公司的ADM3251E,其数据传输率最高可达460 kb/s。RS422收发器选用AD公司的ADM2582E,其数据传输率最高可达16 Mb/s。二者均在器件内部集成了DC-DC转换器,有效地降低了干扰,且其传输速率也满足使用需求。同时,由于主机串口传输率为9 600 b/s,故选择22.118 4 MHz的晶振为串行通信提供稳定时钟。

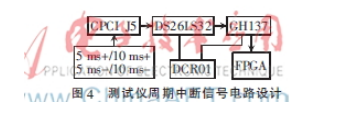

被测设备将周期5 ms和10 ms的时钟信号输出给板卡,作为测试仪周期中断信号。时钟接口电路采用422差分协议,电平采用422电平。时钟信号经CPCI J5连接器进入板卡,接收器采用NS公司的4路差分接收器DS26LS32,以满足422电平标准。调理之后的422电平信号经光电耦合器GH137加以隔离,以减少其他信号的干扰。

由于DS26LS32、GH137内部未集成DC-DC转换功能,故需要有单独的DC-DC电源模块将板上电源进行隔离,以给二者供电。此处选用了TI公司的DCR01系列芯片完成隔离电源供电的功能。测试仪周期中断信号电路设计如图4所示。

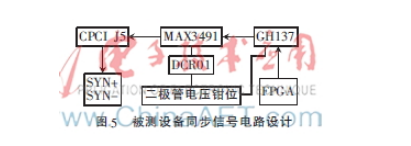

测试仪向被测设备发送RS422差分信号作为被测设备同步信号。同步信号接口电路采用422差分协议,电平采用422电平。同步脉冲从FPGA微处理器送出后,经光电耦合器GH137隔离,进入MAXIM公司的MAX3491收发器。MAX3491的数据传输速率可达10 Mb/s,满足传输要求。信号经CPCI J5连接器外送至被测设备,以校准时差,实现被测设备同步功能。

同时,为减少其他信号的干扰,将对时脉冲采取隔离措施,由TI公司的DCR01系列电源芯片单独供电。由于MAX3491与GH137的供电电压不同,故通过二极管串联电压钳位的方式获得合适的供电电压为GH137供电,有效解决了隔离供电问题。被测设备同步信号电路设计如图5所示。

2.5 数字输出电路设计

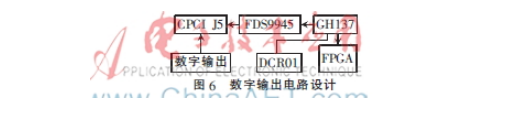

测试仪的I/O功能由数字输出量来实现。FPGA通过设置寄存器方式向外输出高低电平,以实现复位、控制等功能。高低电平从FPGA发出,经光电耦合器GH137隔离,提高信号抗干扰性能。经隔离的信号进入FAIRCHILD公司的FDS9945作为电平控制信号。

FDS9945内部为N沟道MOSFET,电平控制信号连接于场效应管的栅极G(Gate),场效应管的源极S(Source)接隔离地,漏极D(Drain)的输出可作为复位、控制信号。漏极D的输出电平经CPCI J5连接器外送至被控制的对象。利用MOS管的开关特性,通过改变栅极G的电平来控制场效应管源极S、漏极D的通断,从而实现复位、控制等功能[4]。数字输出电路设计如图6所示。

3 FPGA程序设计

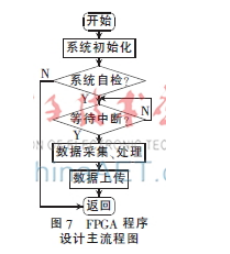

本采集卡FPGA逻辑设计采用Verilog代码[5]实现,主要实现数据采集、存储、读写等命令控制,其主流程图如图7所示。FPGA主要实现CPCI接口到RS232、RS422等接口转换,以及422电平输入输出、数字输出、脉冲计数等功能。PCI BAR0映射为8 KB IO空间,BAR1映射为1 MB Memory空间。PCI采用中断复用,通过使能中断寄存器而触发不同协议的中断,如RS232、RS422通信等,从而分别调用相应的中断服务程序完成通信任务。

4 结果分析

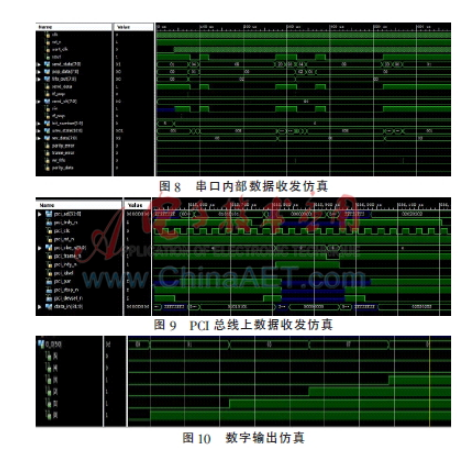

图8为串口内部数据收发仿真,图9为总线上数据收发仿真,图10为数字输出仿真。由实验结果可知,该I/O卡在进行数据通信时,无论是串口内部的环回通信,还是PCI总线上的通信,读写信息一致,没有产生通信错误。同时,6路数字输出量也有由默认低电平到输出高电平的跳变,完成了相应的数字控制功能。可见,该I/O通信卡成功实现了数据的实时采集、处理、上传等功能,目前已投入实际应用之中,具有较高的使用价值。

参考文献

[1] PICMG. Compact PCI specification 2.0 R3.0[S]. 1999.

[2] 罗苑棠.CPLD/FPGA常用模块与综合系统设计实例精讲[M].北京:电子工业出版社,2007.

[3] 李贵山,陈金鹏.PCI局部总线及其应用[M].西安:西安电子科技大学出版社,2003.

[4] 阎石.数字电子技术基础(第四版)[M].北京:高等教育出版社,2004.

[5] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2009.

编辑:jq

-

FPGA

+关注

关注

1664文章

22504浏览量

639316 -

CPCI总线

+关注

关注

0文章

28浏览量

14112 -

通信

+关注

关注

18文章

6451浏览量

140270

发布评论请先 登录

73S1217F:多功能智能卡读取器的理想之选

73S1215F:多功能片上系统助力智能卡读卡器设计

73S1209F:多功能智能卡读取IC的深度解析

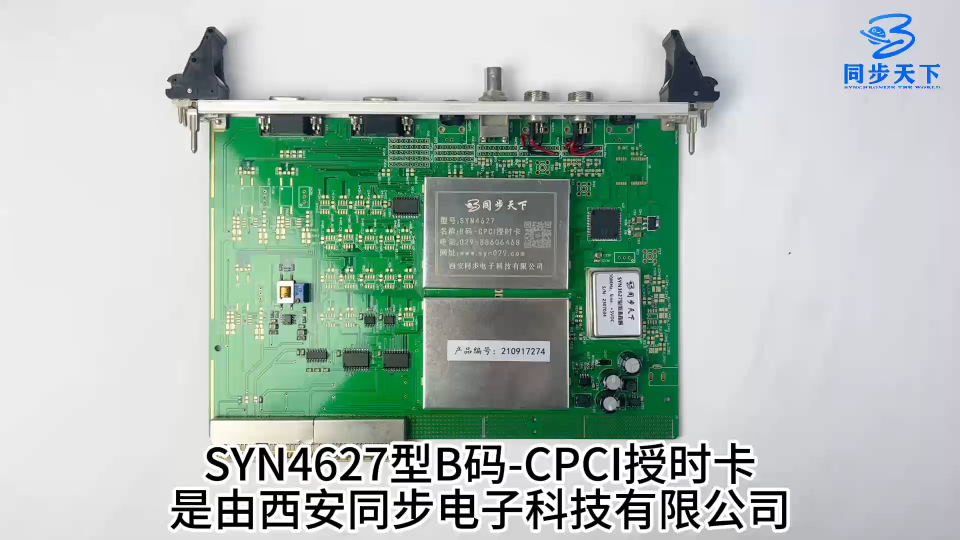

北斗授时板卡 pcie授时卡 微秒级卫星总线时钟同步卡推荐 双模pcie授时卡

fpga嵌入e203内核搭建soc如何实现通信功能?

基于瑞芯微 RK3588 的 ARM 与 FPGA 交互通信实战指南

简述关于FPGA的CPCI总线多功能通信卡的设计

简述关于FPGA的CPCI总线多功能通信卡的设计

评论