作者:李志刚,王明泉,任少卿,杨静

1 引言

随着中国机器人产业的迅猛发展,据预测到2010年,市场容量将超过93.1亿人民币。智能移动机器人是在室外环境中,将视频图像采集回来之后,按照预先给定的目标任务,结合已知的地理信息做出路径规划,在行驶的过程中能够不断感知和判断周围的环境信息,自主地做出各种决策,随时调整自身的行驶状态并执行相应的动作和操作。在这个过程中,视频采集质量的好坏将直接影响整个系统的运行,是进行后续数字图像处理的前提条件。因此,必须有高性能的硬件设备和高质量的算法作为基础,实时视频采集才成为可能。本文设计并实现了基于FPGA的嵌入式实时视频采集系统。该系统体积小,功耗低,速度快,适应性好,能够满足智能移动机器人视频信号处理系统的需求。

2 系统基本原理

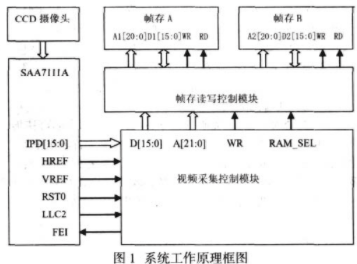

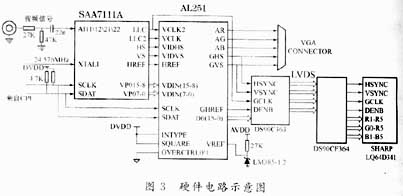

图1为系统工作原理框图,整个系统所需各种芯片的电路连接如下图所示,由CCD摄像头输出模拟视频信号,经过视频解码芯片SAA7111A进行视频预处理(钳位、放大、A/D转换、同步分离等)后输出图像数字信号IPD、行同步信号HREF、场同步信号VREF、奇偶场标志信号RST0和13.5MH像素时钟信号LLC2去驱动FPGA,从而产生正确的图像采集时序和存储地址,并将采集的图像存储到双口RAM中。整个系统由视频采集控制和帧存读写控制两个核心模块组成,它们的功能都由FPGA来实现。双口RAM分为帧存A和帧存B两个存储区域,实现乒乓式的读写操作,能够完成图像的实时采集。SAA7111A的配置程序和FPGA采集控制程序存储在FLASH中,系统上电工作时加载。

图1 系统工作原理框图

3 图像采集系统的构成

3.1 视频信号

视频信号中除了包含图像信号之外,还包括了行同步信号、行消隐信号、场同步信号(帧同步信号)、场消隐信号以及槽脉冲信号、前均衡脉冲、后均衡脉冲等。因而,对视频信号进行A/D转换的电路也非常复杂。Philips公司将这些非常复杂的视频A/D转换电路集成到了一块芯片内。从而生产出功能强大的视频输入处理芯片SAA7111A,为视频信号的数字化应用提供了极大的方便。

3.2 SAA7111A 性能及工作协议

SAA7111A是PHILIPS公司的一种增强型视频输入处理器芯片,它集A/D与解码功能于一身,片内还附有锁相、自动钳位控制、时钟自动增益产生、多制式解码等电路,另外还可对亮度、对比度和饱和度进行控制[2]。既支持PAL电视制式,又支持NTSC电视制式。SAA7111A内部含有I2C接口,可简洁的通过I2C总线对SAA7111A的工作方式进行设定。SAA7111A的场同步信号VREF、行同步信号HREF、奇偶场信号RST0、像素时钟信号LLC2都由引脚直接引出,从而省去了以往时钟同步电路的设计,其可靠性和方便性有了很大的提高。

图2所示为SAA7111A的功能方框图。从SAA7111A的四个模拟输入端AI11,AI12, AI21, AI22输入的视频图像信号,经模拟处理后,一路经A/D转换器后产生数字色度信号和亮度信号,分别进行亮度信号处理和色度信号处理。亮度信号处理的结果一路送到色度信号处理器,进行综合处理,产生Y和UV信号,经格式化后从VPO(16位)输出;另一路进入同步分离器,经数字PLL产生相应的行和场同步信号HS和VS,同时PLL驱动时钟发生器,产生与HS锁定的时钟信号LLC和像素时钟信号LLC2。所有这些功能均是在I2C总线控制下完成的,其中SCL为串行时钟信号,SDA为串行数据信号。

基金项目:中国博士后科学基金资助项目(2005038095);山西省自然科学基金资助项目(20051043);中北大学科学基金资助项目。

图2 SAA7111A功能方框图

SAA7111A的主要特点:

可编程选择四路视频输入的一路或两路,组成不同的工作模式,在其内部有两路模拟视频信号处理通道,可进行静态增益控制或自动增益控制,还有两路模数转换器;

可对芯片编程进行自电平控制、抗混叠滤波、梳状滤波;

场频50Hz或60Hz自动检测,并在PAL和NTSC制之间自动切换;

能对不同输入制式的亮度信号和色度信号进行处理,并实现亮度、色度和饱和度的片内控制;

提供两种数据方式供选择,这两种数据方式分别是RGB和YUV,可灵活输出不同的数字图像数据格式,主要有:4:1:1的YUV格式(12bit ), 4:2:2的YUV格式(16bit), 4:2:2的YUV格式[CCIR-656](8bit), 5:6:5的RGB格式(16bit)和8:8:8的RGB格式(24bit);

SAA7111A的工作模式由其内部的控制寄存器决定,需根据不同的视频标准来配置相应的内部寄存器,即初始化。用户根据I2C 总线协议,将需要的控制字写入控制地址即可对SAA7111A进行相应的控制。这些控制包括:图像数据输出格式、色彩、明暗、饱和度及各种参考信号的输出。I2C总线传送数据的基本时序如图3所示。

图3 I2C总线的基本时序

总线上的数据传输可以是读或写两种方式,其写格式为:

![]()

其中:S为总线起始信号;Slave Address W为被控器SAA7111的寻址字节;A为被控器应答信号;SubAddres为SAA7111控制寄存器的地址;Data(NB)即控制寄存器的配置参数为总线终止信号。

3.3 FPGA的采集控制原理

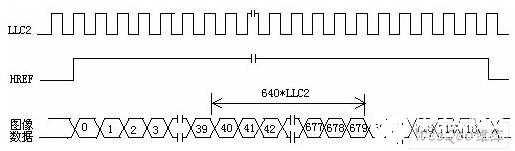

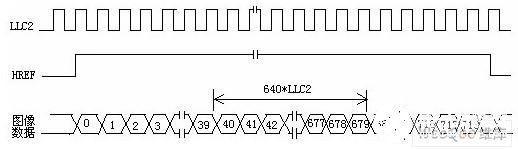

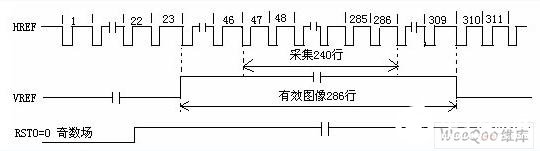

SAA7111A的输出时钟信号包括LLC(27MHz)和LLC2(13.5MHz),其中LLC2为像素时钟频率,每一时钟对应一个16位像素输出。行参考同步信号HREF,高电平表示一行的有效像素,为720个LLC2周期。场参考同步信号VREF高电平时表示输出是有效行图像,单场是286行;低电平期间为场消隐信号,是26个行周期。RTSO=1时表示输出为奇数场,RTSO=0时为偶数场。输入信号FEI为输出使能信号,为0时允许数据输出,为1时数据输出处于高阻状态。图4,5分别为采集一行和奇数场图像的信号时序图。

图4 SAA7111A采集一行图像的时序图

启动采集前必须对SAA7111A内部的32个寄存器写入相应的值。在采集的过程中,仅采集奇场图像信号而不采集偶场图像信号。因为只采集奇场信号也能得到稳定的图像,而可以利用偶场图像时间等待处理图像。对有效像素、无效像素、有效行和无效行进行计数,产生RAM的地址、读写、选通等控制信号,均由FPGA完成。由于只采奇场图像,行数也减少为原来的一半,为286行,前后各去掉23行,取中间240行。当RTSO为高电平且VREF上升沿到来时,标志奇数场开始,启动无效行计数器对HREF信号进行计数,计满前23行后,启动有效行计数器,置COUT信号为高电平,且在水平同步信号VREF=1、垂直同步信号HREF=1、奇偶场信号RTSO=1时,启动无效像素计数器,对LLC2二分频后的像素时钟信号进行计数。LLC2二分频后频率降为6.75MHz,每行像素点由原来的720点,减少为360点,将其截头去尾,前后各去掉20个像素,取一行中间的320个像素点,即得到分辨率为320 X 240的一帧图像。当无效像素计数器计满前20后,启动有效像素计数器开始计数,并将数据缓冲器打开,每计一次数,地址发生器加1,产生地址信号,读写信号WR,选通信号RAM_SEL,当一帧图像写完后,置FLAG信号为低,触发中断信号,以便处理器处理图像。值得注意的是,利用FPGA可以很灵活地控制存入RAM存储器中的图像数据量。这里将图像分辨率设计为320 X 240,实际应用中,可以根据需要灵活设置。

图5 SAA7111A奇数场采集的时序图

4 结束语

本文作者创新点:该系统能够完成对视频信号的采集,适应性极强的FPGA主要用于控制图像信号的采集,FPGA除了完成对SAA7111A配置以外,还完成图像提取处理、图像存储地址产生器等功能。由于FPGA的在线可编程特性使该系统变得更加灵活。此外,成熟的编译环境和FPGA与SAA7111A简单的外围电路大大缩短了开发和调试的周期。在未来的FPGA中还可以加入图像预处理流程,缩短后续处理时间,因此具有较高的推广价值。实验表明,系统速度快、可靠性高、实时性好,在视频采集和图像处理方面有着很好的应用前景。

责任编辑:gt

-

FPGA

+关注

关注

1655文章

22283浏览量

630235 -

芯片

+关注

关注

462文章

53534浏览量

459065 -

机器人

+关注

关注

213文章

30580浏览量

219550

发布评论请先 登录

用SAA7111A设计模拟视频转换接口

怎么实现PDP中的模拟视频数字化电路的设计?

saa7111中文资料

可编程视频信号输入处理器SAA7111

视频解码技术中I2C总线控制核的实现

基于DM642的SAA7113H 视频采集模块的设计

用SAA7111A设计模拟视频转换接口

基于视频解码芯片SAA7111A和FPGA实现实时视频采集系统的设计

基于视频解码芯片SAA7111A和FPGA实现实时视频采集系统的设计

评论