当一项创新颠覆了市场时,它便会得到市场的认可

网卡( NIC )自 20 世纪 80 年代便已出现,到本世纪初,许多公司开始投身该领域进行创新。他们最初的重点是高性能计算( HPC )。尽管业务都在以太网上运行,但是,最强大的 HPC 集群是使用 Myrinet 或 Infiniband 创建的。这些网络的网卡被设计为可以绕过操作系统( OS )内核,直接与 HPC 应用通信,从而显著提升性能。为了实现这一点,这些网卡在网络边缘应用了广泛的计算资源,使其能够从主机 CPU 上卸载常见通信任务。

这些HPC 网卡为后来的以太网网卡奠定了基础,后者内置内核旁路,适用于全球所有股票市场的电子交易。随着时间推移,这些平台进一步演进为 SmartNIC (智能网卡)或数据处理单元( DPU )。伴随超大规模用户( Hyperscaler )和云服务提供商( CSP )的出现,赛灵思发现了阻碍 SmartNIC 普及的三大因素:

1.可编程性

2.可组合性

3.可移植性

赛灵思提供了一种软件定义、硬件加速平台的方法,可以高效解决这三大问题。

可编程性.

过去十年里,人们做了各种尝试来为 SmartNIC 提供一个完全可编程的接口,但没有一种取得绝对成功。同时,该行业缺乏标准化语言和业经验证的软件开发及部署环境。几年前,赛灵思成为 P4 语言联盟的活跃成员,作为工业贡献者,开发了一种跨多类硬件管理网络数据包的语言。P4 语言迅速发展起来,如今大部分 SmartNIC 和 DPU 都将其用作默认编程语言。赛灵思全新 SN1000 SmartNIC 系列中所有独特的逻辑块都是用 P4 编写的。

可组合性

(滑动查看完整内容)

超大规模用户和 CSP 的第二个要求是可组合性。这是一种将新功能块动态插入到收发包处理流水线中的功能。这两条直接管理网络数据包的流水线构成了 SmartNIC 的数据平面。网卡上的第二个平面称为控制平面,作用是管理数据平面内的可编程块。如上所示,赛灵思充分利用了我们在可编程逻辑方面的领先优势,设计出一款完全可组合的网卡架构。

构成数据平面的收发流水线都有数个可编程入口点,客户可以在这些入口点上使用我们的 Vitis 软件开发平台连接其使用 P4、C/C++、HDL 或 HLS 编写的代码块。然后,Vitis 会将此代码编译成逻辑,帮助工程师在适当的数据包处理流水线中插入他们认为合适的模块。这可以让数据包以极快的速度通过数据平面,从而使赛灵思能够支持线速包处理。

其他未在其数据平面中使用可编程逻辑的供应商,必须在其 DPU 上部署大量典型的 CPU 核(通常为 Arm)来处理这些网络数据包。随着数据包速率攀升至每秒数亿个数据包,这种方法(使用 DPU 上的 CPU 核来处理数据平面上的数据包)将受到影响。我们的软件定义、硬件加速的方法将令赛灵思的 SN1000 系列明显优于竞争对手。

大型数据中心客户(如超大规模用户和 CSP)通常会要求供应商展示其产品路线图。该路线图将向客户展示供应商对其架构的承诺,以及在未来几代中推进该架构的计划。通常需要每一代都是新款芯片,在先前芯片的基础上有所改进。

可移植性

多年前,Solarflare 开始开发一种用 P4 编写的完全可移植的 SoftNIC 架构,本次成果最终被赛灵思收购。SoftNIC 是一种将所有核心 NIC 功能全部表示为代码的网卡,使得 NIC 可以在 FPGA硬件平台之间轻松移植。SoftNIC 利用直接存储器访问( DMA )引擎等标准硬件块与主机 CPU 进行通信,利用可以具有特定的芯片几何结构且通常使用了加密块的介质访问控制( MAC )块进行以太网通信。最终结果是,SoftNIC 的漏洞和新增功能无需创建新的芯片,客户只需安装软件更新即可。

构成 SN1000 可移植网卡架构的各种重要组件是 DMA 引擎、加密、MAC 块、虚拟化网卡 ( VNIC )和匹配操作引擎( MAE )的接口。VNIC 不仅是传统 OS 设备驱动程序查看网卡的方式,还可以处理校验和卸载及数据包控制。收发流水线中的 MAE 是处理虚拟网络请求的地方。在这里,Open vSwitch ( OvS )函数可用于管理主机上运行的虚拟机和容器的流量。MAE 可以显著减轻主机 CPU 处理 OS 或程序管理器网络调用的负担,有时会为 CSP 工作负载返回多达 30% 的主机 CPU 周期。MAE 的设计旨在轻松与 tc-flower 和 DPDK 通用流 API (rte_flow)进行连接,以便处理这些函数。插件入口点、VNIC、MAE 和 NET 引擎均是用软件编写并编译到逻辑门中。这就是赛灵思所谓的软件定义和硬件加速。

随着 SN1000 SmartNIC 的发布,赛灵思将提供几个可选的插件模块,在接下来的几个月还将提供更多模块。借助 SN1000,赛灵思展示了首个完全可组合且可移植的 SmartNIC,这是我们身处业届竞争最激烈的领域之一而带来的一项重大创新。

责任编辑:lq

-

cpu

+关注

关注

68文章

11326浏览量

225863 -

数据中心

+关注

关注

18文章

5762浏览量

75197 -

编程语言

+关注

关注

10文章

1965浏览量

39859

原文标题:解决三大痛点,加速SmartNIC普及

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

赛灵思FPGA电源解决方案全解析

FPGA硬件加速卡设计原理图:1-基于Xilinx XCKU115的半高PCIe x8 硬件加速卡 PCIe半高 XCKU115-3-FLVF1924-E芯片

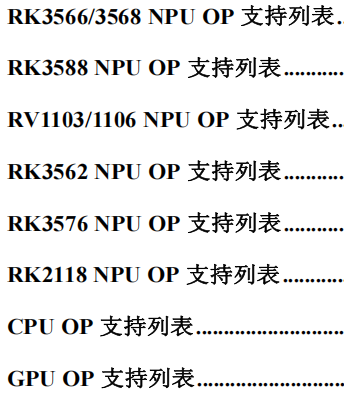

一文掌握瑞芯微RK系列NPU算子支持全景:覆盖6大平台,新增硬件加速算子,嵌入式AI开发不踩坑

复杂的软件算法硬件IP核的实现

常用硬件加速的方法

软硬件协同技术分享 - 任务划分 + 自定义指令集

硬件加速模块的时钟设计

有哪些方法可以确保硬件加速与通信协议的兼容性?

如何利用硬件加速提升通信协议的安全性?

易灵思与南京大学集成电路学院暑期课程圆满结课

大模型推理显存和计算量估计方法研究

推动硬件辅助验证平台增长的关键因素

赛灵思提供了一种软件定义、硬件加速平台的方法

赛灵思提供了一种软件定义、硬件加速平台的方法

评论