SSD盘的核心器件就是控制器芯片和NAND,控制器里面的很多中端或者后端算法也是围绕NAND进行优化的,所以,一般情况下每家控制器厂商或者SSD盘的厂商都有工程师或者团队负责研究或者测试NAND的相关特性,为解决围绕NAND相关的问题提供坚实的基础和技术支撑。

“工欲善其事,必先利其器”,由于主流NAND厂商目前都是国外公司,国内这块对于NAND特性非常精通的工程师资源并不是特别多,能够使用的研发/测试的工具也很少,但是如果需要解决围绕NAND的SSD问题,必须具备一款针对于NAND进行深入测试的工具。

NplusT是一家意大利公司,深耕Memory以及NAND测试将近20年,在这方便积累了大量的经验,NplusT开发的NanoCycler产品是一款非常灵活易用的NAND特性测试和分析工具,支持最新的1.6GT/s,非常适合国内高校/科研院所,SSD控制器和盘开发,以及针对SSD盘失效分析等应用场景。

该NAND分析工具已经广泛应用于欧洲,美国,以色列,台湾,日本,韩国和中国大陆的高校和公司,国内客户如:Huawei, Alibaba, SMIC中芯国际, Inspur浪潮, SCS山东华芯, Dputech大普, YeeStor得一, Tenafe特纳飞, 复旦大学, 清华大学, 南京大学, 山东大学, 等等;国际上使用NanoCycler的客户更多,例如:以PMC/MicroSemi/Microchip的企业级NVMe SSD控制器为代表,其NAND特性全部使用NplusT公司的产品进行测试和分析,包括业内知名的Synopsys, STMicro, Infinion, Cypress, Leti, Smart Modular, Mellanox等等知名公司的NAND分析部门,以及几大国际NAND厂商的客户解决方案部门或区域应用工程部门也在使用该设备进行一些应用测试。

解决NAND相关的SSD问题:

1. 较低的SSD性能和Crash和NAND的关系

2. QoS随着NAND老化下降导致的问题

3. SSD意外Crash问题

电压波动,突发电流冲击,时序分析

高性能power分析,长时间分析power峰值,平均,分布

4. 较高的初始RBER

5. 高速接口带来的挑战

1,033MT/s, 1,200MT/S, 1.6GT/s, 后续2.4GT/s

原文标题:如何解决SSD研发过程中和NAND相关的问题

文章出处:【微信公众号:ssdfans】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

芯片

+关注

关注

463文章

54436浏览量

469399 -

控制器

+关注

关注

114文章

17878浏览量

195150 -

SSD

+关注

关注

21文章

3150浏览量

122612

原文标题:如何解决SSD研发过程中和NAND相关的问题

文章出处:【微信号:SSDFans,微信公众号:SSDFans】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

使用ls - addsw命令创建了一个 dpsw,运行测试过程中数据包速率达到1.2Gbps时,dpsw不会遇到缓冲区丢弃如何解决?

CFE教您如何解决Pogo Pin充电过程中的间歇性断开问题

为什么在充电过程中HY2213-BB3A会特别特别烫,这应该如何解决?

晶圆制造过程中的掺杂技术

【开发指南】全志系列核心板开发过程中的常见问题及排查策略

开发者福音!明远智睿SSD2351核心板

芯片研发过程中的两种流片方式

采用第九代QLC NAND的美光2600 NVMe SSD介绍

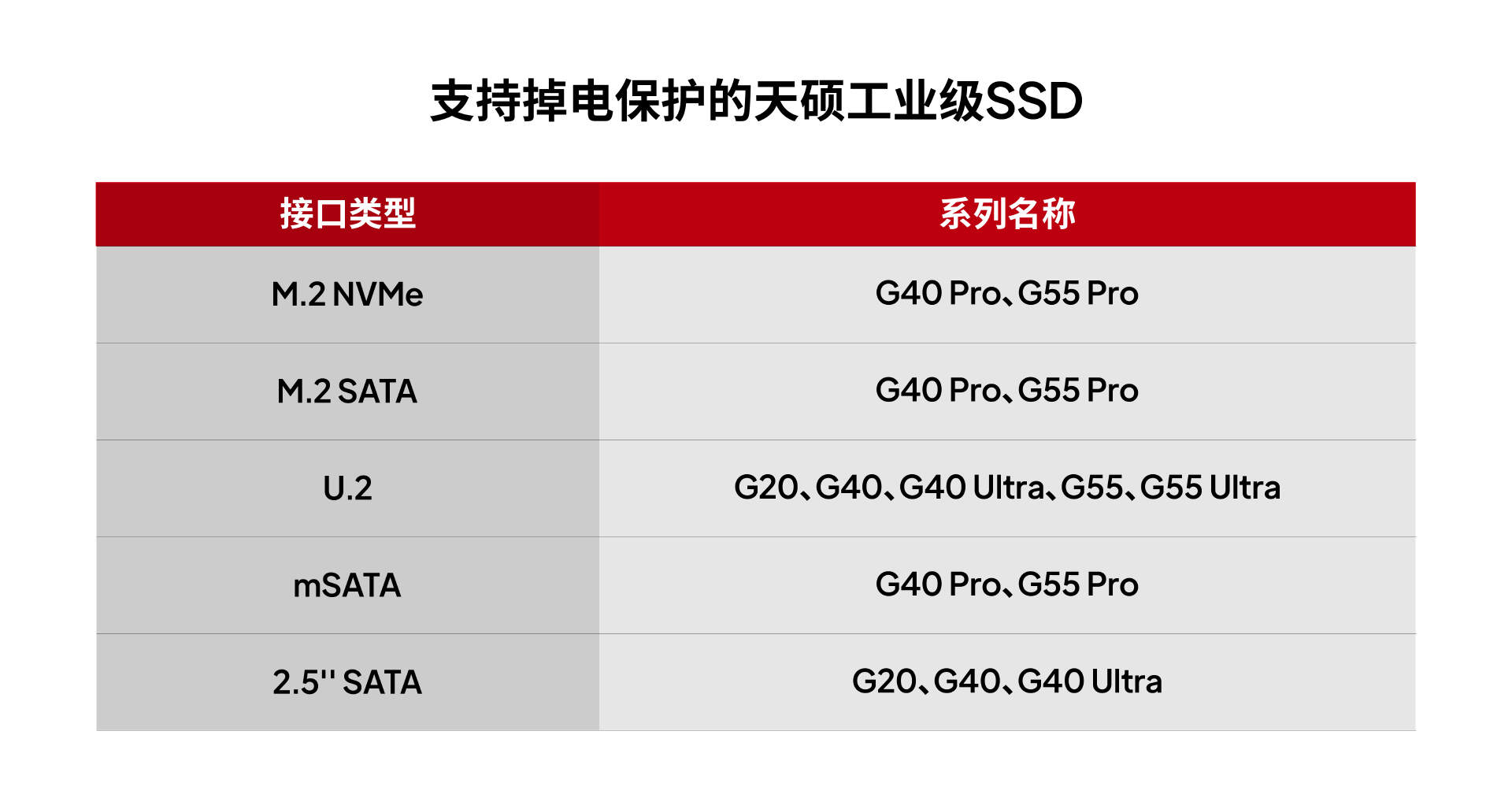

天硕工业级SSD固态硬盘能否避免数据丢失?

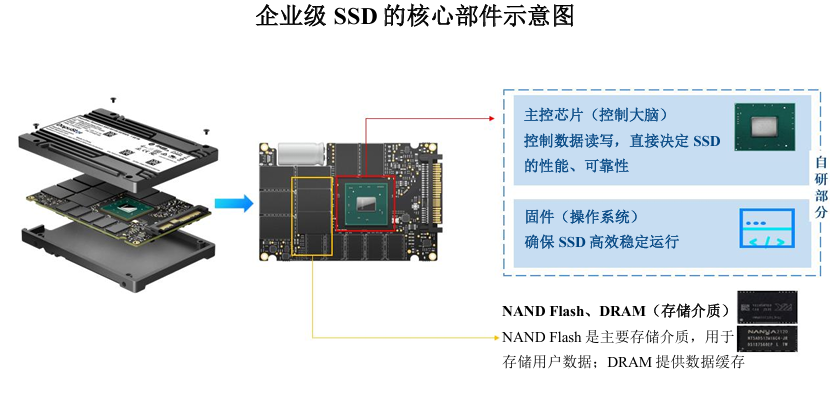

企业级SSD的核心技术与市场趋势

如何解决SSD研发过程中的NAND问题?

如何解决SSD研发过程中的NAND问题?

评论