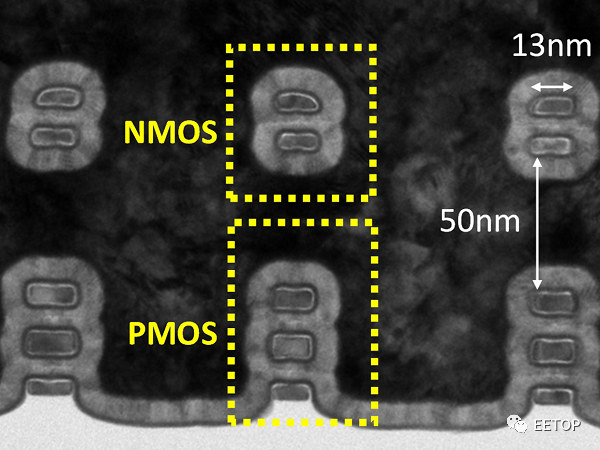

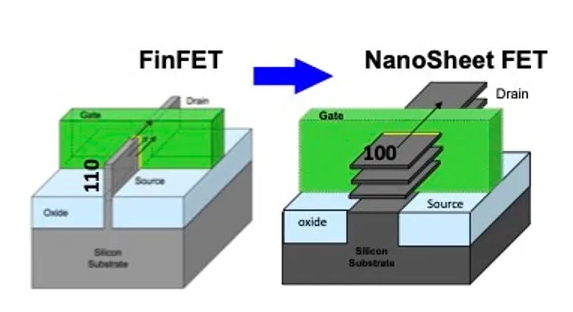

如今几乎所有数字元件背后的逻辑电路都依赖于两种成对的晶体管– NMOS 和PMOS。相同的电压信号会将其中一个晶体管打开,而将另一个关闭。将它们放在一起意味着只有发生些微变化时电流才会流通,进而大大降低了功耗。这些成对的晶体管已经彼此栉次鳞比在一起好几十年,但是如果电路要继续缩小,它们就必须靠得更近。 英特尔(Intel)在本周的IEEE 国际电子元件大会(IEEE International Electron Devices Meeting, IEDM)上展示全然不同的排列方式:把一对晶体管堆叠在另一对上面。该方案有效地将一个简单的CMOS 电路所占面积减半,这意味着未来IC 集成电路芯片上的晶体管密度可能会增加一倍。 该方案首先使用了被广泛认可的下一代晶体管结构,该结构有不同的称呼,包括纳米片(Nanosheet)、纳米带(Nanoribbon)、纳米线(Nanowire)或环绕式结构(Gate- All-Around, GAA)元件。和当前晶体管主要部分是由垂直硅鳍片组成之常见做法不同的是,英特尔纳米片的通道区是由多个相互堆叠之水平纳米级薄片组成。

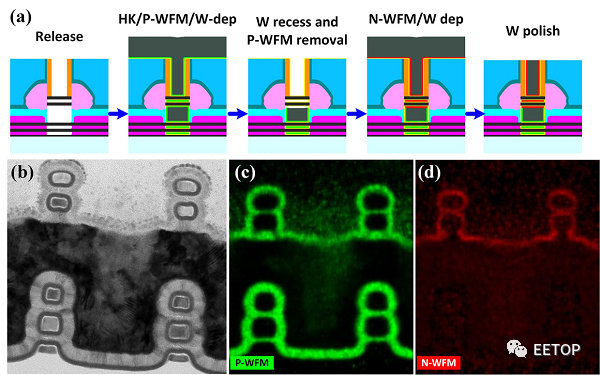

采用自我对准制程配方,修改制造步骤成为制程重点英特尔工程师使用这些元件来打造极简的CMOS 逻辑电路,亦即所谓反向器(Inverter)。它需要两个晶体管,两个电源接线,一个输入连线和一个输出连线。即使晶体管也采取像当前并排的放置方式,但排列得非常紧凑。透过堆叠晶体管并调整互连,反向器面积得以减半。 英特尔用于打造堆叠式纳米片的配方被称为「自我对准」(Self-Aligned)制程,因为其实质上可透过相同的步骤中构建两种元件。这很重要,因为多加第二步骤(比如,在个别的晶圆上构建他们,然后再将晶圆接合在一起)可能会导致晶圆定位偏移,进而造成任何潜在电路的破坏。 该制程的核心重点是对纳米片晶体管的制造步骤进行修改。它首先从重复的硅层和硅锗层开始。然后将其蚀刻成一个又高又窄的鳍片,然后再将硅锗蚀刻掉,留下一组悬浮的硅纳米片。通常,所有的纳米片都会形成单一的晶体管。但在此,最上面两个纳米片会连接到掺磷硅(Phosphorous-Doped Silicon)上,其目的为了形成一个NMOS 元件,而底部两个纳米片则连接到了掺硼硅锗(boron- doped silicon germanium)上,以产生PMOS。

简化整合流程,将应变引进自家元件中这整个「整合流程」当然要复杂得多,但是英特尔研究人员一直在努力使其尽可能地简单,英特尔资深研究员暨元件研究总监Robert Chau 表示。「整合流程不能太过复杂,因为这将影响到以堆叠式CMOS 制造芯片的可行性。结果证明这是一个非常实用的流程,并取得了可观的成果。」 他表示:「一旦掌握了这个诀窍,下一步就可以开始追求效能表现了。」这可能包括PMOS 元件的改进作业,目前它们在驱动电流方面落后NMOS。Chau 进一步指出,该问题的答案可能是要在晶体管通道中引进「应变」(Strain)。此一构想是透过快速通过载流子(Charge Carrier,在这种情况下为电洞)的这种方式来扭曲硅晶体晶格。英特尔早在2002年就将应变引进至自家元件中。

在IEDM 大会的另一项研究中,英特尔展示了一种能在纳米带晶体管中同时产生压缩应变(Compressive Strain)和拉伸应变(Tensile Strain)的方法。 其他研究组织也正展开堆叠式纳米片的设计研究,尽管有时将它们称为互补式场效晶体管(Complementary FET, CFET)。比利时研究组织Imec 率先提出了CFET 概念,并于去年6 月的IEEE超大型集成电路技术研讨会(VLSI Symposia)上发表了实作CFET 的研究报告。但是,Imec 元件并非完全由纳米片晶体管制作而成。其底层反而是由鳍式场效晶体管(FinFET)组成,顶层则为单一纳米片。中国台湾研究人员曾发表一篇有关CFET实作的研究报告,该结构上的PMOS 和NMOS 各有一片纳米片。相比之下,英特尔的电路在3 纳米之纳米片PMOS 上面有一个2 纳米之纳米片NMOS,这更接近当堆叠有必要时元件该有的样子。

原文标题:关注 | 让芯片密度再翻翻,摩尔定律再延续!英特尔展示堆叠式纳米片晶体管技术

文章出处:【微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

芯片

+关注

关注

447文章

47917浏览量

410017 -

英特尔

+关注

关注

60文章

9457浏览量

169080 -

晶体管

+关注

关注

77文章

9070浏览量

135382

原文标题:关注 | 让芯片密度再翻翻,摩尔定律再延续!英特尔展示堆叠式纳米片晶体管技术

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

英特尔CEO称公司全力押注18A制程

英特尔押注18A制程,力争重回技术领先地位

英特尔:2030年前实现单个封装内集成1万亿个晶体管

英特尔CEO基辛格:摩尔定律放缓,仍能制造万亿晶体

可性能翻倍的新型纳米片晶体管

英特尔展示下一代晶体管微缩技术突破,将用于未来制程节点

安装OpenVINO工具套件英特尔Distribution时出现错误的原因?

英特尔媒体加速器参考软件Linux版用户指南

未来的晶体管会是什么样?

英特尔展示堆叠式纳米片晶体管技术

英特尔展示堆叠式纳米片晶体管技术

评论