当像Jim Keller这样的人说您的公司“取得了令人瞩目的进步,并且拥有最有前途的架构”的时候,对你而言这将是莫大的荣誉。如果他还加入了你的公司,那么这种表扬就意味着两倍。

日前,Tenstorrent公司宣布,业内知名的计算架构师Jim Keller已加入公司,担任公司首席技术官兼总裁,并加入了公司董事会。

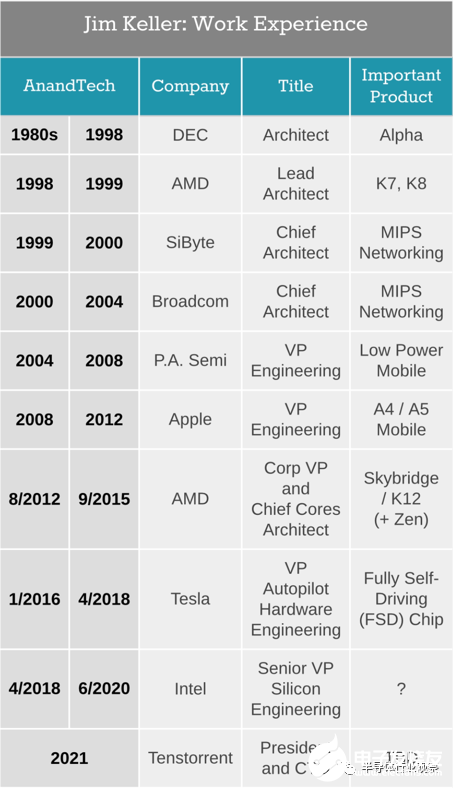

对于我们的普通读者来说,Jim Keller是计算机架构有方面的知名专家。他的职业生涯始于DEC,从事Alpha处理器的设计工作,随后在AMD工作了两年之久,致力于推出K7和K8。

Keller还在SiByte / Broadcom担任过首席架构师四年,为网络接口设计MIPS处理器,然后在PA Semi任职四年,然后在公司被Apple收购后还呆了四年,推动A4和A5的发布。

然后回到AMD工作两年,担任公司副总裁和首席核心架构师。负责新一代CPU架构K12和Zen。

随后,在特斯拉担任自动驾驶硬件工程副总裁两年,创建了完全自动驾驶芯片;然后在担任了硅谷工程集团的英特尔高级副总裁两年后离职。

自从离开英特尔以来,许多关键的行业分析师(以及我们自己)一直在猜测吉姆将去哪儿。他曾短暂出现埃里·马斯克(Elon Musk)于2020年8月发表的Neuralink演讲的观众中,同期到场的还有莱克斯·弗里德曼(Lex Fridman)。

日前,Tenstorrent告诉我们,Jim Keller将担任公司总裁兼首席技术官,同时还是其董事会成员。根据他先前的专业知识,Jim的角色似乎是在为该公司设计未来产品以及在Tenstorrent团队的基础上成功实现这一目标。

该公司首席执行官Ljubisa Bajic也确认Jim被任命为公司总裁兼CTO,他同时指出:

Tenstorrent的建立是基于这样一种信念,即以ML为中心的软件的不断转变需要对计算能力进行相应的转换。Jim Keller是计算机,文化和组织设计方面出色的领导者,没有其他人能够执行此构想。我很高兴与Jim一起工作,并为我们的合作伙伴关系释放出来的可能性而感到兴奋。

Tenstorrent是一家纯粹的无晶圆厂AI芯片设计和软件公司,这意味着他们创建和设计用于机器学习的芯片,然后使用代工厂制造硬件,然后与合作伙伴一起创建解决方案(例如,芯片+系统+软件+针对该客户的优化)。

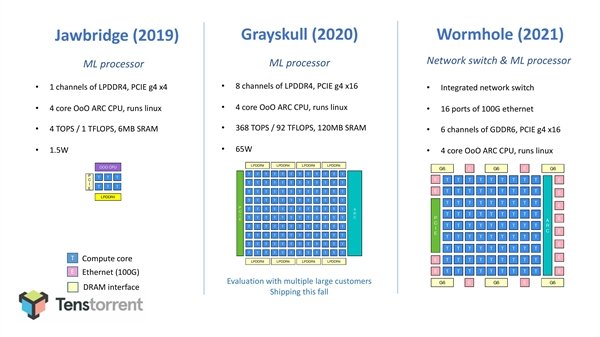

对于那些了解这一领域的人来说,这与市场上其他50家表现相同的公司。纯无晶圆厂AI芯片设计公司的典型分歧在于并无任何不同,Tenstorrent会同时进行训练和推理芯片研发,并且已经在研发其第三代处理器的过程中。

Tenstorrent成立于2016年,在多伦多和奥斯汀之间拥有约70名员工。

公司的关键成员都有芯片设计的背景:CEO曾领导AMD电源和性能架构团队,也曾负责过NVIDIA Tegra的系统架构设计;还有在AMD和Altera工作了16年的系统软件负责人,以及拥有来自神经网络的专业、Intel的网络加速器设计,AMD的GPU系统工程,ARM的Arm CPU验证负责人,AMD的IO虚拟化专业人士,英特尔的前神经网络编译器团队负责人以及AMD的前安全性和网络开发负责人。

由此看来,Jim会很合适,还有一些前同事在旁边工作。

Tenstorrent当前的产品是Grayskull,基于GF的12nm设计的处理器,该产品最初被设计为推理加速器和主机。它在2D双向网格中包含120个定制内核,并且仅65 W即可提供368 TeraOP的8位计算。120个定制内核中的每一个都有用于数据控制的数据包管理引擎,该数据包计算引擎包含Tenstorrent的定制TENSIX内核,以及五个用于非标准操作(例如条件接收)的RISC-V内核。

该芯片通过将矩阵运算优化为压缩数据包,从而通过图形编译器和数据包管理器对计算步骤进行流水线并行化,从而致力于稀疏张量运算。这还可以实现动态图形执行,与某些其他AI芯片模型相比,该信任允许异步进行计算和数据传输,而不是特定的计算/传输时域。

Grayskull目前正在向Tenstorrent的客户发货,但所有这些都尚未公开。

下一代芯片被称为Wormhole,它更注重训练而不是加速,并且还捆绑在16x100G以太网端口交换机中。从训练到加速的转变需要更快的内存接口,因此有6个GDDR6通道,而不是8个LPDDR4通道。

与讨论HBM集成的其他AI芯片相比,这似乎很低,但是Tenstorrent的计划似乎更适合于中端成本结构,而且比那些推动尖端技术的芯片以更高的效率提供机器学习计算。频率和过程节点(部分也将在产量中)。

那么,如果当前一代已经在销售,而下一代几乎已经准备就绪,那么Keller究竟适合什么地方呢?

在与首席执行官交谈时,他表示,Keller将与我们一起打造新颖有趣的东西。这似乎表明,考虑到Tenstorrent的压倒一切的Software 2.0策略(硬件,编译器和运行时提供了一种全栈方法来稀疏(密集)),考虑到Keller的愿景将针对2022/2023硬件——AI矩阵计算。

用Jim自己的话说:长期以来,软件2.0是计算创新的最大机会。要获得胜利需要对计算和底层软件进行全面的重新思考。Tenstorrent取得了令人瞩目的进步,并且凭借最有前途的架构,我们有望成为下一代计算巨头。

责任编辑:PSY

-

处理器

+关注

关注

68文章

20339浏览量

255316 -

AI

+关注

关注

91文章

41315浏览量

302689 -

架构

+关注

关注

1文章

537浏览量

26646

发布评论请先 登录

新思科技ImperasDV解决方案让RISC-V处理器验证效率翻倍

OrangePi RV2 深度技术评测:RISC-V AI融合架构的先行者

新思科技ARC-V处理器驱动RISC-V市场无限机遇

Banana Pi BPI-CM6 计算模块将 8 核 RISC-V 处理器带入 CM4 外形尺寸

重磅合作!Quintauris 联手 SiFive,加速 RISC-V 在嵌入式与 AI 领域落地

探索RISC-V在机器人领域的潜力

明晚开播 |开源芯片系列讲座第28期:高性能RISC-V微处理器芯片

睿思芯科携灵羽处理器亮相2025 RISC-V中国峰会

知合计算:RISC-V架构创新,阿基米德系列剑指高性能计算

英伟达:CUDA 已经开始移植到 RISC-V 架构上

直播预约 |开源芯片系列讲座第28期:高性能RISC-V微处理器芯片

Zen架构之父转战AI公司:投身RISC-V处理器

Zen架构之父转战AI公司:投身RISC-V处理器

评论