我知道返回电流将使用最接近信号轨迹的平面。那么你能否就这两个具体条件给我答案。

1)当我们说4层时,层1 2 3是信号层,连续地平面在第4层。对于所有3层信号,返回电流路径将位于第4平面上,因为没有其他平面。

2)现在对于第二种情况,4层叠加是信号地平面信号信号。假设第3层有信号迹线,但我也为第3层的某些区域(不完全)上的某些 vcc轨道注入了铜。然后,如果我在第4层绘制信号迹线,则返回电流将在第2层的地平面上或部分铜在第3层上注入,以便在部分铜浇注下通过痕迹并且不会在部分铜浇注下通过。

我希望我很清楚。

如果你发布一些照片会更清楚。另外:用于高速信号的PCB是什么?如果不是,请记住,返回电流(实际上是任何电流)始终遵循阻抗最小的路径。 -

对于直流和低频填充(《几MHz /》几百ns长的开关边沿,不用担心太多RF魔法),地平面将成为返回路径。进入VHF范围后,返回路径通常是阻抗最小的路径。如果您的VCC电源平面有很多陶瓷脱钩,然后返回电流将沿着最近的层流(即要么具有良好的电容耦合到地或者是地面)

@Sam我不知道怎么样。电容器对返回电流有影响,因为返回路径是一条巨大的道路而电容器位于引脚附近。我唯一知道关于dec的事情。帽。是他们有频率。因此,通过将它们中的一些并联连接,我们获得了低阻抗,并且它们提供了我们想要的更恒定的电压电平。

@Enric Blanco所以在这种情况下,由于连续接地可能具有最低阻抗,因此它将是我们的返回电流路径,因为任何层上的部分铜浇注不能具有比完全浇注的接地层更低的阻抗 -,但是如何到达每个平面(过孔)将对铜在平面上倾倒的阻抗产生更大的影响。良好的

陶瓷去耦电容非常接近于高频信号的短路,这就是为什么在频率范围的较高端它们可以允许返回电流在层之间通过。DC / LF可能会通过地平面,但是如果有接近的去耦电容,那么多频率的东西将希望保持尽可能接近信号走线,这样可以让HF通过运行更接近信号走线沿着VCC层,然后就可以了。如果没有任何东西在几兆频率上运行且没有任何东西产生低于100ns的切换边缘,那么我不担心。 - Sam 于2017年2月23日23:25

但是没有实际的接触。我的意思是,如果我们从源到接收器连接一条迹线,例如从mcu引脚到i2c传感器引脚,那么电磁场将完成这一操作,电流将沿着相同的路径返回但在平面上。实际上,在我看来,我们似乎并没有与任何地方进行物理连接。我很困惑:) -

因此,实际上总结阻抗地平面层堆叠等所有这些细节在高速或高频率时都很重要。我不需要在低频率下担心太多。mcu传感器等电路 -

电流将根据其阻抗分离所有可能的方式,因此最短且更导电的方式将获得更多电流,而不是更长且导电性更低。但是你可以考虑每个导线/通孔/连接器/等电阻和(通常是很小的)电容和电感的组合。然后你必须解决所得到的网络,以获得各处的电流和电压值。通常这并不重要,因为有一条宽的路径,几乎所有的电流都是这样的,并且在路径上存在如此小的阻抗,无论如何电压几乎为零。 -

你为什么关心返回电流?您是否关注辐射发射或信号完整性?或者是其他东西?在任何情况下,您应始终将最快边缘信号路由到紧邻连续平面的位置。如果飞机上有任何断裂,请不要在断裂处路由快速边缘信号。这适用于两种堆叠选择。时钟和任何具有快速上升和下降时间的信号应紧邻GND。如果将GND放在内部层上,则可以在GND旁边放置两个跟踪层。需要考虑的事情。

。我想尽可能多地学习。我可以再询问一件事,我理解如果gnd在内部有2层相邻但是如果我们有4层并且其中3个可以用于高速跟踪,其中第4个将是完整的gorund平面。堆叠就像信号接地信号信号

编辑:hfy

-

pcb

+关注

关注

4392文章

23750浏览量

421078 -

高频信号

+关注

关注

1文章

161浏览量

22604

发布评论请先 登录

从入门到精通:PCB设计必须遵守的5大核心原则

NRF54L15芯片开发安装路径对vscode不生效问题解析

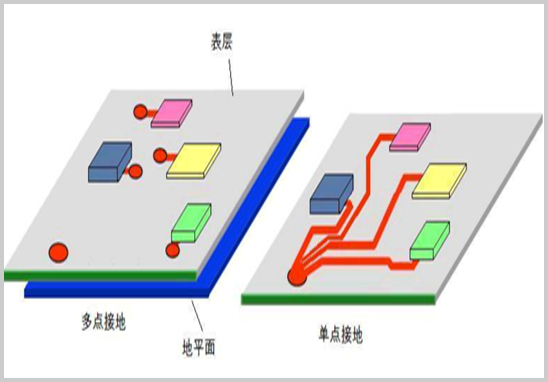

PCB设计中单点接地与多点接地的区别与设计要点

开关电源的PCB设计

技术资料—PCB设计规范

开关电源的输入电容的PCB设计技巧

SMT贴片前必知!PCB设计审查全攻

华为技术资料合集(硬件开发/C语言/PCB设计/天线通信)

【PCB】四层电路板的PCB设计

PCB设计全攻略:必备资料与详细流程解析

大功率PCB设计思路与技巧

PCB设计之电流路径返回问题解析

PCB设计之电流路径返回问题解析

评论