让我们来看看等长对我们信号质量的影响。

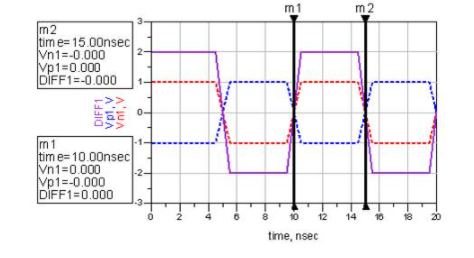

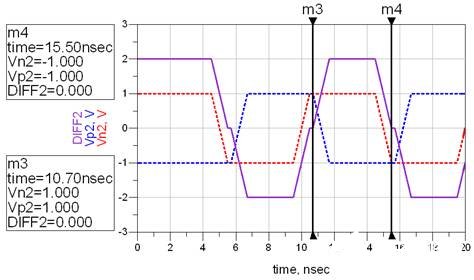

众所周知,SERDES信号都是由差分传输的,也就是说,两根信号线同时传输两个大小相等,方向相反的信号,接收端接收到的信号由两线相减得来。当两根线完全等长的时候,我们看到的波形应该是这样子的:

两次经过零轴的时间差为5ns,刚好是信号的一个UI。

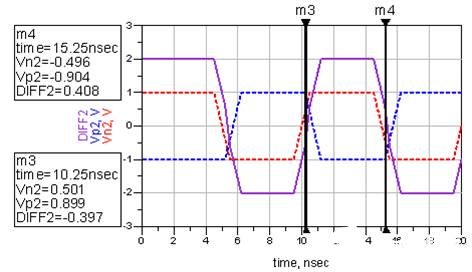

当两线不等长的时候,我们看到的波形是这个样子的:

上升沿明显变缓有木有。再将两个对比看看:

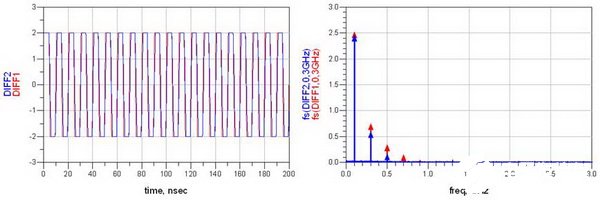

图中,蓝色的是N与P不等长的信号,可以看到,当两线不等长的时候,差分信号的能量明显变弱了,那多的能量去哪里了呢?

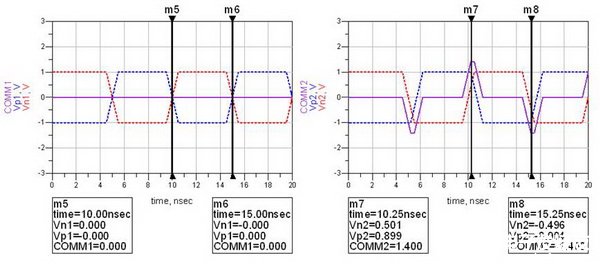

差分对之中除了差模能量之外还有共模能量,差模是N与P之间相减,共模是N与P之间相加。能量总是守恒的,多的能量变成了共模能量继续存在,图片:

如果两线的长度相差再大一些,我们接收端接收到的信号将会变成这样:

可以看到,两次经过零轴的时间由之前的5ns变成了4.8ns。或者说,N与P的长度差,引起了0.04UI的抖动。这时候,串行的Clock recovery该花点心思才能将其时钟解出来了。而且在进行时钟与数据对位的时候,是对在0V这个阶梯的左边还是对在右边呢?这又会引起时序问题的出现。

编辑:hfy

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

波形

+关注

关注

3文章

407浏览量

33199 -

SerDes

+关注

关注

8文章

236浏览量

36983 -

等长

+关注

关注

0文章

4浏览量

7700

发布评论请先 登录

相关推荐

热点推荐

一个等时不等长的DDR

高速先生原创文 | 刘为霞关于DDR的设计,经历过无数项目历练的攻城狮们,肯定是很得心应手的。对于信号质量方面的改善,相信大家应该已经有自己的独门技巧了。同组同层,容性负载补偿,加上拉电阻等等,总有

发表于 06-20 09:06

Altium Designer如何绕等长线

本帖最后由 山文丰 于 2020-7-14 14:32 编辑

1、为什么要等长,等长的重要性。在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有

发表于 07-14 14:30

用allegro使二条时钟线等长的设计置

为了使二个SDRAM的时钟线等长,设置等长的方法有很多,在这里我们只为了二条时钟线等长来学习如何通过设置约束规则然后通

发表于 06-21 11:57

•1981次阅读

一种频率估计的倍频等长信号加权融合算法

鉴于倍频等长信号具有重要研究价值,而其现有频率估计方法存在严重不足,提出一种新型加权融合算法。首先,根据倍频等长信号间频率的倍数生成倍频修正矩阵,对倍频等长信号频谱进行同频化处理,使之达到同频

发表于 03-05 11:48

•49次下载

Allegro中关于绕等长的自动功能

有了单线的自动等长,那就肯定不会放过板上随处可见的差分了,看大招——Auto-interactive Phase Tune。现在板子的速率越来越高,板上的差分线也就跟着越来越多,对内等长的工作量自然就加大了。但是自从

三个步骤,PCB设计信号等长分析

但是我们做设计时有时发现DDR器件等长没有做,其成品也可正常运行,并没产生影响,原因一般是系统软件对此信号做了延时处理,软件上做了时序控制。对于带状线来说,每1ps延时对应的走线长度是6mil左右,所以一般

PCB设计做等长走线的目的是什么

在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。 由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高

关于一个一个等时不等长的DDR设计

关于DDR的设计,经历过无数项目历练的攻城狮们,肯定是很得心应手的。对于信号质量方面的改善,相信大家应该已经有自己的独门技巧了。同组同层,容性负载补偿,加上拉电阻等等,总有一款适合你的DDR。但是

差分信号等长及阻抗匹配

在高速PCB中,为实现差分信号等长,且差分对每条线阻抗连续,有时候我们需要对单差分对做特殊调整。 对它的绕线进行补偿,但是这种补偿,需要依据仿真分析结果对差分对进行调整,仿真结果提供给PCB设计师做

AD设计DDR3时等长设计技巧

本文讲述了使用Altium designer设计SOC和DDR等高速PCB时候,如何设计信号线等长。DDR信号线分成两大部分。一是数据线部分,二是地址线、控制信号线部分。本

发表于 07-28 16:33

•5次下载

AD设计DDR3时等长设计技巧

本文紧接着前一个文档《AD设计DDR3时等长设计技巧-数据线等长 》。本文着重讲解DDR地址线、控制信号线等长设计,因为地址线、控制信号线

发表于 07-29 16:14

•3次下载

等长对我们信号质量有什么影响?

等长对我们信号质量有什么影响?

评论