在附件中是如何设置等长线的规则指导,因为经常性的会忘记,所以经撰写下来,以供自己和他人参考,避免不必要的时间浪费在查找资料上。

2020-08-10 12:35:58

各位大侠,Allegro16.6 T等长是如何设置的呢,请帮帮忙啦~~~~

2016-02-29 08:22:15

allegro中 ddr等长设置及绕线的步骤

2015-12-28 22:01:11

个人小结,希望能对那些还不会用allegro设置等长规则的朋友有点作用。也欢迎同行交流。

2013-12-26 15:53:24

我需要画1条50欧姆的特性阻抗线(射频模块到SMA天线),不知道allegro中的详细操作步骤?请哪位赐教一下,谢谢

2015-03-04 10:50:33

/1bpr4Edh 密码:eb61完整的整个视频主要讲解内容:一.allegro软件常用菜单介绍二.简单电路fanout1.走线和打孔2.IC及简单电路的fanout3.移动、拷贝、及修改的灵活运用4.fanout

2016-06-21 15:18:02

用AD15正常走线再贴线是没有问题的,但是当绕完等长再贴线时所绕部分会重复,总长变长。目前解决办法是贴完线再一根根在所绕部分再重新Layout一下,请问各路大神有没有遇到此问题并且有更好地解决办法?

2018-09-03 11:13:04

我的AD9446的工作在LVDS模式下,请问对于AD9446(100MHz),LVDS信号线的PCB走线的差分对间等长有没有要求?(PS:16对差分线,都做等长好复杂)谢谢!

2023-12-18 06:26:51

Class会增加一个 New Class,在该网络组上右键,修改一个你想要的名字,如:SDRAM 等。单击打开它,将需要等长的网络,从左边选取并添加到右边的窗口中。然后再点击 关闭设置。二. 布线在布

2013-01-12 15:18:43

采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在 PCB 上的传输延迟的差异。至于 USB/SATA/PCIE 等串行信号,并没有上述并行总线的时钟

2020-07-14 14:30:31

AltiumDesigner等长布线操作 我为大家介绍 等长布线,”等长走线“简单的理解就是让指定网络的走线”长度“一样。等长走线的主要目的是为了补偿同一组时序相关的信号线中延时较小的走线,尽量减小

2018-03-09 09:54:43

C6000的CPU执行指令是流水线方式的,每个时钟可以同时执行8个指令,这样一来,不会产生冲突吗?比如第一条指令,赋值给一个寄存器;第二条指令,读取这个寄存器的值;如果并行,这样的话,第二条指令怎么能读到第一条指令赋给寄存器的值呢??用C或者汇编编写程序时,要不要考虑这种冲突呢?谢谢您的回答

2019-01-15 10:27:23

本章教程主要在SPI单工通信方式下进行1条时钟线和1条双向数据线配置,并进行主机发送从机接收。 1、SPI简介及相关函数介绍SPI支持以三线同步串行模式进行数据交互,加上片选线支持硬件切换主从模式

2023-04-25 16:47:06

本章教程主要在SPI单工通信方式下进行1条时钟线和1条双向数据线配置,并进行主机接收从机发送。 1、SPI简介及相关函数介绍关于SPI单工通信模式下1条时钟线和1条双向数据线配置介绍,在第46章已经

2023-04-25 16:48:14

本章教程主要在SPI单工通信方式下进行1条时钟线和1条单向数据线配置,并进行主机接收从机发送。 1、SPI简介及相关函数介绍关于SPI单工通信模式下1条时钟线和1条单向数据线配置介绍,在第46章已经

2023-04-25 16:50:41

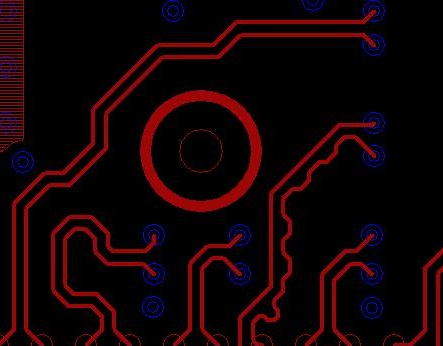

`如附图所示的多个DDR2地址线走线等长大家是怎么做的(用pads),大家有什么好的方法吗?共享一下,谢谢!`

2013-08-05 11:09:23

我正在使用 altium designer 设计一块FPGA、DDR的板子。有一些疑惑,在绕等长线时,有一些线有过孔有一些线没过孔,我发现穿过孔的距离并没有被计算在线长中。那过孔岂不是会造成很大

2015-06-18 17:14:35

本帖最后由 宋一锋 于 2016-11-25 17:53 编辑

PADS等长走线教程

2016-11-18 15:06:20

PADS等长走线教程

2013-04-27 23:34:35

PADS等长走线教程

2014-11-25 01:10:28

`各们老师们,如何设置差分等长自动走曲形线,而不是蛇形线。在长度约束里我设置数量也是最小了还是没有像这样的曲形线,是不是PADS没有这个功能,请各们老师们帮小弟解答一下。`

2019-06-10 10:23:30

电阻RS值为O~33 Ω,并联匹配电阻RT值应该在25~68 Ω。本组内的信号不要和数据信号组在同一个电阻排内。控制信号组:控制信号组的信号最少,只有时钟使能和片选两种信号。仍需要有一个完整的地平面和电源

2017-10-16 15:30:56

号的等长约束一般都比较严格,基本会要求在等长正负50mil以内甚至更小。经常看到的还有内存颗粒的等长要求。有些约束说DDR2的等长要求数据线时钟线等长控制在正负50mil,地址线等长控制在正负

2014-12-01 11:00:33

SDRAM要跑143M ,那SDRAM走线 有哪些要求?数据线等长,地址线等长 ,时钟线长度各有什么要求?

2015-01-29 15:09:21

请问各位大佬:TF数据线和时钟线等长,这种情况如何处理有一根数据线较长,这时还是以时钟线长度为基准吗

2019-03-19 07:35:02

画一组等长线,某些线的等长进度条骗了我。以为达到设定的长度会停下来,可是还是超出了好多。怎么设定让他严格等长

2014-12-31 11:27:41

;数字键2增大绕线拐角幅度;数字键3减小绕线Gap间距;数字键4增大绕线Gap间距;Shift+a可以直接在走线模式下绕点对点等长Ctrl+鼠标中键可以查看网络长度原创文章,转载请注明: 转载自 allegro小北PCB设计

2018-08-04 13:03:03

pcb editor里面调地址等长线的时候右下角出现的提示条是什么意思?有红色的绿色的?

2015-07-27 17:32:49

CB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟线

2019-05-22 02:48:05

protel 中两个焊盘之间用多条导线连接要怎么设置? 只要我第二条一连上第一条导线就会消失 。这可以设置吗?

2012-09-03 11:25:03

想用一个串口收发两条指令 。先发一条指令 ,回数。判断回数正确在发另一条指令 ,回第二条回数。采用堆栈结构。堆栈0:堆栈1:运行后buffer显示:我希望是buffer2 中回第二条发数指令+第二条

2015-06-13 10:16:17

请教一下。我画等长差分线。这一条想走蛇形线。但是点不动。。

2019-08-08 05:35:18

1、时钟线等长概念 在一块主板上,从北桥芯片到CPU、内存、AGP插槽的距离应该相等,主板设计的基本要求,即所谓的“时钟线等长”概念。作为CPU与内存连接桥梁的北桥芯片,在布局上是很有讲究的。例如

2018-08-30 10:14:47

刚学ALLEGRO,一直搞不懂差分对设置等长跟阻抗匹配的关系,不知附图那样设置对不对,求指点

2014-11-30 22:41:22

我在画一原理图,将Flash连在两个接口上,想让Flash到两个接口都等长,而因为属于同一网络节点,结果弄成了一条线等长,求指导啊

2013-01-15 15:59:40

、等长 (7)不要驱动其他时钟二、布线 (1)时钟晶振:时钟线先经过负载电容,再到达晶振,周围打孔,GND屏蔽 (2)同源时钟:时钟线的并联匹配电阻靠近负载芯片,串联电阻靠近时钟芯片或者CPU

2019-05-21 09:34:14

如何将RXD与TXD俩条线经过转化后用一条线代替

2013-01-25 10:53:40

有一种新概念使您能够只用两条引线进行4线电阻测量为什么使用4条线测量电阻?2x4线电阻测量是怎样的?哪种万用表适合您?

2021-04-09 06:34:22

各位大侠:想请问下,如何在Protel ***中设置手工不同网络之间的等长走线,越详细越好!谢谢!

2012-09-15 22:44:01

文|原创:卧龙会 不安分的馒头相信很多LAYOUT 工程师都听说过高端产品用ALLEGRO,低端产品用AD的说法吧。当然这种说法也不是完全错误,这个就见仁见智吧。毕竟ALLEGRO在高速布线方面确实

2018-01-12 17:09:48

在ALLEGRO中设置好T型接点后,如下图所示据我的理解,ALLEGRO中T型接点等长设置的是图中BC和BD两断走线的等长,对吧??那如何设置AB走线的等长??

2017-07-07 17:55:14

画等长线的时候,两根线的差距差了200MM,并且线的密集程度较大,怎么处理?另外 AD中的xSignals怎么用的,有啥用

2019-07-12 18:01:52

线没有按规则走线这里我知道,这是为了达到等长的要求才这样处理的,如果两条线完全等距就没法满足等长要求了。4、另外我最想问的就是关于数据线、地址线、时钟线的等长关系,数据线是组内等长他和时钟线地址线没有

2012-10-29 16:14:50

我用PROTEL99SE画好了原理图,开始进行PCB布线,我想将图示左边的二条垂直相交的线在交点处画2条斜线,结果它自动将本来是一条线分成二段并与斜线组成二条新线,而我在旁边没有节点处这样画又可以实现的意图,请问是哪里设置关闭自动合并操作。

2013-12-25 23:16:05

AD转换芯片数字输出A0-A11这12根数据线与FPGA连接时要做等长吗?

AD转换芯片时钟为70MHz,如果不需要,那么时钟速率达到多少需要做等长,就是画蛇形线!

2023-12-12 08:15:53

AD转换芯片数字输出A0-A11这12根数据线与FPGA连接时要做等长吗?AD转换芯片时钟为70MHz,如果不需要,那么时钟速率达到多少需要做等长,就是画蛇形线!

2019-01-21 15:55:14

DDR3的数据线等长是怎么设置长度的

2019-07-17 04:47:35

跪求Altium designer中单线等长和差分等长以及保持原间距走线和等间距走线是怎么使用的,请求高人指点,谢谢!

2019-09-25 05:35:17

等长线画好之后 白色飞线如何删除

2019-08-28 04:32:34

除了 I2C1 引脚 35 和 36 之外,CMWX1ZZABZ 中是否还有第二条 I2C 总线?我宁愿使用第二个 I2C 而不是添加 MUX 来连接所有传感器。

2022-12-15 07:03:55

在MCU和SRAM连接的数据线和地址线是分别做等长(就是数据线一组自己做等长,地址线一组做等长),还是数据线和地址地址线一起做等长?另外那些SRAM的片选信号线等控制线需要做等长吗?是自己等长还是和数据线地址线一起?SRAM布线是对走线的长度有没有限制?

2019-09-19 23:25:09

请问一下allegro如何使二条时钟线等长?

2021-04-25 08:47:46

有个项目很纠结,希望大家帮忙解答下:用的芯片主要有一块DSP芯片,一块DDR2芯片,一块FLASH芯片等,在走线的时候这3个芯片之间的数据线,地址线需不需要等长走线?

2019-09-26 05:38:04

差分线何时要考虑线的等长?如果要考虑使用等长线的话,两根信号线之间的长度之差最大不能超过多少?如何计算?

2019-05-20 05:35:12

用AD16画等长时 ,地址线已经都连接上了,但是显示长度都为0,怎么解决呢?

2019-06-11 05:35:35

如果我把DDR的数据线的高8位分为一组,低8位分为一组,组内等长,这两组线的长度是不是要一样长?然后我把地址线,控制线,时钟线分为一组等长,地址线,控制线,时钟线的长度是不是要与数据线的长度一样长,还是怎么样???

2019-06-14 05:35:21

范围,而不是等长。又因为飞行时间的最小时序要求一般都可以满足,也就是第二个公式在很多场合可以忽略不计,带给PCB设计的要求就是符合第一个公式,结论就是走线越短越好。任何因为并不存在时序要求而做的整个总线绕等长,而又为了绕等长而导致这个总线的布线度增加,串扰增加,这样的设计是错误的,失败的例子非常多。

2014-10-21 09:35:50

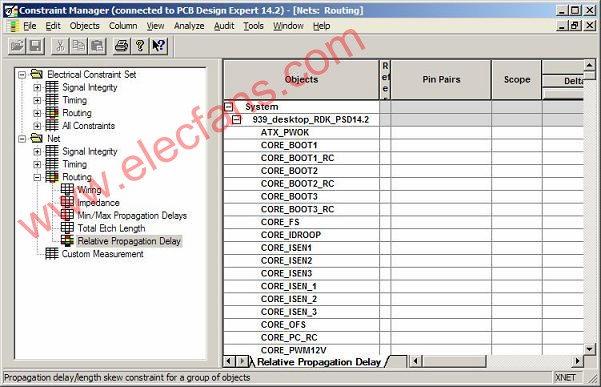

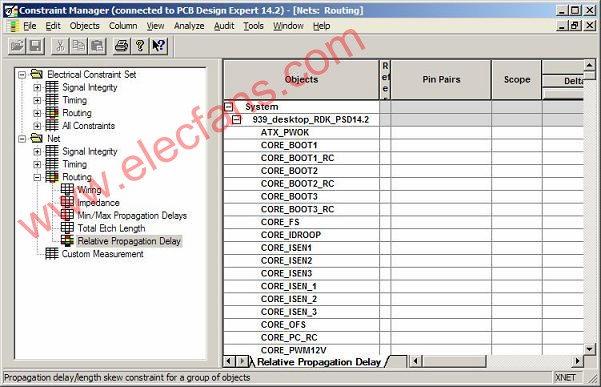

对于简单走线等长在以前文档中都有涉及这里不再复述了,下面内容将给大家介绍一下有关Xnet等长的设置问题, 如现在主板DD

2010-06-28 09:38:18 27423

27423

allegro_差分线等长设置,有需要的下来看看

2016-02-22 16:15:35 62

62 第一步:连接好需要绕等长的线,

第二步: T+R T+R开始绕等长, TABTAB 键调出等长属性设置框

第三步:滑动走蛇形线即可;

2016-09-12 16:13:30 0

0 有了单线的自动等长,那就肯定不会放过板上随处可见的差分了,看大招——Auto-interactive Phase Tune。现在板子的速率越来越高,板上的差分线也就跟着越来越多,对内等长的工作量自然就加大了。但是自从有了绕线新功能,就再也不担心绕等长费时多啦。步骤和单线绕等长一样,简单明了。

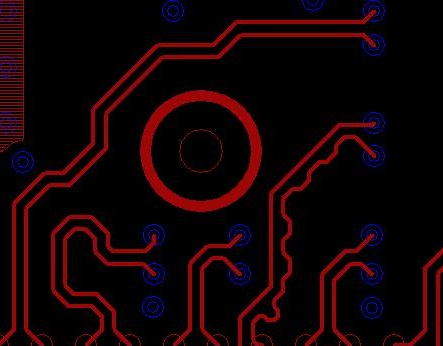

2018-10-19 15:33:40 26240

26240 经常画高速板的同学都知道,10个高速板有9个要绕等长,而且内存出现的频率尤其频繁,整的现在画板子不绕两下都有点不习惯。好在上期给大家介绍了几种快的不能再快的绕等长的方法,用allegro绕等长还是非常任性的。看看下图,多么漂亮,整齐,干净,密密麻麻绕的像一根根肠子似的等长线。

2018-11-11 10:55:36 4915

4915 本文档的主要内容详细介绍的是Allegro PCB设计时等长设置的一些方法与技巧解析。以DDR3(4pcs,fly-by 结构)为例,讲述一下在allegro 中如何添加电气约束(时序等长)。

2018-11-27 16:02:57 0

0 至于 USB/SATA/PCIE 等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方将时钟包含在数据中发出,数据接收方通过接收到的数据恢复出时钟信号。这类串行总线没有

2018-11-29 15:34:27 4989

4989 等长走线的目的就是为了尽可能的减少所有相关信号在 PCB 上的传输延迟的差异。至于 USB/SATA/PCIE 等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方将时钟

2019-04-26 15:27:25 10423

10423

本例中需要实现PCI-e金手指到EMMC芯片等长,包括D0-D7,CLK,CMD这10条网络。查看各条网络,确认是否存在串联匹配电阻。本例中,仅在时钟线上存在,如下图的高亮器件。

2019-06-22 09:44:22 8172

8172

在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。 由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高

2020-09-27 14:08:18 2505

2505

在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。 由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高

2020-10-24 09:29:38 8604

8604 在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至 4 次,而随着芯片运行

2020-11-22 11:54:17 18394

18394 Allegro的全称是CadenceAllegroPCBDesigner,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度

2022-05-13 09:28:25 1797

1797

Allegro(AiDT)自动等长介绍

2022-12-30 09:19:41 3

3

打开约束管理器,在

打开约束管理器,在

电子发烧友App

电子发烧友App

评论