1、前言

磁珠的全称为铁氧体磁珠滤波器(另有一种是非晶合金磁性材料制作的磁珠),是一种抗干扰元件,滤除高频噪声效果显著。

磁珠的主要原料为铁氧体。铁氧体是一种立方晶格结构的亚铁磁性材料,铁氧体材料为铁镁合金或铁镍合金,它的制造工艺和机械性能与陶瓷相似,颜色为灰黑色。

二、磁珠基础知识

磁珠(Ferritebead)有很高的电阻率和磁导率,其等效电路是一个DCR电阻串联一个电感并联一个电容和一个电阻。DCR是一个恒定值,但后面三个元件都是频率的函数,也就是说它们的感抗,容抗和阻抗会随着频率的变化而变化,当然它们阻值,感值和容值都非常小。磁珠比普通的电感有更好的高频滤波特性,在高频时呈现阻性,所以能在相当宽的频率范围内保持较高的阻抗,从而提高调频滤波效果。磁珠的电路符号就是电感,但是型号上可以看出使用的是磁珠。在电路功能上,磁珠和电感是原理相同的,只是频率特性不同而已。

从等效电路中可以看到,当频率低于fL(LC谐振频率)时,磁珠呈现电感特性;当频率等于fL时,磁珠是一个纯电阻,此时磁珠的阻抗(impedance)最大;当频率高于谐振频率点fL时,磁珠则呈现电容特性。EMI选用磁珠的原则就是磁珠的阻抗在EMI噪声频率处最大。比如如果EMI噪声的最大值在200MHz,那你选择的时候就要看磁珠的特性曲线,其阻抗的最大值应该在200MHz左右。

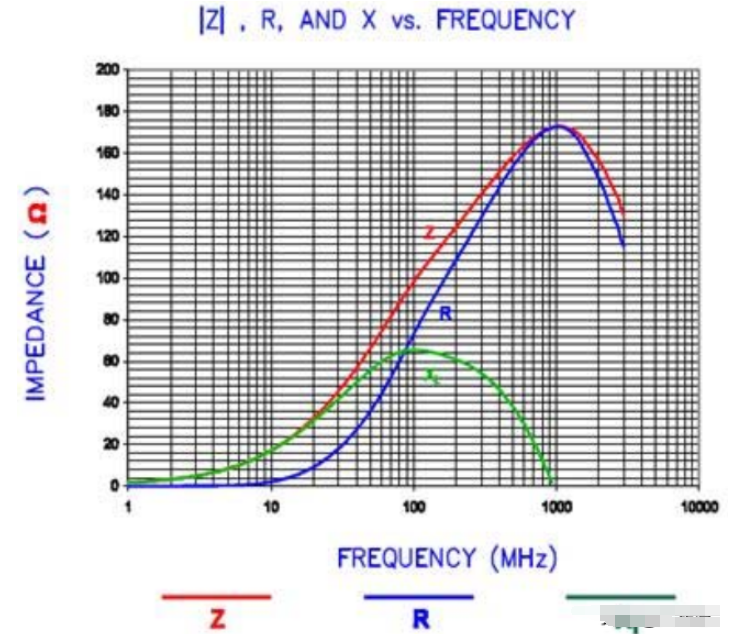

下图是一个磁珠的实际的特性曲线图。大家可以看到这个磁珠的峰值点出现在1GHz左右,在峰点时,阻抗(Z)曲线的值与电阻(R)的相等。也就是说这个磁珠在1GHz时,是个纯电阻,而且阻抗值最大。

Z:impedanceR:R(f)X1:L\C前面简单介绍了EMI磁珠的基本特性曲线。从磁珠的阻抗曲线来看,其实它的特性就是可以用来做高频信号滤波器。需要注意的是,通常大家看到的厂家提供的磁珠阻抗曲线,都是在无偏置电流情况下测试得到的曲线。但大部分磁珠通常被放在电源线线上用来滤除电源的EMI噪声。在有偏置电流的情况下,磁珠的特性会发生一些变化。

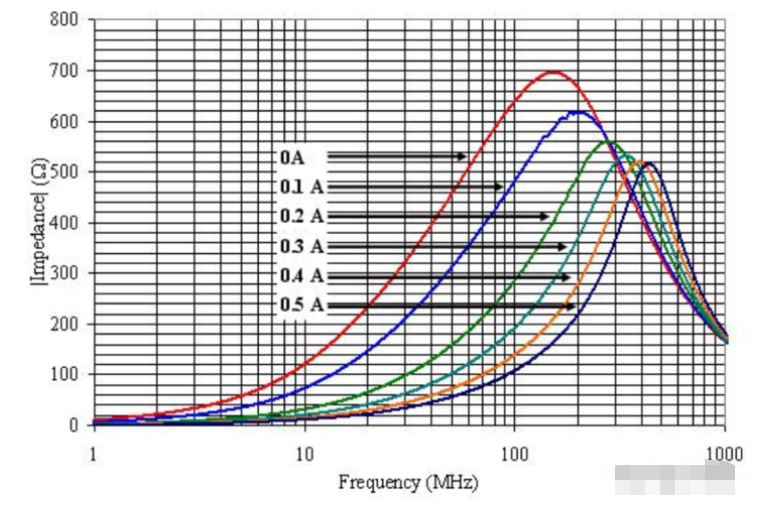

下面是某个0805尺寸500mA的磁珠在不同的偏置电流下的阻抗曲线。大家可以看到,随着电流的增加,磁珠的峰值阻抗会变小,同时阻抗峰值点的频率也会变高。

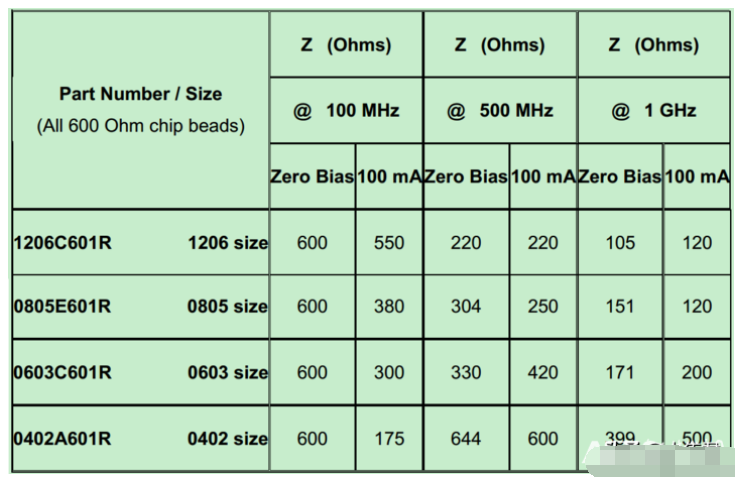

在进一步阐述磁珠的特性之前,让我们先来看一下磁珠的主要特性指标的定义:Z(阻抗,impedanceohm):磁珠等下电路中所有元件的阻抗之和,它是频率的函数。通常大家都用磁珠在100MHz时的阻抗值作为磁珠阻抗值。DCR(ohm):磁珠导体的的直流电阻。额定电流:当磁珠安装于印刷线路板并加入恒定电流,自身温升由室温上升40C时的电流值。那么EMI磁珠的磁珠有成千上万种,阻抗曲线也各不相同,我们应该如何根据我们的实际应用选择合适的磁珠呢?让我们首先来看一下阻抗值同为600ohm@100MHz,但尺寸大小不同的磁珠在不同偏置电流电流和工作频率下的特性。

上面是四个不同大小的磁珠分别工作在0A,100mA偏置电流及在100MHz,500MHz和1GHz工作频率下的阻抗值。

从上表的测试数据中可以看出,1206尺寸的磁珠在低频100MHz工作时,其阻抗值仅从0A下的600ohm减小到100mA偏置电流下的550ohm,而0402尺寸的磁珠阻抗值却从0A下的600ohm大幅减小为175ohm。

由此看来,在低频大偏置电流应用的情况下,应该选择大尺寸的磁珠,其阻抗特性会更好一些。让我们来看一下磁珠在高频工作时的情形。1206尺寸的磁珠其1GHz下的阻抗从100MHz下的600ohm大幅减小为105ohm,而0402尺寸的磁珠其1GHz下的阻抗则只由100MHz下的600ohm小幅减小为399ohm。

这也就是说,在低频大偏置电流的情况下,我们应该选择较大尺寸的磁珠,而在高频应用中,我们应该尽量选择小尺寸的磁珠。

三、应用于信号线上的磁珠

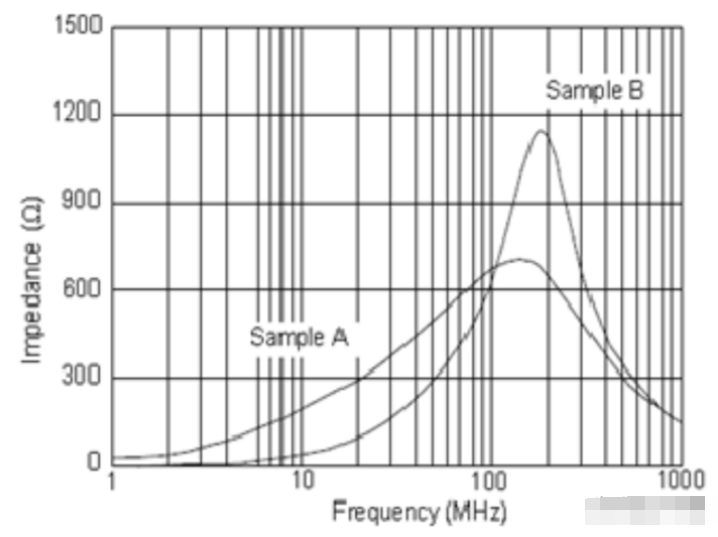

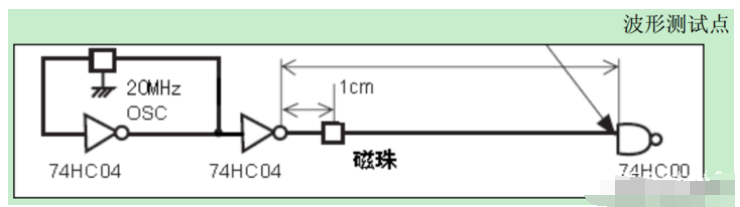

让我们再来看一下下面两个不同曲线特征的磁珠A和磁珠B应用于信号线时的情况。

磁珠A和磁珠B的阻抗峰值都在100MHz和200MHz之间,但磁珠A阻抗频率曲线比较平坦,磁珠B则比较陡峭。我们将两个磁珠分别放在如下的20MHz的信号线上,看看对信号输出会产生什么样的影响。

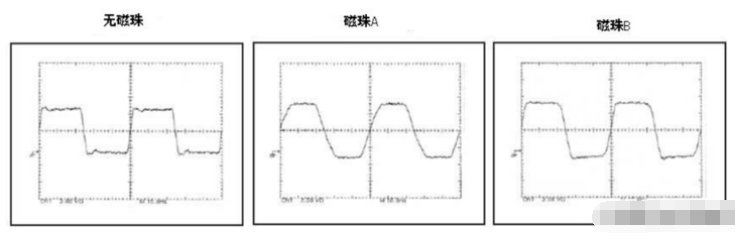

下面是用示波器分别量测磁珠输出端的波形图

从输出波形来看,磁珠B的输出波形失真要明显小于磁珠A。原因是磁珠B的阻抗频率波形比较陡峭,其阻抗在200MHz时较高,只对200MHz附近的信号的衰减较大,但对频谱很宽的方波波形影响较小。而磁珠A的阻抗频率特性比较平坦,其对信号的衰减频谱也比较宽,因此对方波的波形影响也较大。

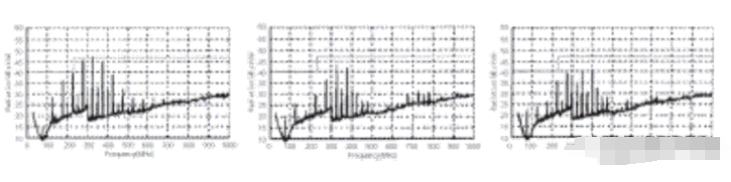

下面是上述三种情况对应的EMI测试结果。结果是磁珠A和磁珠B都会对EMI噪声产生很大的衰减。磁珠A在整个EMI频谱范围内的衰减要稍好于磁珠B。

因此,在具体选用磁珠时,阻抗频率特性平坦型的磁珠A比较适合应用于电源线,而频率特性比较陡峭的磁珠B则较适合应用于信号线。磁珠B在应用于信号线时,可以在尽量保持信号完整性的情况下,尽可能只对EMI频率附近的噪声产生最大的衰减。

四、磁珠与电容回路

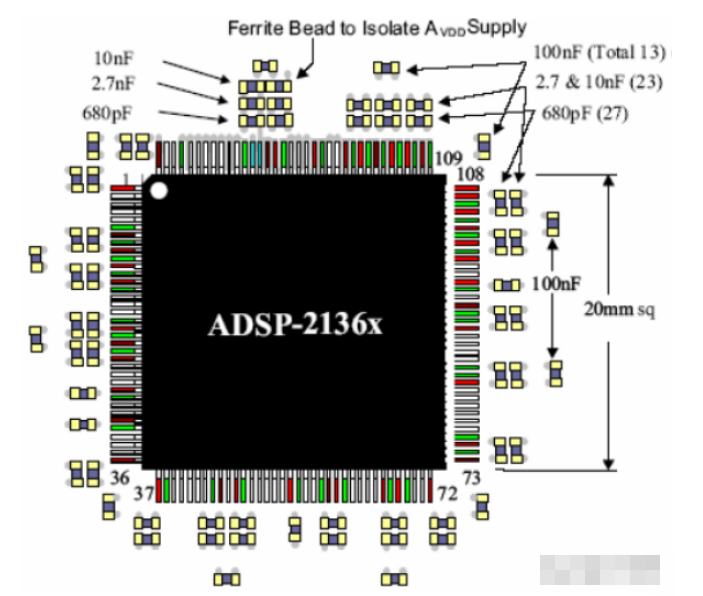

在一些器件的数据手册或者应用文档中,一般会建议对一些要求较高的电源管脚(比如VCCA,VCCPLL之类的)做隔离处理,并推荐使用磁珠进行隔离。

一般建议将电容放在更加靠近器件电源管脚的地方(相对于磁珠的位置),如下图所示。至于电容的容值,和该电源管脚的功率(电压&电流),电容距离管脚的位置,电容的封装大小等因素有关系。

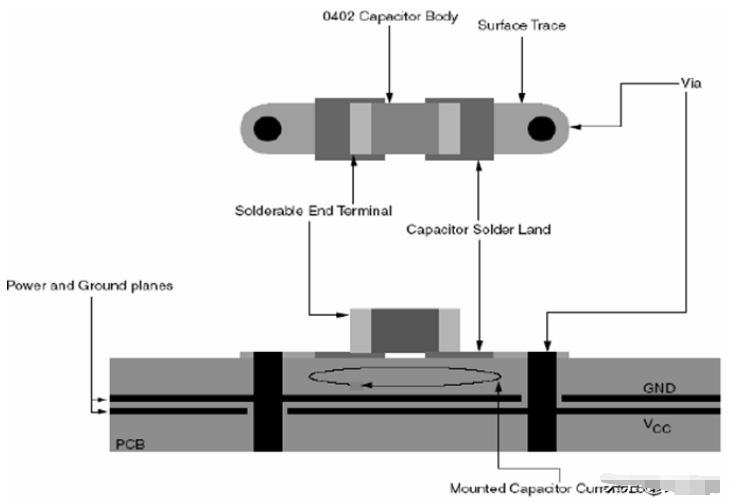

对于电容的Layout也有一些讲究,安装电容时,要从焊盘拉出一下段引线通过过孔和电源平面连接,接地段也一样。则电容的电流回路是:电源平面→过孔→引出线→焊盘→电容→焊盘→引出线→过孔→低平面。如下图所示:

放置过孔的基本原则就是让这一环路面积最小,减小寄生电感。下图显示几种安装方法:

第一种方法从焊盘引出很长的线然后连接到过孔,这会引入很大的寄生电感,一定要避免这样做。

第二种方法在焊盘二端打过孔,比第一种方法路面积小的多,寄生电感也较小,可以接受。

第三种方法在焊盘侧面打孔,进一步减小了环路面积,寄生电感比第一个更小,是比较好的方法。

第四种方法焊盘二侧面打孔,和第三种方法相比,电容的每端都是通过并联的过孔接入电源和地平面,比第三种的寄生电感还小,只要空间允许,尽量使用。

最后一种方法在焊盘上直接打孔,寄生电感最小,但是焊接可能会出现问题。

五、“滥用”磁珠的危害

典型的8层以上单板,或者6层板采用3个电源地平面,电源地相对紧耦合的设计,这时候板上的滤波电容呈现“全局特性”,也就是说电容的位置不是很“重要”,电容在全局起作用。双面板四层板,以及6层板电源地距离比较远,相对松耦合的时候,板上的滤波电容倾向于“局部特性”,电容的位置比较重要,最好能靠近芯片管脚放置。

当电源供电网络不使用电源地平面来设计的时候,电容更倾向于“局部特性”。如PLL电源的电容,如DDR3设计中Vref电源的电容,都希望严格把相应的电容靠近芯片的管脚,甚至最好能做到设计时指定电源必须从滤波电容进入芯片管脚。

同样的,对于常规数字电源,如3.3V,2.5V等IO电源,如果我们对每一个芯片都使用磁珠隔离之后单独供电,那么电容就失去了“全局”作用。最直接的一个负面作用就是导致设计需要增加更多的滤波电容。或者某个芯片的电容数量与种类不够,导致电源轨道噪声变大。

就算是电容的数量不是问题,电源噪声可控,“滥用”磁珠还会造成其他设计问题。电源种类多是设计的现状,“滥用”磁珠会“雪上加霜”的让电源种类更多。加大电源地平面设计的难度。而增加的磁珠,其实并没有给电源噪声带来好处。

六、总结

常规的数字电源,在采用多层板设计,电源地平面紧耦合的情况下,不建议“滥用”磁珠,保持电容的“全局”特性起作用。

需要使用磁珠的场合大致分为两种

1、“特别”保护自己,如PLL电源,FPGA中的SerDes模拟电源等

2、“关爱”他人,自身的干扰性比较强,避免EMI问题,如强驱动的时钟芯片等

责任编辑人:CC

-

电源

+关注

关注

185文章

18979浏览量

264489 -

磁珠

+关注

关注

6文章

280浏览量

45440

发布评论请先 登录

SI合集002|信号完整性测量应用简介,快速掌握关键点

使用MATLAB和Simulink进行信号完整性分析

Cadence工具如何解决芯粒设计中的信号完整性挑战

贴片电感磁珠的选型方法有哪些?

电源完整性分析——谨慎使用磁珠

是德DSOX1204A示波器在电源完整性测试中的关键优势

信号完整性(SI)/ 电源完整性(PI)工程师的核心技能树体系

了解信号完整性的基本原理

Samtec虎家大咖说 | 浅谈信号完整性以及电源完整性

电源完整性基础知识

各种常用电路模块设计原则:电源完整性

受控阻抗布线技术确保信号完整性

信号完整性测试基础知识

磁珠是如何影响电源的完整性

磁珠是如何影响电源的完整性

评论