在FPGA开发板上都有几种不同的存储器,比如SDRAM,FLASH,EPCS,还有内部onchip memory,这几种存储器间是如何通信或者构建一个系统该如何搭配他们呢,不少人都问到这个问题。在这里我做个总结以方便初学者的学习。

首先看看在sopc builder中reset address

该如何搭配他们呢,不少人都问到这个问题。在这里我做个总结以方便初学者的学习。

首先看看在sopc builder中reset address和nios IDE中System Library中的program memory(.text)、read-only data memory(.rodata)等这几个地址的关系和作用根据altera 的文档解释如下:

.text :代码执行区

.rodata:只读数据区,存放静态全局变量

.rwdata:可读写数据区,存放可读写变量和指针变量

.bss:未初始化变量区

.text-the actual executable code

.rodata-where read only data used in the execution of the code

.rwdata-where read/write variables and pointers are stored

heap-where dynamically allocated memory is located

stack-where function call parameters and other temporary data

SOPC builder 在Nios II more "cpu_0" setting 标签中的

reset address 决定了flash programmer 的下载存储器(一般是选EPCS controller 或者CFI

flash),并且决定了程序从此处开始启动。exception address 指定的是异常处理地址。当然,程序在运行前所有的数据都是存放在flash(EPCS 或者CFI FLASH)中如果你设计的系统resetaddress 与其它地址的设置不相同,比如reset address 和exceprion address,reset address和IDE 中的program memory(.text)设成不同的存储器,那么系统从reset address 启动时都会从flash 中把相关数据自动下载到相应的地址或者初始化相应地址。通过上面的认识,我们就比较清楚了各存储器间可进行哪些搭配了,reset address 的选择可选EPCS controllor 或者CFI flash;program memory(.text) 可选择onchipmemory,SDRAM,CFI flash 等。如果reset address 为EPCS 则在使用flash progrrammer时程序是下载到EPCS 芯片中。如果reset address 选择CFI flash,则flash progrrammer时程序是下载到CFI flash 芯片中。需要注意的是这里有个特殊情况。例如在开发板上经常有这么一个简单的系统,CPU+

onchip memory+LED_PIO,reset address 选择onchip memory;感觉整个系统都没有用到flash。而且onchip memory 在系统断电后数据就会消失,那么程序代码是存在哪,系统如何从onchip memory 启动听呢?先来看看onchip memory 模块的描述信息:在onchip_memory.v 中有这么一段the_altsyncram.init_file = "onchip_memory.hex",很明显onchip memory 的初始数据来自"onchip_memory.hex",而"onchip_memory.hex"是在NiosIDE 的System Library 中存储器有选择onchip_memory( 至少有一项是选择onchip_memory,如果都不选,就不会生成)时,在build 结束的时候生成的。于是当我们把System Library 中存储器的选择都选择onchip_memory 时,在IDE 中build 结束后所有的程序代码都生成在"onchip_memory.hex"中,再在QII 中全编译一次时,系统通过onchip_memory.v 调用"onchip_memory.hex"从而把所有的程序代码以及配制信息都生成在POF 和SOF 文件中,使用QII 的programmer 直接下载到EPCS 芯片或者FPGA 芯片内程序都会立即执行。因为这里的特殊性就有很多网友询问了,reset address 选择onchipmemory,而IDE 中把代码区都选择SDRAM 调试的时候程序正常运行,再在QII 全编译后下载POF 文件就运行不了呢?问题就是出在这了,在这里可以总结出一点,要让程序在onchip memory 之外的存储器中运行,那么reset address 就必然选EPCS 或者CFI flash,并且要通过flash programmer 把程序下载到flash 中。

责任编辑:YYX

-

FPGA

+关注

关注

1664文章

22516浏览量

639694 -

存储器

+关注

关注

39文章

7761浏览量

172289

发布评论请先 登录

Azukar-FPGA开源FPGA教育开发板介绍

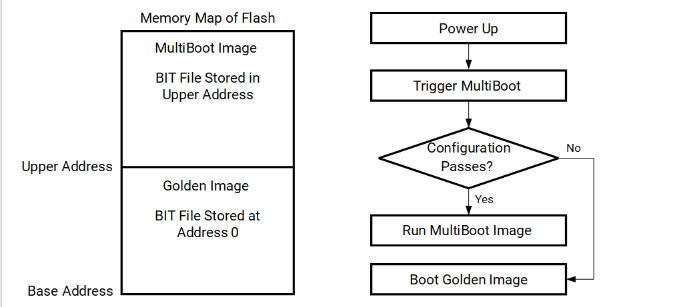

【ALINX 教程】FPGA Multiboot 功能实现——基于 ALINX Artix US+ AXAU25 开发板

【免费试用】正点原子STM32N647开发板免费试用

速通攻略 | RK3588开发板U-Boot阶段的存储设备文件读取方法

基于FPGA开发板TSP的串口通信设计

RK3506开发板Linux开发板极致性价比之选

Pico2-ICE FPGA开发板的应用示例

Vivado无法选中开发板的常见原因及解决方法

ALINX AMD RFSoC射频开发板选型指南

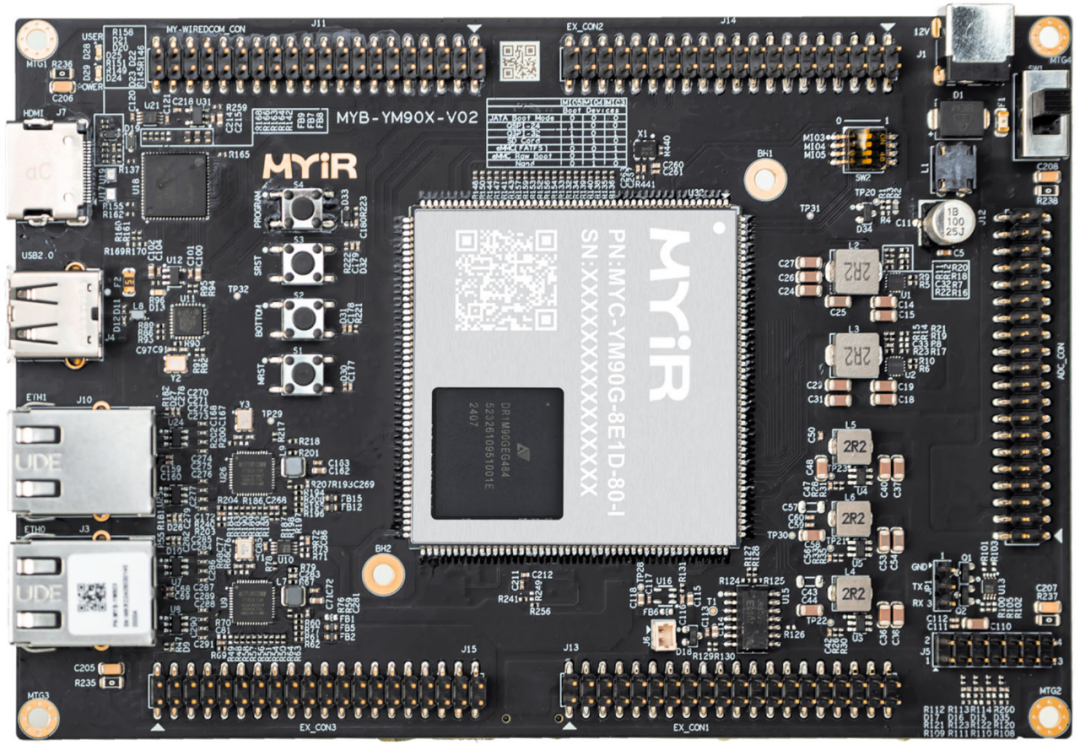

有ARM,NPU,FPGA三种核心的开发板 — 米尔安路飞龙派开发板

【新品】远距离图传数传模块开发板、蓝牙模块开发板、无线模块开发板

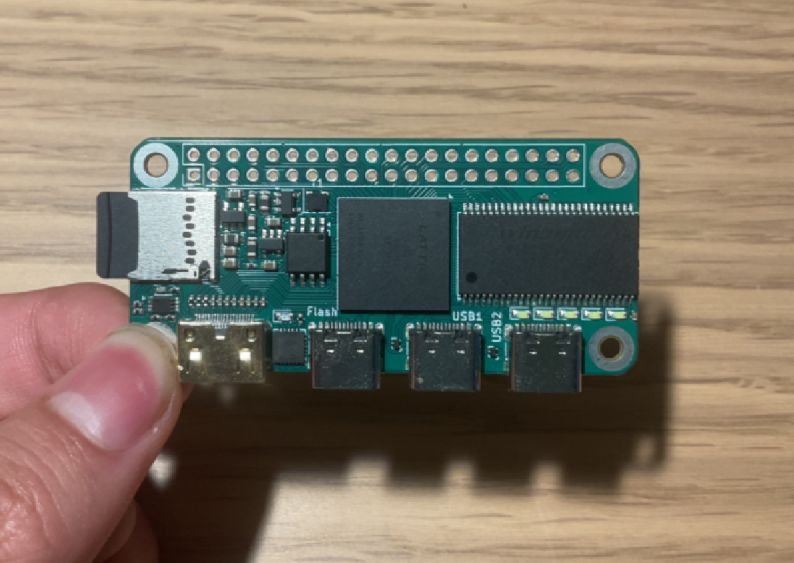

【干货分享】:开源小巧的FPGA开发板——Icepi Zero

FPGA开发板中几种不同的存储器

FPGA开发板中几种不同的存储器

评论